글/ 난딘 쉬(Nandin Xu), 제품 애플리케이션 엔지니어, 아나로그디바이스(Analog Devcies. Inc.)

이 글에서는 먼저 공통 모드 과도 내성(CMTI)의 규격과 이 규격이 시스템에서 어떠한 중요성을 갖는지에 대해 설명한다. 다음으로 새로운 절연형 시그마-델타 변조기 제품군과 성능을 소개하고, 신제품이 시스템 전류측정 정확도를 특히 오프셋 오차와 오프셋 오차 드리프트에 대해 어떻게 향상시키고 촉진하는지 알아본다. 마지막으로 권장되는 회로 솔루션을 소개한다.

.jpg)

절연형 변조기는 높은 정확도의 전류 측정 및 갈바닉 절연이 요구되는 모터/인버터에 널리 사용된다. 모터/인버터 시스템의 높은 통합 수준과 고효율 혁신으로 더 작은 크기, 더 높은 스위칭 주파수, 더 낮은 히트싱크의 이점을 제공하는 SiC 및 GaN FET가 MOSFET과 IGBT를 대체하기 시작했다.

그러나 절연형 부품에는 높은 CMTI 성능이 요구되고, 더 높은 정확도의 전류 측정도 필요하다. 차세대 절연형 변조기는 CMTI 성능을 크게 향상시키고 정확도 자체를 향상시킨다.

공통 모드 과도 내성(CMTI)이란?

공통 모드 과도 내성(CMTI)은 클럭 또는 데이터가 그 이상이 되면 손상되는 절연 경계에 걸쳐 인가되는 과도 펄스의 상승 및 하강 속도를 지정한다. 여기에는 펄스의 변화율과 절대 공통 모드 전압(VCM)이 모두 기록된다.

새로운 절연형 변조기는 정적 및 동적 CMTI 조건에서 모두 시험되었다. 정적 테스트는 디바이스에서 단일 비트 오류를 검출한다. 동적 테스트는 CMTI 펄스를 무작위로 적용하여 잡음 성능의 변화에 대해 필터링된 데이터 출력을 모니터링한다. 자세한 테스트 블록 다이어그램은 그림 1에서 볼 수 있다.

.jpg)

높은 슬루율(고주파수)의 과도 상태는 절연 장벽을 통한 데이터 전송을 손상할 수 있기 때문에 CMTI는 중요하다. 이러한 과도 상태에 대한 민감성을 이해하고 측정하는 것이 매우 중요하다. 아나로그디바이스(ADI)의 테스트 방법은 자기 커플러에 대한 CMTI 측정 방법을 포함하는 IEC 60747-17 표준을 기반으로 한다.

테스트 벤치에서 절연형 변조기의 CMTI를 특성화하는 방법

간략화한 CMTI 테스트 플랫폼은 그림 1에 보이는 다음 항목들을 포함한다.

• VDD1/VDD2를 위한 배터리 전원 공급장치

• 높은 공통 전압 펄스 발생기

• 데이터 모니터링에 사용되는 오실로스코프

• 데이터 분석에 사용되는 데이터 수집 플랫폼과, 절연형 변조기에 사용되는 256 데시메이션 sinc3 필터

• 절연형 모듈(일반적으로 광학 절연 사용)

• 절연형 변조기

정적 및 동적 CMTI 테스트에는 동일한 플랫폼이 사용되며, 입력 신호만 다르다. 이 플랫폼은 다른 절연형 제품의 CMTI 성능을 테스트하는 데에도 사용할 수 있다. 절연형 변조기의 경우 1비트 스트림 데이터를 데시메이션하고 필터링한 다음, 모터 제어 시스템의 제어 루프로 전송하므로 동적 CMTI 테스트 성능이 더 포괄적이고 유용하다. 그림 2와 그림 3은 다양한 CMTI 레벨에서 시간 및 주파수 영역 CMTI 동적 테스트 성능을 보여준다.

.jpg)

.jpg)

그림 2에서 동일한 절연형 변조기에 더 높은 VCM 과도 신호를 추가할 때 스퍼(spur)가 커지는 것을 볼 수 있다. VCM 과도 신호가 절연형 변조기 규격을 초과하면, 매우 큰 스퍼가 시간 영역에서 나타난다(그림 2c 참조). 모터 제어 시스템에 사용할 경우, 이는 심각한 영향을 미쳐 커다란 토크 리플을 발생한다.

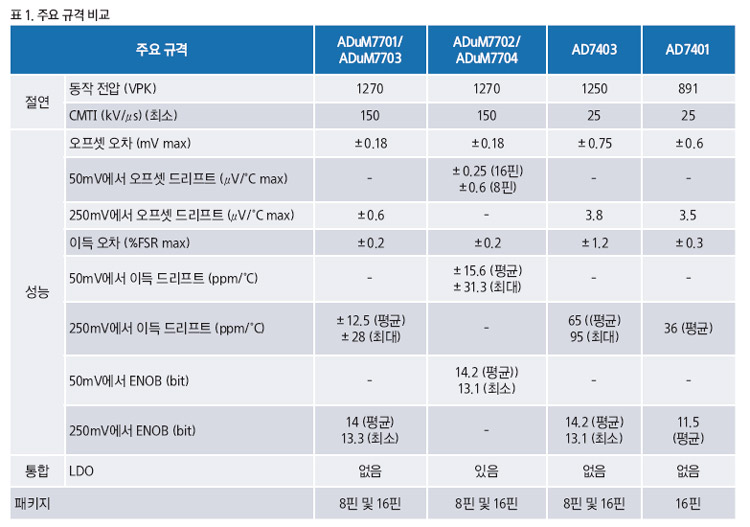

그림 3은 다양한 주파수 과도 상태에서 FFT 영역 성능을 보여준다(과도 상태의 시간을 변경하여 VCM 과도 상태 레벨을 유지함을 의미). 그림 3의 결과는 고조파가 과도 주파수와 매우 관련이 높다는 것을 보여준다. 따라서 절연형 변조기의 CMTI 성능이 높을수록 FFT 분석에서 잡음 수준은 더 낮아진다. 이전 세대 절연형 변조기와 비교할 때, 차세대 ADuM770x 디바이스는 CMTI 성능이 25kV/μs에서 150kV/μs로 증가하여 시스템 과도 상태 내성이 크게 향상되었다. 자세한 내용은 표 1의 비교 데이터에서 확인할 수 있다.

시스템 수준 보상과 보정 기법

모터 제어 또는 인버터 시스템에서 전류 데이터의 정확도가 높을수록 시스템은 더 안정적이고 효율적이다. 오프셋 및 이득 오차는 ADC에서 DC 오차의 공통된 원인이다. 그림 4는 오프셋 및 이득 오차가 ADC 전달 함수에 미치는 영향을 보여준다. 이러한 오차는 토크 리플 또는 속도 리플로 시스템에 영향을 미친다. 대부분의 시스템에서 오차 영향을 제한하기 위해 이들 오차를 주변 온도에서 보정할 수 있다.

한편, 전체 온도 범위에 걸친 오프셋 드리프트와 이득 오차는 문제가 된다. 보상하기가 더 어렵기 때문이다.

시스템 온도를 알고 있다면, 프로파일에 보상 계수를 추가하여 오프셋 드리프트 프로파일을 최대한 평탄하게 만듦으로써(비용과 시간이 많이 소모되긴 하지만) 선형 및 예측 가능한 드리프트 프로파일을 갖는 컨버터에 대해 오프셋 및 이득 오차 드리프트의 보상을 달성할 수 있다. 자세한 보상 방법은 애플리케이션 노트 AN-1377에 설명되어 있다.

.jpg)

이 방법은 AD7403/AD7405 데이터 시트에 지정된 드리프트 수치를 오프셋 드리프트의 경우 최대 30%, 이득 오차 드리프트는 최대 90%까지 줄일 수 있으며, 시스템 수준에서 오프셋 및 이득 오차 드리프트를 향상시키고자 하는 경우 다른 모든 컨버터 부품에 적용할 수 있다.

초핑 기법의 활용

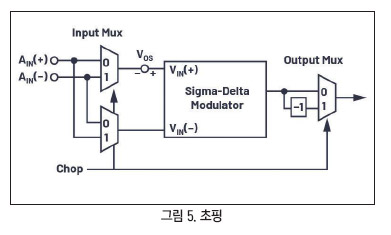

다른 방법으로, 초핑 기법이라고 하는 설계를 사용할 수 있다. 이 설계는 시스템 설계자가 사용하기에 더 효율적이고 편리하며, 또한 초핑 기능을 실리콘 자체에 통합함으로써 오프셋 및 이득 오차 드리프트를 최소화할 수도 있다. 초핑 방식은 그림 5에 나와 있으며, 여기에서 ADC에 구현된 솔루션은 전체 아날로그 신호 체인을 초핑하여 모든 오프셋 및 저주파수 오차를 제거한다.

변조기의 차동 입력은 입력 멀티플렉서에서 교대로 반전되고(또는 초핑되고), 초프의 각 단계에서 ADC 변환이 수행된다(먹스를 “0” 또는 “1” 상태로 전환). 변조기 초핑은 출력 신호를 디지털 필터에 전달하기 전에 출력 멀티플렉서에서 반전된다.

시그마-델타 변조기의 오프셋을 VOS로 나타내는 경우, 초프가 0일 때 출력은 {AIN(+) - AIN(-)} + VOS이고, 초프가 1일 때 출력은 –[{(AIN(-) - AIN(+)} + VOS]이다. 디지털 필터에서 이 두 결과를 평균하면 {AIN(+) - AIN(-)}가 되므로 오차 전압 VOS가 제거된다.

이는 오프셋 항이 없는 차동 입력 전압과 같다.

최신 절연형 변조기는 내부 아날로그 설계를 최적화하고 최신 초핑 기법을 사용하여 오프셋 및 이득 오차 관련 성능을 향상시킴으로써 시스템 설계를 매우 간소화하고 보정 시간을 줄여준다. 최신 ADuM770x 디바이스는 최고의 절연형 수준과 최상의 ADC 성능을 제공한다. 시스템의 전원 공급장치 설계를 간소화할 수 있는 LDO 버전도 사용할 수 있다.

권장되는 회로 및 레이아웃 설계

모터 시스템의 일반적인 전류 측정 회로는 그림 6에 나와 있다. 시스템에 필요한 위상 전류 측정 회로는 세 개지만, 블록 다이어그램에는 하나만 표시된다. 다른 두 개의 위상 전류 측정 회로도 이와 유사하며, 파란색 점선으로 표시된다. 위상 전류 측정 회로에서 RSHUNT 저항의 한쪽이 ADuM770x-8의 입력에 연결된 것을 볼 수 있다.

.jpg)

다른 쪽은 고전압 FET(IGBT 또는 MOSFET일 수 있음) 및 모터에 연결된다. 고전압 FET가 상태를 변경하면 과전압, 저전압 또는 기타 전압 불안정 상태가 항상 발생한다. 이에 따라 RSHUNT 저항의 전압 변동이 ADuM770x-8로 전달되고, 관련 데이터가 DATA 핀에서 수신된다. 레이아웃 및 시스템 절연 설계는 전압 불안정 상태를 향상 또는 저하할 수 있으며, 이는 위상 전류 측정 정확도에 영향을 미친다.

권장되는 회로 구성은 다음과 같다(그림 6 참조).

• VDD1/VDD2 디커플링의 경우, 10μF/100nF 커패시터가 필요하며 해당 핀에 가능한 가깝게 배치해야 한다.

• 10Ω/220pF RC 필터가 필요하다.

• 션트의 잡음 효과를 줄이기 위해 옵션인 차동 커패시터가 권장된다. 커패시터를 IN+/IN- 핀에 가깝게 배치한다(0603 패키지 권장).

• 디지털 출력 라인이 긴 경우, 82Ω/33pF RC 필터가 권장된다. 우수한 성능을 위해 차폐트위스트 페어 케이블을 고려한다.

• 고성능 요구사항의 경우, 4단자 션트 저항의 사용을 고려한다.

최고의 성능을 달성하려면 레이아웃 역시 우수해야 한다. 권장되는 레이아웃은 그림 7에 나와 있다. 공통 모드 제거기능을 향상하려면 션트 저항에서 IN+/IN- 입력 핀까지 차동 쌍 배선이 권장된다. 10Ω/220pF 필터는 IN+/IN- 입력핀에 최대한 가깝게 배치한다.

.jpg)

10μF/100nF 디커플링 커패시터는 VDD1/VDD2 전원 공급장치 핀에 가깝게 놓아야 한다. 신호 안정성을 높이기 위해서는 부분 접지면 GND1을 입력 관련 회로 아래에 배치하는 것이 좋다. 전원 공급장치의 전류 변동 영향을 줄이려면 독립 GND1 라인(보라색으로 표시되고, 차동 쌍 배선 라인과 병렬로 있는)과 션트 저항에서 ADuM770x-8 GND 핀까지 스타형 연결이 필요하다.

결론

최신 ADuM770x 절연형 시그마-델타 변조기는 CMTI를 150kV/μs 수준으로 증가시키고 온도 드리프트 성능을 향상시켜 전류 측정 애플리케이션에 많은 이점을 제공한다. 권장 회로와 레이아웃은 설계 단계에서 유용하게 사용할 수 있다.

참고문헌

ADuM7704 data sheet. Analog Devices, Inc., August 2020.

Heo, Hong-Jun; Seon-Ik Hwang; Jang-Mok Kim; and Jin-Woo

Choi. “Compensating of Common Scaling Current-Measurement

Error for Permanent Magnet Synchronous Motor Drives.” 2016 IEEE

8th International Power Electronics and Motion Control Conference

(IPEMC-ECCE Asia), May 2016.

McCarthy, Mary. “AN-1131: Chopping on the AD7190, AD7192,

AD7193, AD7194, and AD7195.” Analog Devices, Inc., October 2011.

Merino, Miguel Usach and Gerard Mora Puchalt. “Integrated

Capacitive PGAs in ADCs: Redefining Performance.” Analog Dialogue,

Vol. 50, No. 3, August 2016.

O’Byrne, Nicola. “MS-2652: Measurement Techniques for Industrial

Motion Control.” Analog Devices, Inc., June 2014.

저자 소개

난딘 쉬(Nandin Xu)는 중국 상하이 소재 아나로그디바이스(ADI)의 제품 애플리케이션 엔지니어이다. 중국 전역에 걸쳐 RDC, 절연형 변조기, 정밀 ADC/DAC 제품에 대한 기술 지원을 담당하고 있다. 중국 우한 화중과학기술대학에서 제어과학 및 관제기술 석사 학위를 받고 2013년에 ADI에 입사했다. 여가 시간에는 농구와 축구를 즐긴다. 문의: nandin.xu@analog.com.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>