지난 달 10일, 자일링스는 20 nm 공정 기술을 이용해 FPGA 개발을 완료(tape-out)했다고 발표했다. 동시에, 20 nm 공정의 FPGA에 적용할 차세대 아키텍처 “UltraScale”을 공개했다. 새로운 공정, 새로운 아키텍처를 도입한 제품은 올 4사분기에 출시될 예정이다.

자일링스가 20 nm 공정을 적용한 FPGA의 테이프 아웃과 함께 ASIC급 프로그래머블 아키텍처인 울트라스케일(UltraScale)™을 발표했다.

자일링스가 20 nm 공정을 적용한 FPGA의 테이프 아웃과 함께 ASIC급 프로그래머블 아키텍처인 울트라스케일(UltraScale)™을 발표했다.

자일링스 전 세계 품질 및 신제품 출시 담당 수석부사장 빈센트 통(Vincent Tong) 씨는 “20 nm 공정을 이용한 반도체 디바이스의 테이프 아웃은 업계 최초이며 경쟁사보다 하이엔드 디바이스에서 1년 이상 앞서 있다”고 주장했다.

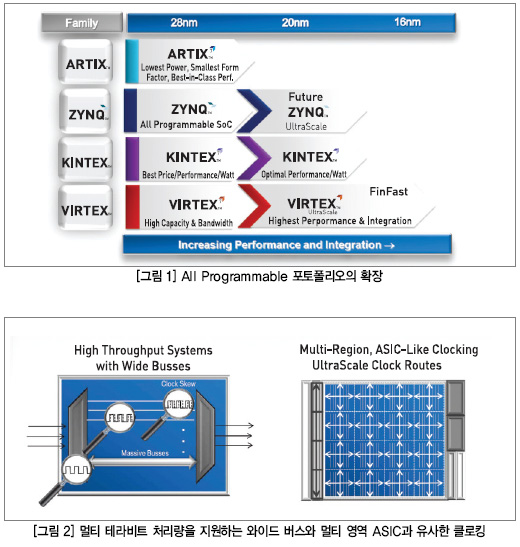

20 nm 공정의 FPGA가 기존 FPGA와 다른 점은 그 명칭에서 눈에 뛴다. 지금까지 자일링스는 FPGA 제품에 새로운 반도체 제조 공정을 도입할 때마다 숫자로 세대를 구분하고 아키텍처를 쇄신해 왔다. 즉, 40~45 nm 공정의 FPGA는 ‘6 시리즈’로, 28 nm 공정을 채용한 FPGA는 ‘7 시리즈’로 이름을 붙였다. 그러나 20 nm 세대는 ‘8 시리즈’라는 명칭을 사용하지 않았다. 자일링스가 아키텍처 명칭과 공정 세대를 분리시키는 새로운 개념을 도입한 것이다.

이번에 발표한 울트라스케일 아키텍처는 20 nm 세대뿐만 아니라, 28 nm 세대와 16 nm 세대를 커버한다. 이번에 울트라스케일 아키텍처를 도입한 제품은 20 nm 세대 제품으로 미들엔드급인 “킨텍스(Kintex) 울트라스케일”과 하이엔드급인 “버텍스(Virtex) 울트라스케일”이다. 향후에는 올 프로그래머블(all programmable) SoC인 “징크(ZynQ)”에도 울트라스케일 아키텍처를 적용한 제품을 추가할 계획이다. 또한 올해 말 테스트 칩을 내놓고 2014년에 첫 제품을 출시할 계획인 16 nm 세대 제품도 20 nm 세대와 동일한 울트라스케일 아키텍처를 채택할 예정이다.

빈센트 통 수석부사장에 따르면, 저가형 Artix 제품군은 28 nm 공정에서 더 이상 미세 공정을 적용하지 않을 계획이며 울트라스케일 아키텍처를 적용하는 것에 대해서도 현재 고려하고 있지 않다.

ASIC급 프로그래머블 아키텍처 “울트라스케일”

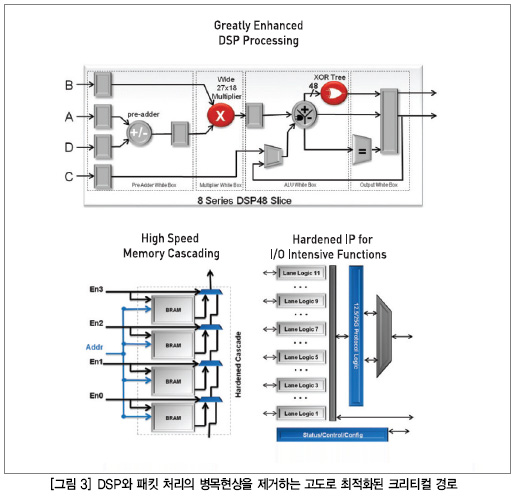

울트라스케일 아키텍처는 20 nm 플래너(planar)에서 16 nm FinFET까지, 모놀리식에서 3D IC까지 확장되도록 개발되었다. 이 아키텍처는 총 시스템 스루풋(throughput)과 레이턴시의 확장에 가해지는 한계를 처리할 뿐만 아니라, 고급 노드에서의 칩 성능, 인터커넥트에서 가장 큰 문제인 병목현상을 처리한다.

이에 관련해 빈센트 통 수석부사장은 “IP 트래픽의 병목현상을 처리하기 위해 레이어를 하나 더 올려 직접 라우팅이 가능하도록 ASIC 방식의 인터커넥트를 구현했으며, 클록 스큐 문제는 ASIC처럼 클록 소스를 다이에 분산 배치하는 방법으로 해소하고 클록 속도를 높였다”고 설명했다.

DSP와 패킷 처리를 가속화시키는 기술도 도입했다. DSP의 경우, wider multiplier를 통해 단일-정밀도 부동소수점 및 이중-정밀도 부동소수점 연산이 가능하게 했다. 또한 고속 메모리 캐스케이딩 기술에 의해 DSP와 패킷 처리의 병목현상을 해소했다. 이밖에도 10/100G 이더넷 및 PCI Express 등을 하드 IP화해 I/O 기능도 강화했다.

소비 전력의 절감을 위해서는 1.2 V 동작의 DDR4 메모리를 지원하는 등 하드웨어적인 방법과 함께 개발환경인 비바도(Vivado) 디자인 수트의 소비전력 최적화 설계 기능을 강화했다.

자일링스의 첫 20 nm FPGA 제품은 28 nm 세대에 이어 TSMC의 20SoC 개발 공정을 이용한다. 빈센트 통 수석부사장에 따르면, 이 공정을 도입함으로써 28 nm 세대에 비해 최대 35%의 정적 전력(static power)을 줄일 수 있다.

그는 “20 nm 공정 울트라스케일을 적용해 시스템 수준 성능을 기존 대비 1.5배에서 2배까지 높일 수 있다”고 밝혔다.

울트라스케일 아키텍처 기반 FPGA는 새로운 고성능 아키텍처 요건으로 다음과 같은 차세대 스마터 시스템을 가능하게 해준다.

- 400G OTN과 지능형 패킷 프로세싱, 트래픽 관리

- 4×4 복합 모드(Mixed Mode) LTE 및 스마트 빔포밍(beamforming) WCDMA 무선

- 스마트 이미지 강화 및 인식 4K2K 및 8K 디스플레이

- ISR(intelligence surveillance and reconnaissance)을 위한 고성능의 시스템

- 데이터 센터를 위한 고성능 컴퓨팅 애플리케이션

울트라스케일 기반 FPGA를 지원하는 비바도 디자인 수트의 얼리 액세스는 현재 이용 가능하며, 초기 울트라스케일 디바이스는 올 4사분기에 선보일 예정이다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>