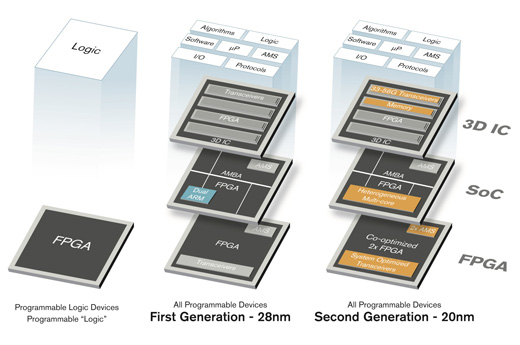

자일링스는 차세대 8 시리즈 올 프로그래머블 FPGA와 제2세대 3D IC 및 SoC를 포함한 20나노 포트폴리오 전략을 발표했다. 20나노 포트폴리오는 이미 28나노에서 입증된 차세대 기술을 바탕으로 제작되어, 최상의 시스템 성능과 저전력 소모, 프로그래머블 시스템 통합을 제공한다. 자일링스의 비바도™ 디자인 수트와 함께 최적화된 20나노 포트폴리오는 최고의 생산성과 품질을 자랑하며, 다양한 차세대 시스템에 활용이 가능하며 ASIC 및 ASSP에 가장 강력한 대안을 제공한다.

자일링스 사장 및 CEO 인 모쉬 가브리엘로브는 “20나노 포트폴리오는 기하급수적으로 성장하고 있는 프로그래머블(programmable imperative) 수요 문제를 해결해 줄 것이다. 막대한 디자인 비용뿐만 아니라 최대 적응성, 재사용, 시스템 통합과 함께 모든 시스템에서 보다 많은 지능(intelligent)이 지속적으로 투입되어야 할 필요성으로 인해 프로그래머블 수요는 점점 늘어가고 있다."라고 말했다.

자일링스는 보다 ‘스마트’한 고집적 광대역 시스템 요구조건을 해결하기 위해 20나노 올 프로그래머블 포트폴리오 최적화에 주력하고 있다. 이러한 애플리케이션은 다음을 포함한다.

- 지능형 Nx100G ~ 400G 유선 네트워크

- 스마트 기술, 적응형 안테나(adaptive antenna), 인지 무선 기술, 대역 및 백홀(backhaul) 장비를 이용한 LTE™ 첨단 무선 기지국

- 고출력, 저전력 데이터 센터 솔리드 스테이트(solid state) 스토리지, 지능형 네트워크, 고집적 저지연 애플리케이션의 가속화

- 차세대 디스플레이, 전문가용 카메라, 공장 자동화, 최신 자동차 운전자 보조장치, 감시 카메라용 이미지/비디오 프로세싱

- 거의 모든 애플리케이션을 위한 최첨단 커넥티비티

자일링스 프로그래머블 플랫폼 그룹 부사장 빅터 펭은 "자일링스는 기존의 경쟁 제품보다 한 세대 앞선 기술인 최신20나노 포트폴리오 발표와 함께, 28나노 분야에서 실질적인 기술 개발로 시장을 주도하고 있다. 또한 ASIC 및 ASSP보다 훨씬 많은 장점을 제공한다."고 밝혔다.

자일링스는 다양한 분야에서 경쟁사보다 최소 수년 앞선 기술적 우위를 점하고 있다. 이미 수백만 고객을 보유하고 있는 초정밀 리얼 SoC 및 3D IC, 새로운 에코시스템, 공급망, 고품질 및 신뢰성을 위한 프로세스, 차세대 비바도 디자인 수트 툴과 최적화된 디바이스 개발, 고성능 트랜스시버를 시스템에 통합하는 방법 개선 등 광범위한 분야에서 자일링스의 실적은 두드러진다. 28나노에서 입증된 자일링스의 선도적인 기술과 20나노 미세공정 가치의 융합으로 자일링스는 고객이 시장에서 앞서 나갈 수 있도록 지원한다.

차세대 올 프로그래머블 FPGA

20나노 8 시리즈 올 프로그래머블 FPGA는 기존 제품보다 2배 빠른 성능과 1.5~2배 확장된 통합 기능을 자랑하는 반면 전력은 절반만 소모한다. Nx100G 유선 네트워크, LTE A 무선 네트워크를 위한 무선 L1 베이스밴드 코프로세싱, 차세대 시스템 가속화 및 커넥티비티와 같은 차세대 애플리케이션에 적합하다. 주요 개선 사항은 다음과 같다:

- 구조 개선을 통해 자원 활용률 90% 이상 달성, 4배 더 빠른 디자인 클로져(design closure)를 제공하는 라우터빌리티(routability)에 최적화된 알고리즘

- 차세대 어댑티브 이퀄라이제이션(adaptive equalization), 낮은 지터, 최저전력 소모, 시스템 최적화 및 고속 트랜스시버

- 디지털 신호 처리 및 온칩 메모리 성능을 대폭 개선해 메모리 대역 2배 확장

2세대 올 프로그래머블 3D IC

자일링스의 제2세대 3D IC는 동종 및 이종 구성을 갖추게 된다. 고성장 애플리케이션에는 Nx100G/400G 스마트 네트워크, ToR(top-of-rack) 데이터 센터 스위치, 고집적 ASIC 프로토타이핑(prototyping)이 포함된다. 주요 개선 사항은 다음과 같다:

- 산업 표준 인터페이스를 반영한 2단계 3D 연결 및 5배 빨라진 다이 투 다이(die-to-die) 대역

- 로직 정전 용량 최소 1.5~ 2배 확장, 트랜스시버 대역 4배 확장, 인터라켄(Interlaken) 커넥티비티 통합 광대역 메모리, 트래픽 관리, 패킷 프로세싱 IP

- 최적화된 디자인 툴로 2배 향상된 통합 수준 및 내/외부 라우팅 용량, 자동 디자인 클로져 및 확장 가능한 알고리즘

2세대 올 프로그래머블 SoC

자일링스의 20나노 올 프로그래머블 SoC는 주요 프로세싱 기능을 가속화하기 위해 FPGA 패브릭과 이종 프로세싱 코어를 통합한다. 고성장 애플리케이션에는 이종 무선 네트워크 무선, 베이스밴드 가속화 및 백홀, 데이터센터 보안 기기, 오토모티브, 산업, 과학, 의료, 항공우주 및 방위 시장에서의 임베디드 비전 애플리케이션이 포함된다. 주요 개선 사항은 다음과 같다:

- 프로세싱 시스템과 FPGA 패브릭 간의 대역 개선으로 주요 프로세싱 기능 가속화

- 차세대 I/O, 트랜스시버 및 DDR 메모리 인터페이스 기능

- 최신 SoC 수준 전원 관리 및 차세대 블록 레벨 전력 최적화

- ARM® 테크콘® 2012 컨퍼런스에서 발표한 개선사항을 기초로 한 차세대 보안

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>