이 글에서는 보드 설계자들이 학교로 다시 돌아가 새롭게 배울 필요 없이 원하는 클록 결과를 얻을 수 있는 방법에 대한 디지털 전문 지식을 주로 지원하기 위해 IDT®(Integrated Device Technology®) 같은 기업들이 제공하는 몇 가지 툴에 대해 다룬다.

글 | 이안 돕슨 (Ian Dobson), 시스템 아키텍처 디렉터

TSD(Timing & Synchronization Division) 사업부

IDT (Integrated Device Technology)

통신 시스템이나 하이엔드 서버용 보드 설계 작업은 언제나 계층적 접근법에 따라 진행된다. 이를 테면 CPU, 프레이머(framer), NPU, FPGA, 프로토콜 스위치처럼 빌딩 블록이 큰 칩을 먼저 선택한 다음에 I/O 디바이스, 글루 로직(종종 FPFA에 삽입)을 선택한 뒤, 마지막으로 클러킹과 전력 공급 장치를 선택하는 식이다. 보드 설계자의 기본적인 전문 지식은 주요 빌딩 블록을 선택하고 조합하는 보드 아키텍처에 집중된다.

그러나 광전송망(optical transport network, OTN) 같은 초고속 멀티 프로토콜 I/O 인터페이스가 등장하면서 클록 트리 설계는 순식간에 놀라울 정도로 복잡해졌다. 어떤 순간에 회선상에서 실행중인 프로토콜이 무엇이냐에 따라, 복호화에는 서로 다른 클록 주파수가 요구될 수 있다. 많은 경우 클록 주파수는 I/O 인터페이스상에서 데이터의 언더런(under run) 또는 오버런(over-run)을 막기 위해 역동적으로 변화시킬 필요가 있다.

그뿐 아니라 I/O 인터페이스의 성능과 속도는 그러한 클록으로부터 극도로 빠듯한 주파수 도메인 성능을 요구한다. 그렇다면 디지털 보드 설계자는 푸리에(Fourier) 변환, 보드 플롯(Bode plot) 및 기타 아날로그 설계 툴사용법을 다시 배워야 하는 것인가? 다행히 그럴 필요가 없다!

보드 설계자가 된다는 것은 무척이나 고된 일이다(그 때문에 필자는 기회가 생겼을 때 즉시 관리직으로 전환했다). 전체 회로도를 생성하고 그것을 구현하는데 필요한 업무를 수행하기 위해서는 상충하는 여러 가지 요건들 사이에서 적절한 균형을 찾을 필요가 있다.

- 마케팅 팀은 케이프 케네디에 위치한 차량 조립 건물 내부를 꽉 채울 정도로 많은 기능을 요구하는데, 기계적 설계팀은 회사 로고 뒤, 성냥갑 크기의 작은 구멍만한 면적을 당신의 보드에 할당했다.

- 최고기술책임자(CTO)는 지난 주 SF영화에서 본 기술을 제안하는데, 구매팀은 약 75%가 진공관인 “승인된 부품 목록”에 이미 올라와 있는 부품만 사용할 수 있다고 주장한다.

- 소프트웨어 팀은 프로세서에 자신의 코드를 이식해야 할지도 모르기 때문에, 새 프로세서는 고려하지 않겠다고 거절한다. 그러나 최근 설계에 쓰겠다고 소프트웨어 팀에서 제출한 8배속 RAM 신청서를 보면, 이 모든 것이 일어났을 때 성능 문제가 생길 것이라는 확신이 든다.

- 파워팀에서는 당신에게 추가로 200 W를 주었지만 오직 120 VAC로만 주어서 이 전압을 필요한 전압 수치로 변환하려면 파워팀이 아닌, 당신의 열처리 예산을 줄여야 할 것이다.

- 열처리 예산에 대해서 지난 번 설계보다 20% 줄여달라는 요구를 받았는데 ,환기된 공기가 보드에 도달할 쯤에는 이미 온도가 75 ℃가 되어 있을 것이다.

모든 사람이 마침내 동의한 PHY 칩데이터시트를 살펴 기준 클록 명세를 정의한 3페이지의 표를 확인하는 것은 어쩌면 가장 쓸 데 없는 일일 수 있다. 기준 클록 명세에는 주파수가 포함되어야 하고 듀티 사이클(duty cycle)이 포함되어야 할 수도 있다. 그러나 그게 전부다. 그 편이 더 나을 수도 있다. 당신의 상사는 최종 회로도 검토를 하기 이틀 전에야 전체 클록 트리를 선택하고 추가하라고 허락해주기 때문이다.

대부분의 보드 설계자들이 알고 있듯이 클록 부품 선택은 더 이상 단순하지 않다. 좋은 소식은 타이밍 부품을 설계하고 공급하는 주요 기업들이 고객이 직면한 이러한 문제를 인식하고 아날로그 설계 관련 박사학위가 없는 사람도 손쉽게 클록 트리를 완성할 수 있게 해주는 툴을 제공하고 있다는 것이다.

클러킹 부품을 선택하고 설계할 때 해결해야 하는 몇 가지 문제점을 살펴보고 각각의 작업을 끝내기 위해 어떤 도움을 얻을 수 있는지 알아보자.

보드 설계 흐름 내에서 클러킹은 아키텍처 구성 요소의 요건을 만족시키기 위한 서비스 기능을 제공해야 한다. 그러한 아키텍처 구성 요소를 선택해야 비로소 클록 명세의 전체 목록이 결정된다. 일부 복잡한 통신 시스템은 네트워크 동기화 같은 타이밍 기능을 아키텍처 구성 단계에서 처리한다는 점을 주목할 필요가 있다. 일단 아키텍처 구성 요소를 선택하고 나면 보드 설계자는 전력, 면적, 기류 요건을 고려해야 한다. 그 후 커넥터, 면판(faceplate) 스위치, LED 등 설치할 위치가 중요한 부품이 추가된다. 그리고 나면 글루 로직, 전력 공급 및 클러킹 같은 서비스 구성 요소에 할당할 보드의 면적이나 전력, 비용 예산이 거의 남지 않는 경우가 허다하다.

■ 보드 면적

단순하다면 모든 경우에 프로토콜, 전압, 성능 명세에 따라 각각에 필요한 다양한 클록을 사용한다. 클록 트리에서는 각각 필요한 기능이 간단히 설명될 수 있고 디스크리트 소자로 사용할 수 있는 경우가 많은 반면, 각각에 대해 개별 디바이스를 사용함으로써 발생하는 비용, 면적, 전력의 불이익은 감수해야 한다. 그러한 이유로 타이밍 부품 제조사들은 여러 기능을 하나로 통합한 부품을 개발해왔다. 이는 최적의 보드 설계를 돕기 위한 의도였으나, 어떠한 부품들의 조합이 설계자가 원하는 요구 명세에 최적화된 기능을 제공하는지 알기 어렵다는 문제점을 낳았다. 또한 비용, 면적, 전력, 성능 간에 무엇을 우선할 지는 설계마다 달라질 수 있다.

타이밍 부품 제조사는 최적의 솔루션을 찾기 위해 방대한 부품 카탈로그가 도움이 되기도 하지만, 이것이 혼란을 가중시키는 원인이 된다는 점도 인식하고 있다. 따라서 대부분의 부품 제조사들은 클록 트리 구축 툴을 제공하거나 제품을 숙지한 애플리케이션 엔지니어로 하여금 각각의 설계 요건에 맞춘 솔루션을 제시하는 신속 서비스를 제공한다. 필요한 부품을 모두 제공할 수 있는 타이밍 부품 공급사와 협력하면 디지털 보드 설계자가 몇몇 불완전하고 가끔은 호환이 안 되는 솔루션들을 끼워 맞춰야 할 필요가 줄어든다.

■ 시간 도메인 지터 한계

시간 도메인 지터는 클록 에지 위치의 부정확성을 뜻하는 용어로 클록의 주기적인 오실로스코프 뷰(view)에서 확인할 수 있다. 사이클 간 지터(Cycle-

to-cycle jitter)는 단시간 뷰로, 하나의 클록 에지 다음에 다음 클록 에지를 보여준다. 사이클 간 지터는 디지털 로직 애플리케이션에 중요한데, 클록 펄스가 너무 짧으면 셋업 홀드 시간 위반을 일으킬 수 있기 때문이다. 주기 지터(period jitter)는 장기간 뷰로, 데이터 복구 애플리케이션에 중요한데, 과다한 주기 지터는 오실로스코프 아이 다이어그램에서 소위 ‘눈(eye)’을 닫아버려 비트 에러율이 높아지기 때문이다. 둘 다 목표 수치를 타이밍 부품의 데이터시트와 간단히 비교하는 것만으로 해결된다. 적합한 부품은 타이밍 부품 제조사의 홈페이지에서 쓸만한 파라메트릭 서치(parametric search) 툴을 사용해 즉시 선택할 수 있다.

■ 전력 소비

이전부터 타이밍 부품은 단일 전원 레일과 몇 가지 프로그램 가능한 기능을 포함한 단순한 디바이스였다. 이 때문에 데이터시트에는 전력 소비나 전류 수치 하나밖에 표시하지 않았고 단순 비교도 쉬웠다. 더욱이 전력 소비는 통풍장치나 히트싱크가 없는 디바이스 패키지가 소비하는 전력보다 훨씬 낮은 것이 보통이어서 그러한 특정 칩에 대한 열 계산이 필요하지 않았다.

하지만 불행히도, 낮은 위상 잡음 목표를 달성하기 위해 성능을 통합하고 전력 소비를 증가시키자, 전력 소비를 확인하고 열 관련 문제를 분석해야 해서 단순한 계산이 복잡해지고 애플리케이션마다 따로 적용해야 하는 것으로 바뀌어 버렸다. 최근에 나온 여러 타이밍 부품은 높은 수준의 유연성과 사용하지 않는 기능에 대해 전력을 낮추는 기능을 제공한다. 또한 애플리케이션 환경에 적합한 전압 레일에서 개별 회로에 전력을 공급하는 기능도 제공한다.

디바이스 컨피규레이터 툴은 이에 대한 솔루션이 될 수 있다. 그러한 툴은 보드 설계자들이 타이밍 디바이스에 대한 설정을 결정하도록 도와줄 뿐 아니라 타이밍 디바이스가 제대로 구축되면 설계자는 특정 보드와 사용처에 유효한 전력 소비와 접합 온도(junction temperature)를 얻을 수 있게 된다.

■ 주파수 확산

얼마 전까지만 해도 특정 시장 부문에서 일하는 보드 설계자는 5~6가지 주파수를 제공하는 것만 신경 쓰면 충분했으며, 일단 보드에 전원이 들어오면 주파수는 고정되었다. 예를 들어 이더넷 라우터의 경우, 플러그형 옵틱 모듈의 설치 여부에 따라 회선 접속을 위해 25 MHz, 125 MHz, 156.25 MHz의 주파수 중 하나를 제공할 수 있다. 오늘날 단일 시장 공간을 위해 설계된 기능이 다른 시장으로 빠르게 확산되면서 이제는 이더넷 라우터에 유지관리용으로 USB 3.0 포트와 SD카드 슬롯을 사용하는 경우가 있고, 40 MHz와 12 MHz 클록이 필요해졌다. 이더넷 라우터에 광통신 전송망과 호환 가능한 업링크 포트도 지원하면 소프트웨어 설정을 통해 변경할 수 있는 30~40개의 여러 클록 주파수가 필요할 수 있다. 이 때문에 더 많은 주파수가 필요한 것은 물론, 그러한 주파수들이 더 이상 단순한 정수비로 연관되지 않게 되었다.

이러한 문제들은 단일 기기에서 더 높은 유연성과 여러 PLL을 제공하는 타이밍 부품을 사용함으로써 해결할 수 있다. 그러나 유연성이 늘어나면 프로그램 복잡성도 늘어나는 경향이 있다. 이러한 새로운 부품들은 IDT의 타이밍 커맨더(Timing Commander™) 같은 컨피규레이터 툴을 사용해 복잡한 디바이스를 간단히 설정할 필요가 있다. 원하는 입출력 주파수를 입력하면 툴이 모든 레지스터를 프로그램하는 방법을 산출해낸다. 컨피규레이터 툴은 각각의 주파수 계획에 따른 운용 소프트웨어를 위한 단순한 출력 파일도 제공하고 부품 내에 영구적으로 내장되는 경우도 있다.

■ 주파수 도메인 지터 명세

주파수 도메인 지터는 모든 실제 클록 신호에 존재하는 뜻밖의, 일반적으로 원치 않는 별도 주파수를 뜻한다. 이는 바람직한 주파수(반송파)의 에너지 대 해당 반송파의 주파수를 상쇄하는 에너지와 비례해 1 Hz 주파수대에서의 상대적인 에너지 플롯 하나로 나타나는 경우가 가장 흔하다. 이런 원치 않는 주파수 요소는 고성능 아날로그-디지털 컨버터(ADC)나 디지털-아날로그 컨버터(DAC)의 기준 클록에 나타날 때 특히 좋지 않다. 이러한 ADC나 DAC들은 원치 않는 주파수의 앨리어싱이 여럿 나타나기 때문이다. 또한 고속 직렬 인터페이스용 PHY는 ADC나 DAC를 내장하는 경우가 많아 주파수 도메인 지터가 그 부분에서도 많은 우려를 낳고 있다.

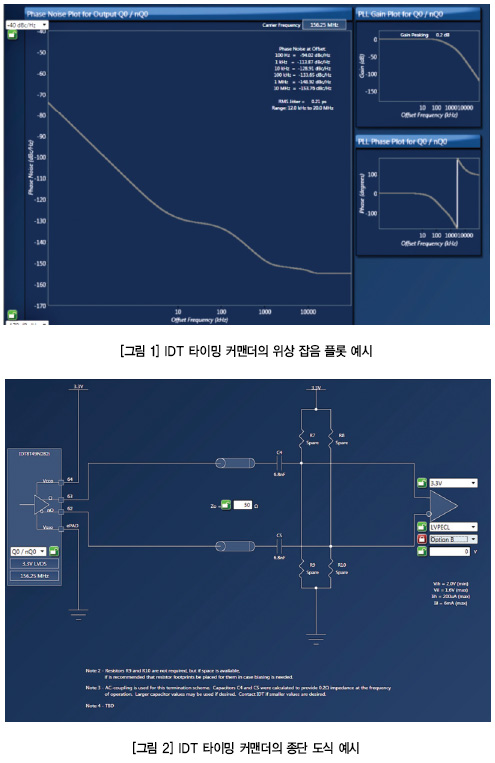

고성능 애플리케이션에서는 타이밍 부품의 위상 잡음 성능을 부품을 사용한 디바이스의 입력 명세와 비교할 필요가 있다. 위상 잡음 성능은 타이밍 부품의 정확한 구성에는 영향을 받지 않으며, 그렇기 때문에 주요 컨피규레이터 툴은 각각의 설정마다 이러한 플롯을 보여준다(그림 1 참조).

■ 신호 프로토콜, 전압 변환, 전력 공급 필터링

보드 설계에서 클록 트리는 크리스털이나 오실레이터 같은 주파수 소스뿐 아니라 대부분의 보드 서브시스템에서 디바이스들을 통합해 나가고 있다. 그 결과 싱글엔디드형(CMOS) 프로토콜과 하나 이상의 차동(differential) 프로토콜(예: LVDS) 사이에서 신호를 전환할 필요가 종종 생기며 전압 스윙(voltage swing) 역시 조정해야 할 경우가 종종 발생한다. 클록 트리는 보통 수동 부품의 연결로 이루어져 있지만 능동형 레벨 시프터가 가끔 사용되기도 한다. 이전에는 각 프로토콜의 전류 및 전압 명세에 익숙하지 못한 설계자가 이를 위해 많은 애플리케이션 노트를 봐야 했다. 그러나 컨피규레이터 툴은 특정 타이밍 부품의 입력이나 출력에 대해 이러한 프로토콜 그리고/또는 전압의 불일치를 해결하는 방법을 추천한다(그림 2 참조).

동일한 성능으로 제안된 회로도(도면)와 부품값을 생성해낼 수 있으며 이러한 부품값은 특히 고성능 장비에서 전력 공급 필터 및 루프 필터용으로 필요할 수 있다.

■ 중복 및 장애 시나리오

일상생활에서 신뢰도 높은 연결성이 점점 더 요구되면서 모바일 기기에서부터 테라비트 코어 라우터까지 모든 것들이 안정적으로 작동하는 것이 그 어느 때보다 중요해졌다. 음성 통화 스위치와 장애에 대한 내성이 높은 군용 시스템을 위해 개발된 기술들이 네트워크 계층을 따라 하단으로 전파되어 오면서 이제는 모든 시스템이 장애의 가능성(FIT 비율)을 최소화하고, 설령 장애가 발생하더라도 그 영향을 최소화하는 방식으로 설계되고 있다. 많은 시스템이 장애 시나리오 시의 동작에 대한 표준인 ITU-T G.8261 등 국제 표준을 준수할 필요도 있다.

타이밍 부품에 있어서 이는 주로 스위치오버(switchover)와 홀드오버(holdover)에 관한 문제이다. 스위치오버는 질적 저하나 신호의 총 손실이 발생한 클록을 확인해 백업 소스로 전환하는 과정을 말한다. 홀드오버는 스위치오버의 반대 경우로, 모든 백업 클록 소스가 부적합한 경우 발생하는데, 어느 정도의 기능성을 유지하기 위해 크리스털이나 크리스털 오실레이터(XO)에 의존한다.

믿을 수 있는 클록 트리를 생성하는 것은 시스템 차원의 문제이며 전체 클록 트리의 차원에서 해결해야 한다. 특히 외부적으로 정의된 경우라면 시스템 수준의 명세를 반드시 만족해야 한다. 이 부분은 여전히 숙련된 엔지니어가 관여하여 처리해야 하는 업무이다. 보드 설계자는 타이밍 부품 제조사의 숙련되고 시스템에 대한 지식을 숙지하고 있는 애플리케이션 엔지니어팀과 협력하여 이러한 문제를 해결할 필요가 있다. 그러나 이는 여러 제조사의 부품을 섞어 쓰는 사용자가 만족할 정도의, 칩을 확인하는 수준에서 바로 해결될 수 있는 문제가 아니다.

요약

보드 설계자라는 업무는 다양한 디지털, 아날로그, 소프트웨어, 열 및 기계 설계 등 다양한 주제에 대한 심도 있는 지식이 필요한 어려운 일이다. 클러킹의 영역에서 지난 5년 간 주파수 확산, 빠듯한 시간 및 주파수 도메인 지터 요건, 뒤죽박죽인 많은 신호 프로토콜과 전압 수준으로 이런 어려움이 더욱 빠르게 증가했다. 주요 부품 제조사는 이러한 문제를 인식하고 클록 트리 빌더, 파라메트릭 서치, 높은 성능에 사용이 편리한 컨피규레이터 툴들을 제공해 이러한 문제에 대응하고 있다. 이러한 툴은 보드 설계자들에게 큰 도움이 되지만 모든 문제를 해결해주는 것은 아니다. 여전히 남아있는 문제에 대해서는 클록 트리가 시스템에 미치는 영향을 충분히 이해하고 있는 유능한 애플리케이션 엔지니어팀의 도움이 필요하다. 보드 설계자는 툴과 애플리케이션 전문 지식을 제공하는 타이밍 부품 벤더와 협력하면 업무가 조금 더 수월해지고 노력의 결과가 성공적이라는 사실을 알게 될 것이다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>