[기고] 무선 시스템 테스트에서 타이밍과 동기화의 중요성

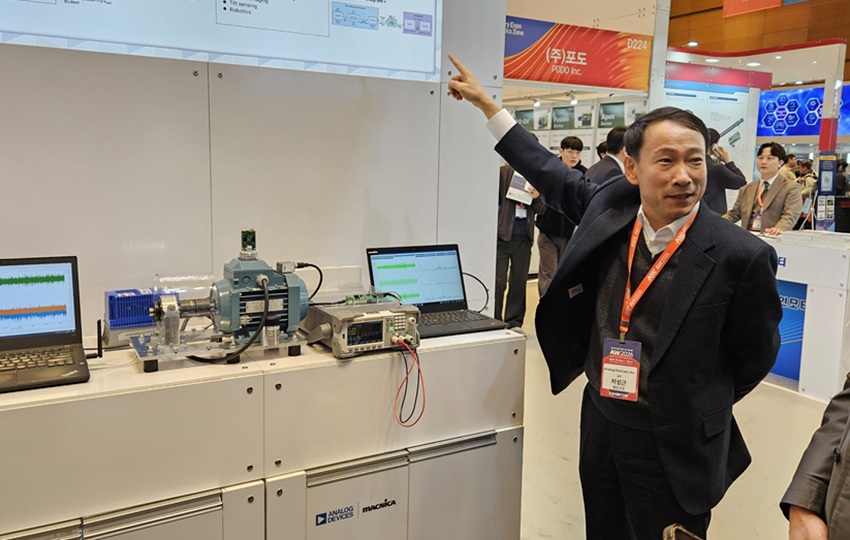

2023-08-07 제프리 라이언 F. 파주타가나(Jeffrey Ryan Fajutagana) 펌웨어 엔지니어, 키아나 키(Kiana Khey) 펌웨어 엔지니어, 아나로그디바이스(Analog Devices, Inc.)

이 글에서는 무선 시스템 테스트, 특히 타이밍 및 동기화와 관련한 시스템 레벨 테스트에서 고려해야 할 중요한 요소들에 대해 알아보고, 송신기와 수신기 블록 간에 특정 오차 범위 내에서 데이터를 무선으로 전송하는 데 있어서 이들이 얼마나 중요한지 살펴본다.

이 글에서 설명하는 테스트 핵심 요소들은 무선 시스템의 뛰어난 신뢰성과 동기화를 보장하기 위한 기능적 및 비기능적 규격, 시스템 한계, 그리고 버그를 이해하기 위한 테스트 사례를 개발하는 데 도움이 될 것이다.

이 글에서 설명하는 테스트 핵심 요소들은 무선 시스템의 뛰어난 신뢰성과 동기화를 보장하기 위한 기능적 및 비기능적 규격, 시스템 한계, 그리고 버그를 이해하기 위한 테스트 사례를 개발하는 데 도움이 될 것이다.

머리말

무선 기술이 빠르게 발전하면서 무선 통신의 새 시대가 열리고 있다. 무선 기술은 거의 모든 분야에서 사용되고 있으며 통신, 의료, 자동차, 우주 탐사를 비롯한 전 산업 분야에서 혁신을 일으키고 있다. 이 시장은 확고한 기반을 갖추고 빠른 성장세를 이어가고 있다.

무선 시장은 2019년 1조 4313억 달러에서 2024년 5조 5194억 달러 규모로 31%의 연평균 성장률(CAGR)을 나타낼 것으로 전망된다. 무선 기술은 지금도 꾸준히 진화하고 있으며 앞으로도 계속 더 높은 정확도, 더 향상된 가동 효율, 더 빠른 의사결정, 더 높은 데이터 레이트, 더 많은 비용 절감으로 더 많은 새로운 것들을 가능하게 할 것이다. 하지만 무선 기기들의 기능이 다양해지면서 무선 시스템 테스트의 복잡성 역시 높아지고 있다.

어떠한 무선 시스템이 적절히 작동하기 위해서는 정확한 타이밍과 동기화가 필수적으로 요구된다. 이는 시스템에 사용되는 송신기 클럭과 수신기 클럭을 지정된 허용오차 이내에서 일치시키는 프로세스이다. 이를 통해 최대의 패킷 무결성과 최적의 데이터 흐름을 달성할 수 있다. 모든 무선 시스템 테스트와 개발에서는 타이밍과 동기화를 중요하게 고려해야 한다.

이를 달성하기가 쉽지만은 않다. 클럭 소스는 드리프트를 일으키는 것으로 악명이 높기 때문이다. 마이크로초(μs) 대의 낮은 드리프트라 하더라도 시간이 경과하면서 계속 누적되면 동기화 소실로 이어질 수 있다. 완벽하게 동기화된 무선 시스템을 달성하기 위해서는 클럭들을 완벽하게 매칭해야 한다. 하지만 이렇게 하기가 현실적으로는 매우 까다로운 일이다. 드리프트는 클럭의 근원적인 특성으로서 클럭의 카운팅 시간에 오차를 일으키고, 궁극적으로 동기화를 어긋나게 만들 수 있다.

동기화가 불량한 시스템은 전송 성능을 떨어트리고 전송하고자 하는 데이터 품질을 떨어트릴 것이다. 뿐만 아니라 이것은 데이터 무결성을 떨어트리고 동작 오류로 이어질 수 있는데, 이 문제는 사람들의 건강, 보안, 안전과 관련한 애플리케이션에서 특히 더 중요하다. 이러한 애플리케이션에서 문제가 발생한다면 법적인 책임을 져야 하거나 고객들로부터 신뢰를 잃을 것이다.

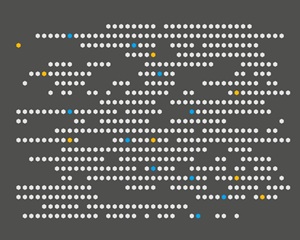

동기화가 잘 이루어진 시스템이 이처럼 중요하기 때문에, 정밀도와 이동성 같은 요구 사항에 따라 다음과 같은 다양한 동기화 기법들이 사용된다: 송신측-수신측 기반 동기화(sender-receiver-based synchronization)는 2웨이 메시지 교환이다. TPSN(Timing-sync Protocol for Sensor Networks)을 예로 들수 있다. TPSN은 노드들 사이에 동기화 펄스를 송신 및 수신함으로써 네트워크 동기화를 이룬다. 각 전송의 시간 오프셋을 타임스탬프로 기록하고 계산해서 클럭 시간 차이를 구하고, 이를 통해 노드들을 동기화한다.

SFD 기반 동기화(SFD-based synchronization)는 1웨이 메시지 교환을 사용한다. RBS(Reference Broadcast Synchronization)가 이 방식의 동기화를 사용한다. 지연 측정 동기화(delay measurement synchronization)는 수신측-수신측 기반 동기화와 마찬가지로 1웨이 메시지 교환인데, 다만 지연을 측정한다. 이 방식을 사용한 예로는 DMTS(Delay Measurement TimeSynchronization)를 들 수 있다.

이제 TPSN을 채택한 무선 시스템에 사용되는 다양한 타이밍 및 동기화 파라미터들에 대해 살펴보자. 각 파라 미터가 시스템의 전반적인 기능성에 어떻게 영향을 미치는지, 그리고 안정적이고 잘 동기화된 시스템을 달성 하기 위해서는 이들 파라미터를 어떻게 구성해야 하는 지 알아볼 것이다. 이들 파라미터는 무선 시스템을 테스트할 때 버그를 식별하고(타이밍 및 동기화와 관련한) 시스템 한계를 파악하는 데에 도움이 된다.

타이밍 및 동기화 파라미터

동기화 기준점(Sync Reference)

동기화 기준점을 사용하면 소프트웨어로 송신 및 수신 명령들을 정확하게 스케쥴링할 수 있다. 이 기준점으로부터 양의 오프셋으로 이벤트들을 스케쥴링하여 송신기와 수신기 사이에 동기화를 이룰 수 있다. 무선 시스템에서는 주로 다음과 같은 기준점들을 사용한다:

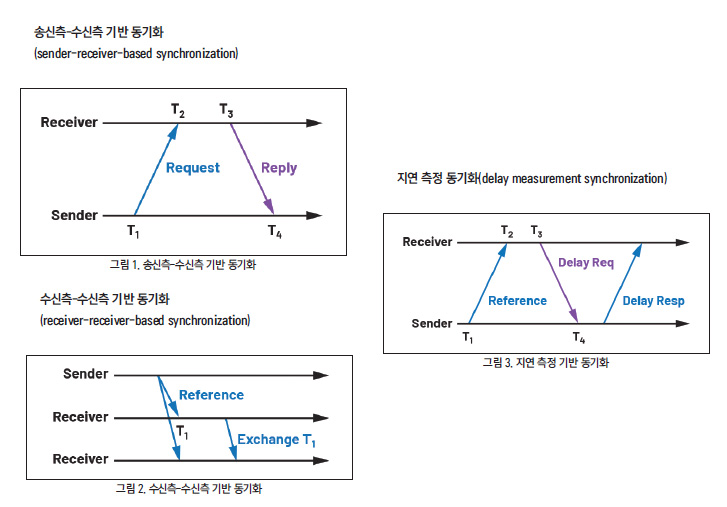

Sync Now

동기화 명령(set_sync_ref(NOW))이 처리되는 바로 그 시점을 동기화 기준점으로 설정한다. 그림 4는 (set_sync_ref(NOW)) 명령을 사용해서 설정된 기준점을 기준으로 패킷을 전송하는 것을 보여준다.

Sync SFD

SOF(start of frame)를 동기화 기준점으로 설정하며, 유효한 동기화 워드가 검출되었다는 것을 지시한다.(set_sync_ref(SFD)) 명령을 보내면, 이 명령이 전송되고 나서 첫 번째 SFD(start of frame detect) 직후에 기준점이 설정된다. 그림 5는 SFD 기준점을 기준으로 해서 두 번째 송신 패킷을 전송하는 것을 보여준다.

Sync Latest

이 동기화 모드는 모든 SOF에 동기화 기준점이 설정된다. 그림 6에서 보듯이, 후속 유효 패킷 동기화 워드가 수신될 때 마다 동기화 기준점이 가장 최근 SOF의 타임스탬프로 업데이트된다.

이러한 동기화 모드들을 사용해서 두 노드 사이에 동기화를 할 수 있다. 그런데 하드웨어 클럭은 드리프트를 일으키는 것으로 잘 알려져 있으며, 이 때문에 시간이 지나면서 주파수가 달라지고 부정확성을 일으킬 수 있다. 그 결과, 어느 특정 시점에는 클럭들이 차이가 날 수 있다. 송신 클럭과 수신 클럭의 동기화 기준점을 되풀이해서 업데이트함으로써 스큐와 드리프트의 영향을 최소화할 수 있다.

동기화가 잘 이루어진 시스템이 이처럼 중요하기 때문에, 정밀도와 이동성 같은 요구 사항에 따라 다음과 같은 다양한 동기화 기법들이 사용된다: 송신측-수신측 기반 동기화(sender-receiver-based synchronization)는 2웨이 메시지 교환이다. TPSN(Timing-sync Protocol for Sensor Networks)을 예로 들수 있다. TPSN은 노드들 사이에 동기화 펄스를 송신 및 수신함으로써 네트워크 동기화를 이룬다. 각 전송의 시간 오프셋을 타임스탬프로 기록하고 계산해서 클럭 시간 차이를 구하고, 이를 통해 노드들을 동기화한다.

SFD 기반 동기화(SFD-based synchronization)는 1웨이 메시지 교환을 사용한다. RBS(Reference Broadcast Synchronization)가 이 방식의 동기화를 사용한다. 지연 측정 동기화(delay measurement synchronization)는 수신측-수신측 기반 동기화와 마찬가지로 1웨이 메시지 교환인데, 다만 지연을 측정한다. 이 방식을 사용한 예로는 DMTS(Delay Measurement TimeSynchronization)를 들 수 있다.

이제 TPSN을 채택한 무선 시스템에 사용되는 다양한 타이밍 및 동기화 파라미터들에 대해 살펴보자. 각 파라 미터가 시스템의 전반적인 기능성에 어떻게 영향을 미치는지, 그리고 안정적이고 잘 동기화된 시스템을 달성 하기 위해서는 이들 파라미터를 어떻게 구성해야 하는 지 알아볼 것이다. 이들 파라미터는 무선 시스템을 테스트할 때 버그를 식별하고(타이밍 및 동기화와 관련한) 시스템 한계를 파악하는 데에 도움이 된다.

타이밍 및 동기화 파라미터

동기화 기준점(Sync Reference)

동기화 기준점을 사용하면 소프트웨어로 송신 및 수신 명령들을 정확하게 스케쥴링할 수 있다. 이 기준점으로부터 양의 오프셋으로 이벤트들을 스케쥴링하여 송신기와 수신기 사이에 동기화를 이룰 수 있다. 무선 시스템에서는 주로 다음과 같은 기준점들을 사용한다:

Sync Now

동기화 명령(set_sync_ref(NOW))이 처리되는 바로 그 시점을 동기화 기준점으로 설정한다. 그림 4는 (set_sync_ref(NOW)) 명령을 사용해서 설정된 기준점을 기준으로 패킷을 전송하는 것을 보여준다.

Sync SFD

SOF(start of frame)를 동기화 기준점으로 설정하며, 유효한 동기화 워드가 검출되었다는 것을 지시한다.(set_sync_ref(SFD)) 명령을 보내면, 이 명령이 전송되고 나서 첫 번째 SFD(start of frame detect) 직후에 기준점이 설정된다. 그림 5는 SFD 기준점을 기준으로 해서 두 번째 송신 패킷을 전송하는 것을 보여준다.

Sync Latest

이 동기화 모드는 모든 SOF에 동기화 기준점이 설정된다. 그림 6에서 보듯이, 후속 유효 패킷 동기화 워드가 수신될 때 마다 동기화 기준점이 가장 최근 SOF의 타임스탬프로 업데이트된다.

이러한 동기화 모드들을 사용해서 두 노드 사이에 동기화를 할 수 있다. 그런데 하드웨어 클럭은 드리프트를 일으키는 것으로 잘 알려져 있으며, 이 때문에 시간이 지나면서 주파수가 달라지고 부정확성을 일으킬 수 있다. 그 결과, 어느 특정 시점에는 클럭들이 차이가 날 수 있다. 송신 클럭과 수신 클럭의 동기화 기준점을 되풀이해서 업데이트함으로써 스큐와 드리프트의 영향을 최소화할 수 있다.

시간 오프셋(Time Offset)

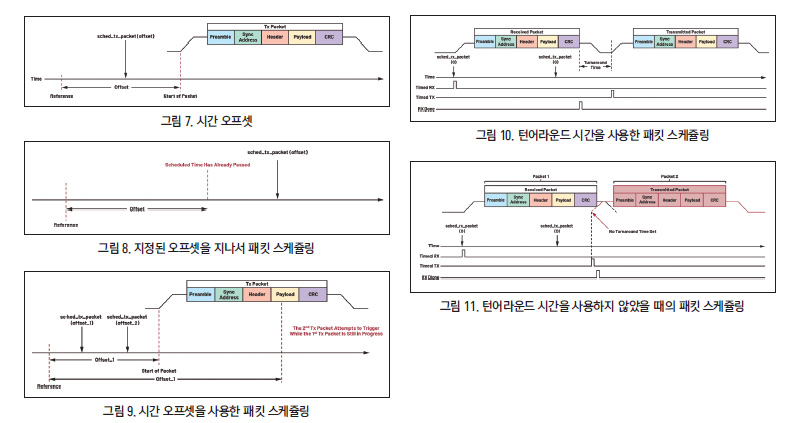

시간 오프셋은 시간 포착 또는 동기화 기준점이 시작되는 시점으로부터 현재 시간까지의 시간 차이다. 이 파라미터는 송신 또는 수신할 때 사용된다. 최소 시간 오프셋은 송신/수신 명령을 즉시 실행하기 위해서 필요한 최소 시간이다.

이 파라미터는 API와 무선 기기의 기본 지연시간에 근거해서 계산할 수 있다. 이보다 낮게 설정하면 스케쥴링 오류를 일으키고 송신/수신 트랜잭션 실패로 이어질 수 있다.

그림 8은 시간 오프셋이 최소 허용 시간보다 낮아서, 명령이 이미 지나간 시간으로 스케쥴링된 경우를 보여준다. 두 개의 연속된 송신 또는 수신 명령(Tx-Tx 또는Rx-Rx)을 실행할 때, 두 명령이 모두 단일 시간 기준점을 사용한다고 가정할 경우, 첫 번째 패킷의 크기는 두번째 명령을 성공적으로 실행하는 데 사용할 수 있는 시간 오프셋을 결정하는 데 있어서 중요한 요소이다.

첫번째 패킷의 길이가 늘어나면 두 번째 명령의 시간 오프셋 역시 늘어나야 성공적인 트랜잭션이 이루어진다. 허용 가능한 최소 시간 오프셋보다 낮은 시간 오프셋을 사용하면 첫 번째 패킷이 실행되는 도중에 두 번째 패킷을스케쥴링하게 되어 오류가 일어날 것이다. 그림 9는 이같은 상황을 보여준다.

최대 시간 오프셋(Max Time Offset)

최대 시간 오프셋은 지정된 시간을 벗어나서 패킷을 스케쥴링하는 것을 방지하기 위해 사용된다. 클럭 드리프트 때문에 동기화 기준점으로부터 너무 먼 시간으로 패킷을 스케쥴링하면 부정확한 스케쥴링을 유발하여, 신호 검출 타임아웃이나 SOF 타임아웃을 일으킬 수 있다. 이들 타임아웃에 관해서는 뒤쪽 ‘타임아웃’ 부분에서 다시 자세히 설명한다.

턴어라운드 시간(Turnaround Time)

턴어라운드 시간은 물리(PHY) 층이 수신 모드에서 송신 모드로 또는 그 반대로 전환하기 위해 필요한 시간을 말한다. 턴어라운드 시간 동안에는 아날로그 RF 프론트 엔드의 부품들이 파워업하고 안정화해야 하므로 상당한 시간이 소요된다. 낮은 지연시간을 요구하는 애플리케이션에서는 이 시간 소모가 더 중요하다.

이러한 예로는 로봇 팔이나 그 밖에 다른 기계 장비를 원격으로 제어하는 산업용 시스템의 공정 제어 루프를 들 수 있다. 턴어라운드 시간은 반이중 트랜시버에만 해당된다. 턴어라운드 시간은 사용자가 수신 패키지를 받고 난 다음, PHY 층이 다시 준비되는 대로 송신 패킷을 전송하고자 할 때 (혹은 그 반대일 때) 사용된다.

그림 10에서는 송신 패킷과 수신 패킷의 두 가지 패킷을 볼수 있다. 여기서 sched_rx_packet(0) 명령은 트랜시버가 패킷을 수신할 준비를 하게 한다. 오프셋은 0으로 설정되었는데, 이는 PHY가 준비되면 트랜시버가 즉시 패킷을 수신하기 시작한다는 뜻이다. 패킷을 수신하는 동안, sched_tx_packet(0) 명령을 전송해서 PHY 층이 턴어라운드 상태로 전환하도록 한다. 소프트웨어가 수신 완료(Receive Done)를 기준점으로 삼고 턴어라운드 시간 값을 더해서 송신 패킷을 스케쥴링한다.

그림 11은 소프트웨어에 턴어라운드 시간을 설정하지 않았을 경우, 어떤 상황이 벌어지는지 보여준다. 턴어라운드 값을 설정하지 않았으므로, 스케쥴러가 첫 번째 패킷 후에 바로 다음 패킷을 송신하도록 설정한다. PHY 층이 아직 상태를 전환하지 않았으므로 송신이나 수신 준비가 되지 않았다는 것을 스케쥴러가 알지 못하기 때문에, 다음 패킷은 실패할 수밖에 없다.

이는 턴어라운드 시간을 설정하는 것이 왜 중요한지 잘 보여준다. 턴어라운드 시간을 설정하지 않으면, 송신 도중에 수신을 스케쥴링 하는 것이(혹은 그 반대로 하는 것이) 성공적으로 실행될지 장담할 수 없다. 턴어라운드 시간 값은 PHY 층이 PHY 송신 상태에서 PHY 수신 상태로 전환하는 데 드는 시간에 근거해서 설정할 수 있다. 이 설정은 RF 디바이스가 수시로 송신에서 수신으로, 또는 반대로 전환하는 경우에 중요하다.

패킷간 간격(Interpacket Gap)

패킷간 간격은 이전 프레임의 마지막 비트부터 후속 프레임의 첫 번째 비트까지의 시간이다(둘 다 무선). 턴어라운드 시간과 마찬가지로, 패킷간 간격은 패킷을 송신/수신하면서 또 다른 패킷을 전송하고자 할 때 기준점으로 사용할 수 있다. 차이점은, 패킷간 간격은 동일한 유형의 두 패킷 (Tx-Tx 또는 Rx-Rx) 사이에 사용된다는 것이다. 패킷간 간격은 트랜시버가 PHY를 다음 패킷을 전송할 수 있게 준비시키기 위해서 필요하다.

그림 12에서는 송신 패킷과 송신 패킷으로 이루어진 두 개의 패킷을 볼 수 있다. 이 경우, sched_tx_packet(0) 명령은 트랜시버가 패킷을 즉시 전송하도록 한다. 첫 번째 패킷이 송신을 완료하지 않은 상태에서 또 다른 sched_tx_packet(0) 명령을 전송함으로써, 현재의 패킷 전송이 완료되는 대로 다음 패킷의 전송을 시작하도록 설정한다.

패킷간 간격은 이 다음 패킷을 전송할 때 스케쥴러에 의해 기준점으로 사용된다. 이 시간은 PHY의 하강 및 상승 시간에 따라서 결정된다. 그럼으로써 PHY가 또 다른 패킷 송신/수신을 할 수 있는 준비가 된다. 그림 13은 패킷간 간격을 설정하지 않았을 때 오류가 발생하는 것을 보여준다. 스케쥴러는 첫 번째 패킷이 송신/수신을 완료하는 대로 다음 패킷을 전송하도록 설정한다. 하지만 턴어라운드 시간과 마찬가지로, PHY가 또 다른 송신/수신을 할 준비가 되지 않았다는 것을 스케쥴러는 모른다.

타임아웃(Timeout)

무선 시스템에서 타임아웃을 사용하면 디바이스가 응답을 무한정 기다리는 것을 방지할 수 있다. 디바이스가 유효한 응답을 기다리도록 허용할 수 있는 시간을 근거로 해서 타임아웃을 설정할 수 있다. 이 시간 안에 유효한 응답이 수신되지 않으면 오류가 발생한 것으로 보고된다. 주로 사용되는 타임아웃으로는 다음과 같은 것들을 들 수 있다:

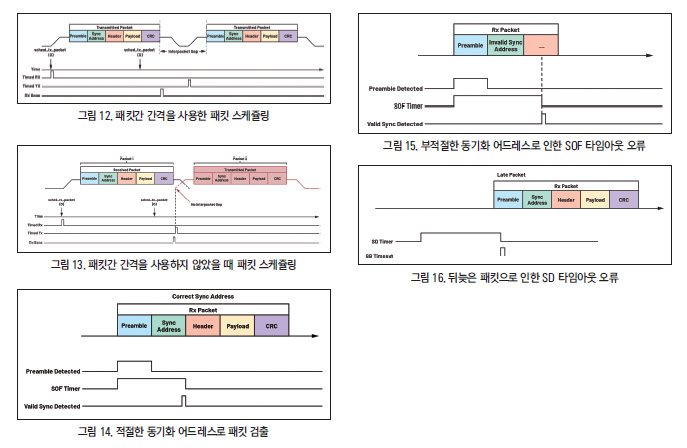

SOF 타임아웃(Start of Frame Timeout)

SOF 타임아웃은 부적절한 동기화가 검출되었을 때 발생한다. 동기화 워드를 수신하기 전에 SOF 타이머가 만료 되었을 때도 SOF 타임아웃이 발생한다.

그림 14는 SOF 타이머 시간 안에 유효한 동기화 어드레스를 검출한 경우이고, 그림 15는 할당된 시간 안에 유효한 동기화 어드레스가 검출되지 않음으로써 SOF 타임아웃이 발생한 경우이다.

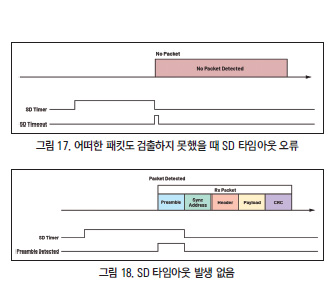

신호 검출 타임아웃(Signal Detect Timeout)

신호 검출 타임아웃은 SD 시간 안에 유효한 프리앰블(preamble)을 검출하지 못하거나 프리앰블을 수신하기 전에 타이머가 만료되었을 때 발생한다. 그림 16과 그림 17은 이러한 상황들을 보여준다.

그림 18은 타이머 시간 안에 유효한 프리앰블을 검출한 경우이다. 그러므로 타임아웃이 발생하지 않는다.

타임아웃 시간을 적절히 설정하는 것이 중요하다. 너무 짧거나 너무 길지 않아야 한다. 타임아웃 시간이 너무 짧으면 유효한 패킷이라도 짧은 타임아웃 때문에 시간이 충분하지 않아서 검출하지 못할 수 있다. 너무 긴 타임아웃은 잘못된 타임아웃 수를 줄일 수는 있지만, 디바이스가 더 긴 시간 동안 동작 상태로 있어야 하므로 더 많은 전력을 소모하게 된다.

맺음말

시간 동기화는 무선 시스템에서 중요한 요소이다. 데이터 무결성을 중요하게 요구하는 애플리케이션에서는 특히 더 그렇다. 여러 가지 요인들이 시스템 동기화에 영향을 미칠 수 있다. 동기화와 관련해서 타이밍 파라미터들의 연관성과 특성을 이해함으로써 고도로 신뢰할 수 있는 무선 시스템을 달성하고 무선 시스템 테스트를 실시하는 데 도움이 될 것이다.

참고 문헌

Aslam, Muhammad, Xianjun Jiao, Wei Liu, and Ingrid Moerman. “An Approach to Achieve Zero Turnaround Time.” IEEE Access, December 2018.

“Five Dangers of Poor Network Timekeeping + Easy and Cost Effective Solutions to Avoid Networks Fall Out Sync.” Symmetricom, 2013.

Kulakli, Ali Burak and Kayhan Erciyes. “Time Synchronization Algorithms Based on Timing-Sync Protocol in Wireless Sensor Networks.” Istanbul. IEEE, December 2008.

Garcia-Pineda, Miguel. “A Group-Based Architecture and Protocol for Wireless Sensor Networks.” University of Valencia, thesis paper.

Mizrahi, Tal. “A Game Theoretic Analysis of Delay Attacks Against Time Synchronization Protocols.” 2012 IEEE International Symposium on Precision Clock Synchronization for Measurement, Control, and Communication Proceedings, October 2012.

Roche, Michael. “Time Synchronization in Wireless Networks.” McKelvey School of Engineering, April 2006.

“The Global Wireless Connectivity Market Is Estimated to Grow from USD 69.0 Billion in 2020 to USD 141.1 Billion by 2025, at a CAGR of 15.4%.” ReportLinker, October 2020.

“GNSS Market Report Issue 4.” European Union Agency for the Space Programme, 2015.

Vaez-Ghaemi, R.(2018, June 14). “Timing and Synchronization Standards for Wireless Networks.” VIAVI Solutions, 2018.

저자 소개

제프리 라이언 F. 파주타가나(Jeffrey Ryan F. Fajutagana)는 아나로그디바이스(Analog Devices) 필리핀의 소프트웨어 시스템 엔지니어링 그룹 펌웨어 엔지니어이다. 2018년에 필리핀 대학 - 로스 바뇨스에서 전기공학 학사학위를 취득하고 졸업과 함께 ADI에 입사했다. 문의. jeffrey.fajutagana@analog.com

키아나 V. 키(Kiana V. Khey)는 아나로그디바이스 필리핀의 소프트웨어 엔지니어링 그룹 펌웨어 엔지니어이다. 2015년에 필리핀 기술 대학 - 비사야스에서 전자공학 학사학위를 취득했다. 문의. kiana.khey@analog.com

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

본 기사의 전문은 PDF문서로 제공합니다.

(로그인필요)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

100자평 쓰기