업계가 TSV 기반의 3D 집적 기법으로 이동함에 따라 수직 다이 적층을 기반으로 한 3D 대안 기술의 이용이 가능해졌다. 이 대안 기술은 TSV 없이도 높은 패키징 밀도를 제공한다. 이 SiP 기반의 칩 적층 기술들은 어셈블리를 더 소형화 해주는 새로운 옵션들을 제공하면서 더 적은 개발 비용, 공급망의 안정성, 파운드리 간 호환성, 신속한 적기 출시 기회를 제공한다.

전자 패키지를 소형화하는 방법을 찾고 있음에도 불구하고 주문형 ASIC이나 복잡한 3D 집적 방식을 활용할 자원이 부족한 설계 담당자들도 이제는 여러 소자를 소형 SiP(system-in-package) 구조에 집적시키는 칩 적층 기술을 이용할 수 있게 됐다. 기존의 멀티칩 패키징 기법들을 이용할 경우에 직면하게 되는 비용과 크기의 상승을 피하면서도 중소량 애플리케이션을 지원하는데 적합한 믿을 만한 혁신적인 접근법이 개발됐다. 배어 다이(bare die)와 수직 인터커넥트(Vertical Interconnect, VI)/인터포저(interposer) 구조를 이용하는 이 적층 기술은 같거나 다른 다이들을 다중 칩으로 조합하거나, 디스크리트 소자 또는 집적 수동 소자들의 통합 패키징(co-packaged)을 가능하게 한다. 이 접근방식은 ASIC 파운드리 공정과는 무관하며, TSV(Through-Silicon Via) 기술이 필요 없기 때문에, 서로 다른 반도체 공정이나 제조원으로부터 생산된 여러 IC를 통합하는 설계에 매우 적합하다. 큰 선투자 NRE 비용과 오랜 개발 사이클이 수반되는 SoC(System-on-Chip) ASIC 구현과는 달리, 주문형 SiP 패키지는 더 큰 설계 유연성 및 시장 출시 시간의 단축뿐 아니라, 입증된 저비용 솔루션이 되고 있다.

소자 패키징의 진화

패키징 기술은 작아진 크기에 더 많은 기능을 집적해야 하는 지속적인 요구를 충족시키기 위해 싱글칩 표면 실장(SMT) 패키지에서부터 MCM(Multi-Chip Module), 그리고 POP(Package-On-Package) 솔루션으로 계속 진화해왔다. TSV 기술을 통해 연결된 수직 적층형 IC의 3D 집적은 아마도 궁극적인 진화를 표방하겠지만, 이 기술이 완전히 상업적으로 채택되려면 아직도 수년은 더 있어야 한다. 아직도 소수의 공급업체와 애플리케이션만이 대량생산 중인 이 기술이 널리 확산되기 위해서는 비용, 열 관리, 개발 인프라 등의 과제를 해결해야 한다.

3D 집적의 대안 접근방식

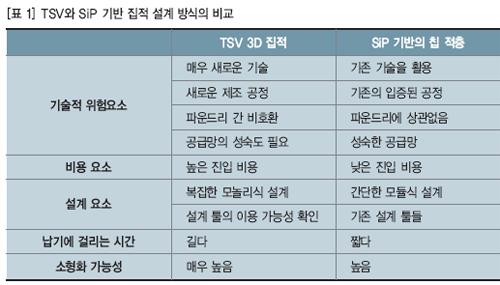

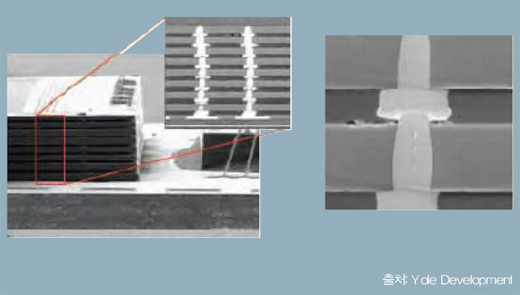

3D 집적의 대안 접근방식은 TSV 기술에 의존하지 않고 고집적도로 인터포저(수동 소자를 포함하거나 안 하거나) 및 수직 인터커넥트 구조를 이용한 배어 다이 적층으로 구현할 수 있다. 이 기술은 SiP 기반의 기술을 이용하는 새로운 방식으로 보다 전통적인 프로세스와 어셈블리 기법들을 채택함으로써 소량/중량의 애플리케이션에 매우 안정적인 솔루션을 제공한다. 이 적층 기술을 채택하면 협피치(fine-pitch) 플립칩, 웨이퍼의 박막화(thinning), 고밀도 후막 세라믹 기판 분야에서의 발전된 기술을 이용해 디스크리트 소자 또는 집적 수동 부품들과 통합 패키징되며, 동일하거나 다른 소자와의 멀티칩 어셈블리 설계가 가능해진다. 이로써 OEM들은 TSV 같은 대안 멀티칩 패키징 기법에서 직면하게 되는 진입장벽을 피해 갈 수 있다. 이 접근방식은 또한 특정 파운드리 공정에 의존하지 않기 때문에, 서로 다른 반도체 제조원의 여러 IC의 통합 설계에 적합하다(표 1 참조).

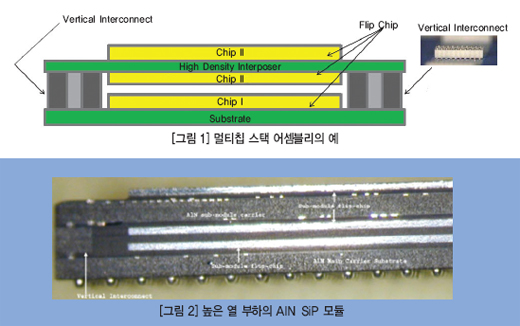

그림 1은 고밀도 인터포저 및 수직 인터커넥트(VI) 구조를 이용해서 수직으로 장착된 여러 개의 IC를 이용한 칩 적층 설계를 보여준다. 이 유연한 접근방식은 동일하거나 서로 다른 여러 개의 다이가 디스크리트 소자 또는 집적 수동 소자와 함께 확장성이 좋은 아키텍처에 통합 패키징 될 수 있도록 해준다. 이 패키지에 이용되는 세라믹 VI 구조는 기계적 적층 구조와 층 간의 전기적 연결을 같이 제공하며 애플리케이션의 핀 수와 선폭 기술에 맞춰 쉽게 맞춤화할 수 있다. 또한 세라믹 VI 구조의 이용은 와이어본드를 제거해 시스템 크기와 잠재적 (전기적, 열적) 성능을 향상시켜 준다.

사례 연구: 높은 열 부하의 다이 적층

그림 2는 세라믹 기반 3D 적층의 한 가지 적용을 설명한다. 이 사례는 고밀도 멀티칩 메모리 스택에 대한 것이다. 구성 소자의 열 부하를 관리하기 위해서는 패키지의 높은 열 전도성이 필요한데, 이는 부분적으로 높은 열 전도성을 가진 AlN(Aluminum Nitride) 세라믹 기판과 전도성 수지를 이용해서 구성할 수 있다.

사례 연구: 소형화된 무선 오디오 DSP/트랜시버 모듈

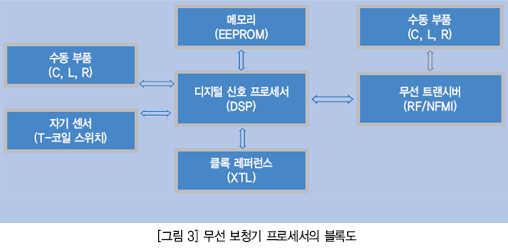

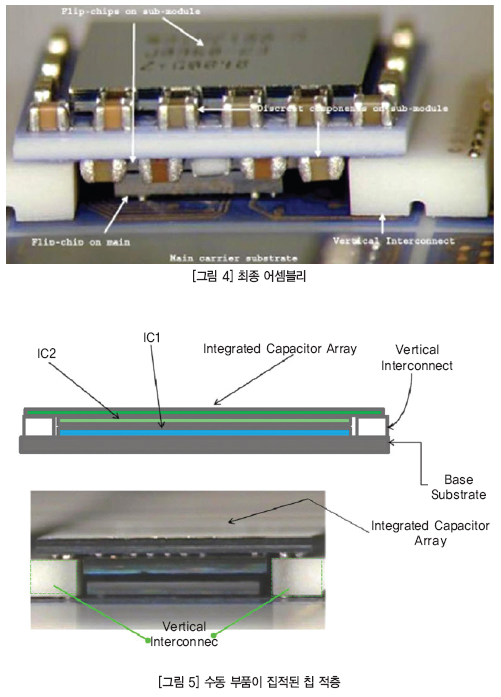

이 방식이 실제로 어떻게 적용될 수 있는가를 보여주는 또 다른 예가 아래에 나와 있다. 그림 3은 보청기(여기서는 온세미컨덕터의 AYRETM 오디오 디지털 신호 프로세서)에 사용되는 무선 DSP/트랜시버 모듈의 기능 블록도이다. 이 시스템은 다양한 능동 부품 및 수동 부품들을 포함하고 있는데, 최종 애플리케이션의 엄격한 크기 제한 때문에 가장 작은 폼팩터에 패키징 해야 한다. 고밀도 후막 세라믹 기판, 수직 인터커넥트 구조, 웨이퍼/다이 박막화(wafer/die thinning), 협피치 플립칩 어셈블리, 3D 적층을 포함하는 기술들이 모두 합쳐져 그림 4에 나와 있는 소형 SiP 어셈블리를 실현할 수 있었다.

수동 소자들을 패키지 기판이나 인터포저에 집적시킴으로써 크기를 더 줄일 수 있다. 그림 5는 VI 구조와 함께 조립되어 있는 두 개의 능동 IC의 예이다. 그러나 이 경우, 상부의 세라믹 서브모듈은 실리콘 집적 커패시터 어레이(온세미컨덕터 SiPArray™ 기술)로 대체됨으로써 커패시터가 필요 없으며 플립칩으로 실장될 능동 소자를 위한 마운팅/박막 라우팅 플랜 역할을 해준다. 이 방법은 디스크리트 부품들을 효과적으로 기판 안에 내장함으로써 어셈블리를 더 얇게 해준다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>