“NexFET™ Power Block으로 디스크리트 솔루션 절반으로 줄일 것”

단일 패키지에 2개의 NexFET MOSFET 스택 … 최대 효율, 주파수 및 전력밀도 제공 세계적인 반도체업체인 TI 코리아(www.ti.com/ww/kr)는 전력 MOSFET 경쟁 디바이스의 1/2의 공간으로 25A 조건에서 90% 이상의 효율을 달성할 수 있는 동기식 MOSFET 하프 브리지를 출시했다.

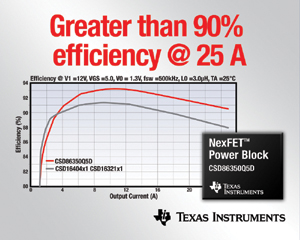

세계적인 반도체업체인 TI 코리아(www.ti.com/ww/kr)는 전력 MOSFET 경쟁 디바이스의 1/2의 공간으로 25A 조건에서 90% 이상의 효율을 달성할 수 있는 동기식 MOSFET 하프 브리지를 출시했다.

한철 TI코리아 이사는 “전자회로 디자이너들은 파워블록의 보다 작아진 면적과 보다 높아진 효율문제에 직면해 있는게 현실”이라며 “TI의 NexFET 파워 블록은 이러한 디자이너들에게 효과적인 솔루션”이라고 강조했다.

TI의 새로운 CSD86350Q5D Power Block은 2개의 비대칭 NexFET 전력 MOSFET을 첨단 패키지에 통합하여 서버, 데스크톱 및 노트북 PC, 기지국, 스위치, 라우터, 고전류 POL(point-of-load) 컨버터 등 저전력 동기식 벅 하프-브리지 애플리케이션에서 고성능을 제공한다.

NexFET Power Block은 효율과 전력밀도를 향상시킬 뿐만 아니라 최대 1.5MHz의 스위칭 주파수로 최대 40A의 전류를 생성할 수 있기 때문에 솔루션의 크기와 비용을 줄여준다. 최적화된 핀아웃과 접지 리드 프레임은 개발 시간을 대폭 줄여주는 동시에 전체 회로 성능을 향상시킨다. 또한, NexFET Power Block은 비용 효율적인 방법으로 GaN 등과 같은 다른 반도체 기술에 상응하는 성능을 달성할 수 있다.

한철 TI코리아 이사는 “CSD86350Q5D Power Block의 5mm x 6mm SON 아웃라인은 5mm x 6mm QFN 패키지로 제공되는 2개의 디스크리트 MOSFET에 비해 절반의 크기가 가능하다”며 “이 솔루션은 경쟁 제품에 비해 2% 높은 효율과 20% 낮은 전력손실 특성을 제공하는 등 25A 동작 조건에서 90% 이상의 전력 효율을 제공한다”고 설명했다.

이 밖에도 CSD86350Q5D Power Block은 경쟁 솔루션에 비해 전력 손실을 증가시키지 않으면서 2배의 주파수를 제공한다. 또한 하단에 노출 접지 패드를 제공하는 SON 패키지로 레이아웃을 단순화시킬 수 있다는 특징을 제공한다.

TI의 NexFET 전력 MOSFET 기술은 고전력 컴퓨팅, 네트워킹, 서버 시스템, 전력공급장치 등의 에 너지 효율을 향상시킨다. 이러한 고주파, 고효율 아날로그 전력 MOSFET은 시스템 설계자들이 최첨단 DC/DC 전력 컨버전 솔루션에 접근할 수 있도록 해준다.

너지 효율을 향상시킨다. 이러한 고주파, 고효율 아날로그 전력 MOSFET은 시스템 설계자들이 최첨단 DC/DC 전력 컨버전 솔루션에 접근할 수 있도록 해준다.

TI의 NexFET™ Power Block은 독특한 구조를 지니고 있다. MOSFET은 플래너(Planar)와 트랜치(Trench) 기술로 나뉘어지는데, 대다수의 파워로직 설계방식은 트랜치 설계방식을 사용하고 있다. TI의 NexFET™ 기술은 트랜치 기술에서 진일보한 하이 퀄리티 스피드용에 적합한 기술이다. 한철 이사는 “고전적인 플래너 방식이나 트랜치 기술과 달리 TI의 NexFET™는 고밀도 구조에 낮은 게이트 차저를 제공한다”며 “경쟁사의 제품들과 비교해 높은 효율과 낮은 전력손실을 보이는 것은 이러한 공정기술과 패키징 기술로 차별화를 두고 있기 때문”이라고 설명했다.

NexFET Power Block 디바이스는 5mm x 6mm SON 패키지로 TI와 TI의 공식 대리점을 통해 양산되고 있다. 가격은 1,000개 수량 기준으로 CSD86350Q5D은 개당 1.75달러이다. 샘플과 평가 모듈도 제공되고 있다.

이재용 기자(hades@cyberes.co.kr)

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>