28nm FPGA를 이용한 100GbE 스위칭 솔루션의 구현

고속 100GbE 통신 네트워크 표준들이 융합됨에 따라서 스위칭 기능이 인터넷의 매끄러운 작동을 위해서 중요한 역할을 하고 있다. 집합적인 네트워크 트래픽이 매 6개월마다 두 배로 늘어나고 다중의 프로토콜에 걸친 전송 때문에 복잡성이 증가함으로써 현행 스위치 아키텍처가 한계에 다다르고 있다. 오늘날의 단일칩 기반 아키텍처는 이와 같이 증가된 대역폭 및 복잡성에 대한 요구를 충족하지 못하므로 고속 네트워크의 요구를 충족하는 효율적인 알고리즘과 스위칭 아키텍처를 개발할 필요성이 대두되고 있다. Stratix V FPGA를 이용함으로써 하드웨어 디자이너는 QoS를 달성하면서 시스템으로 데이터 분배를 매끄럽게 하는 차세대 스위치 및 라우터를 위한 진정한 100GbE 솔루션을 구현할 수 있을 것이다.

Rishi Chugh / 알테라 코퍼레이션 수석 제품 마케팅 매니저

컴퓨터 네트워크와 고속 100GbE 네트워크의 지능적인 인터커넥트 구조로서 스위칭 네트워크가 이용된다. 전통적으로 이들 인터커넥트 네트워크는 전화, 컴퓨터, 인터넷 인프라 네트워크에서 개별적으로 구축되었다. 오늘날의 통신 네트워크는 분산 프로세싱이 가능한 단일 인터커넥트 네트워크를 목표로 공통적인 인터커넥트 스위칭 기술로 융합되고 있다. TDM(time-division multiplexed) 스위칭을 기반으로 하던 전통적인 전화통신 네트워크가 이더넷/IP 패킷 기반 스위칭 네트워크로 전환하고 있다. 이러한 전환은 스위칭 기능에 영향을 미치는데, 이것은 이더넷 프레임과 IP 패킷은 가변 패킷 길이라서 스위치의 버퍼링과 분할에 복잡성을 가중시키기 때문이다. 이러한 IP 스위칭으로 전환을 위해서는 기존 네트워크를 지원해야 하면서 하이브리드 스위치를 필요로 한다.

오늘날의 통신 네트워크는 분산 프로세싱이 가능한 단일 인터커넥트 네트워크를 목표로 공통적인 인터커넥트 스위칭 기술로 융합되고 있다. TDM(time-division multiplexed) 스위칭을 기반으로 하던 전통적인 전화통신 네트워크가 이더넷/IP 패킷 기반 스위칭 네트워크로 전환하고 있다. 이러한 전환은 스위칭 기능에 영향을 미치는데, 이것은 이더넷 프레임과 IP 패킷은 가변 패킷 길이라서 스위치의 버퍼링과 분할에 복잡성을 가중시키기 때문이다. 이러한 IP 스위칭으로 전환을 위해서는 기존 네트워크를 지원해야 하면서 하이브리드 스위치를 필요로 한다.

하이브리드 스위치 패브릭 디바이스는 이더넷, SONET, TDM 등의 각기 다른 프로토콜을 지원하며 백플레인 스위칭에도 이용된다. 이들 디바이스는 또한 8B/10B와 64B/66B 같은 각기 다른 인코딩 방식에 더해서 SPI-4/-5.2, Interlaken, SRIO, XAUI 같은 다양한 인터커넥트 프로토콜을 지원해야 한다. 스위치 내부에서 이들 패킷은 버퍼에 저장되고 더 우수한 전체적인 네트워크 트래픽 효율을 달성하기 위해서 스위치 알고리즘에 따라서 각기 다른 패킷 크기로 분할된다.

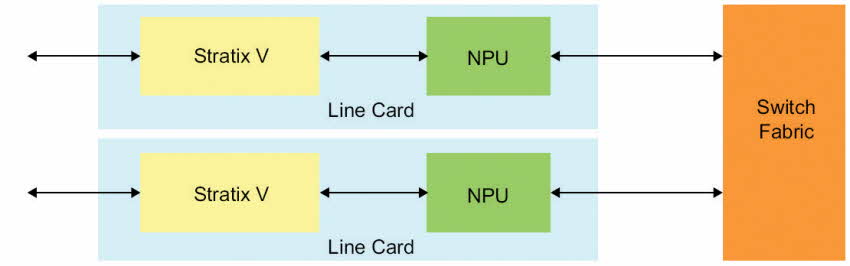

(그림 1)은 다수의 스위치 라인 카드가 NPU(network processing unit)와 연결되고 NPU는 스위치 패브릭과 인터커넥트 되는 스위치 새시 예를 보여준다. 데이터가 진입 프로세서로 들어가서, 스위치 패브릭을 통과해서, 출구 프로세서로 나온다. NPU의 주된 기능은 도착하는 패킷을 검사해서 QoS(quality of service)를 판단하고, (프로토콜에 따라서 다른) 캡슐화 등의 패킷 수정을 수행하고, 네 트워크 보안을 위한 암호화/해독을 수행한다.

트워크 보안을 위한 암호화/해독을 수행한다.

이 스위칭 아키텍처는 근본적인 메모리 한계 때문에 패킷 큐잉 프로세스의 요구를 충족하지 못한다. 스위치가 큐잉 용도로 모든 라인 카드에 걸쳐서 공유할 수 있는 전역 메모리를 포함하는 공유 메모리 아키텍처라 하더라도 대역폭에 대한 요구가 증가함에 따라서 성능이 메모리에 따라서 직접적으로 영향을 받는다. 메모리 한계를 보충하고 ASIC이나 ASSP 플랫폼을 이용한 새로운 라인 카드를 설계하는 것은 비용이 많이 드는 방법이라서 디자이너들은 언제나 스위치 패브릭 아키텍처를 위한 새로운 경제성 있는 대안을 요구해 왔다. 이러한 한계를 극복하는 한 가지 방법이 패킷을 입력 스트림에서 큐잉하는 것인데 이것은 입력 큐잉 모델이라고 하는 기법이다. 이 아키텍처는 패브릭이 오로지 진입 및 출구 NPU 사이에만 전송을 제공하며 통상적인 크로스바 스위치처럼 동작한다. Altera의 Stratix V 디바이스 같은 FPGA는 이러한 구현에 매우 적합하며 가격이 저렴하면서 출시 시간을 단축하는 솔루션을 제공한다.

메모리 한계를 보충하고 ASIC이나 ASSP 플랫폼을 이용한 새로운 라인 카드를 설계하는 것은 비용이 많이 드는 방법이라서 디자이너들은 언제나 스위치 패브릭 아키텍처를 위한 새로운 경제성 있는 대안을 요구해 왔다. 이러한 한계를 극복하는 한 가지 방법이 패킷을 입력 스트림에서 큐잉하는 것인데 이것은 입력 큐잉 모델이라고 하는 기법이다. 이 아키텍처는 패브릭이 오로지 진입 및 출구 NPU 사이에만 전송을 제공하며 통상적인 크로스바 스위치처럼 동작한다. Altera의 Stratix V 디바이스 같은 FPGA는 이러한 구현에 매우 적합하며 가격이 저렴하면서 출시 시간을 단축하는 솔루션을 제공한다.

크로스바 스위칭

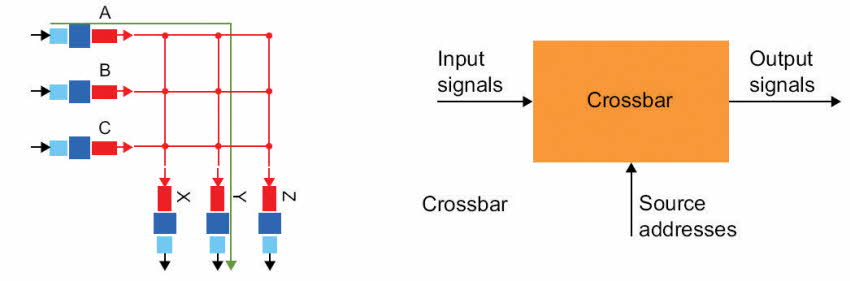

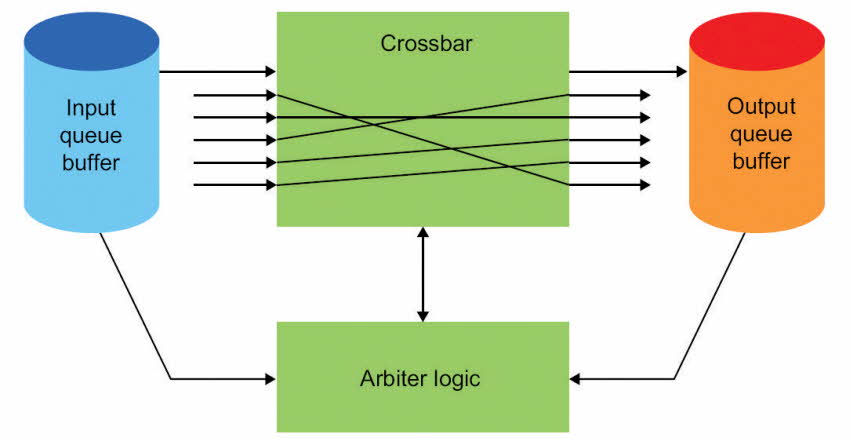

(그림 2)는 기본적인 크로스바(crossbar) 또는 크로스포인트(crosspoint) 스위치를 보여주는 것으로서, 일련의 입력, 그에 상응하는 출력, 입력을 출력으로 맵핑하는 일련의 어드레스를 포함한다.

크로스바는 다음과 같이 분류할 수 있다.

●블로킹

●비-블로킹

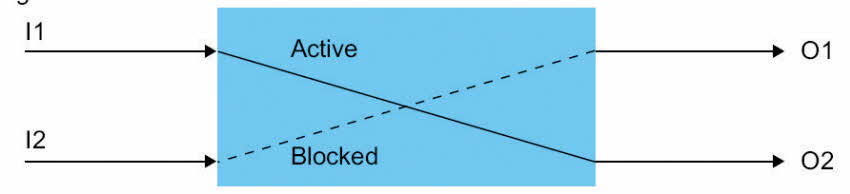

크로스바 스위치를 통해서 한 메시지의 진행이 동일한 출력 포트를 목적지로 하지 않는 다른 메시지에 의해서 중단되었을 때 블로킹이 발생한다. (그림 3)은 크로스바 스위치의 블로킹 아키텍처를 보여주는 것으로, I1에서 O2로의 커넥션이 I2에서 O1로의 경로를 막고 있다.

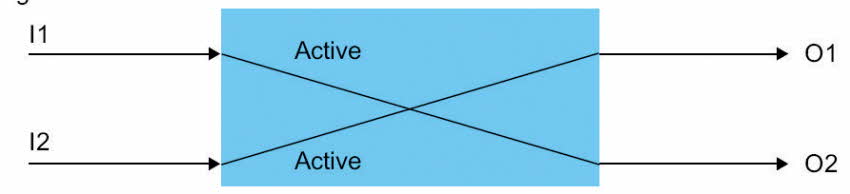

비-블로킹은 커넥션 경로가 어떠한 다른 기존 커넥션과 무관할 때 발생한다. 비-블로킹 스위치는 확장이 불가능하지만 더 높은 성능을 제공한다. 반면에 블로킹 스위치는 스위치 아키텍처 내에서 포트 버퍼링 과제를 용이하게 한다. (그림 4)는 크로스바 스위치의 비-블로킹 아키텍처로서, I1에서 O2와 I2에서 O1으로 트래픽이 동시에 일어날 수 있다.

FPGA 플랫폼은 시스템 디자이너가 단일 스위치 디바이스로 블로킹뿐만 아니라 비-블로킹 아키텍 처 모두를 구현할 수 있는 유연성을 제공한다. FPGA 플랫폼으로 구현하는 크로스바 스위치는 가변 길이 IP 패킷, ATM, SONET 스트림을 비롯해서 다양한 유형의 네트워크 타입으로부터 전송되는 데이터를 지원할 수 있다. 전송되는 패킷 타입에 상관 없이 QoS를 저하시키지 않으며 디자인이나 패킷 타입 요구에 따라서 맞춤화할 수 있다.

처 모두를 구현할 수 있는 유연성을 제공한다. FPGA 플랫폼으로 구현하는 크로스바 스위치는 가변 길이 IP 패킷, ATM, SONET 스트림을 비롯해서 다양한 유형의 네트워크 타입으로부터 전송되는 데이터를 지원할 수 있다. 전송되는 패킷 타입에 상관 없이 QoS를 저하시키지 않으며 디자인이나 패킷 타입 요구에 따라서 맞춤화할 수 있다.

(그림 5)에서 보듯이 외부 중재기 로직을 이용해서 입력 큐 상태에 따라서 QoS를 판단하고 제어한다. 중재기가 크로스바 스위치 내의 한 커넥션을 선택하고 패킷을 네트워크를 통해서 전달할 순서와 우선순위를 결정한다. Stratix V FPGA는 이의 높은 I/O 포트 수에 의해서 이러한 메모리리스(memoryless) 크로스바 스위치 구현에 매우 적합하다. 디자이너에게 QoS를 관리하고 패브릭의  효율을 극대화할 수 있는 다양한 중재 알고리즘을 구현할 수 있는 유연성을 제공한다.

효율을 극대화할 수 있는 다양한 중재 알고리즘을 구현할 수 있는 유연성을 제공한다.

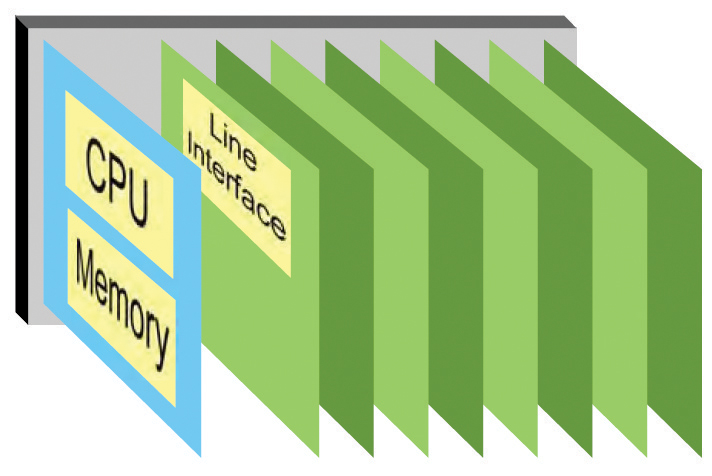

백플레인 스위치 패브릭 (그림 6)은 시스템 백플레인 상에서 스위치 아키텍처를 통해서 다중의 라인 카드를 연결하는 단일 작업을 전문으로 하는 전문적인 형태의 스위치 패브릭이다. 스위치를 통해서 한 카드에서 다른 카드로 데이터 트래픽을 전달한다. 스위치는 새시에 다중의 백플레인이나 다중의 카드를 포함할 수 있다. 라인 카드와 중앙의 스위치 기능이 포괄적인 스위치-라우터 시스템을 이룬다.

라인 카드는 통상적으로 PHY/MAC 기능을 관리하는데, 라인 속도 데이터를 취하고 이를 NPU나 트래픽 관리기의 패킷 프로세싱 모듈로 전송한다. 그런 다음 출력 트래픽은 스위치 라인 카드로 보내지고 스위칭 기능을 통과한다. 스위칭 기능은 큐 관리기와 스위칭 메커니즘으로 이루어져서 데이터 경로를 루팅한다. 스위치 라인 카드가 백플레인 인프라를 통해서 새시 내의 다른 라인 카드들을 연결한다.

백플레인 스위치 패브릭은 네트워크 스위치와 라우터의 일련의 라인 카드 사이에 스위칭을 제공한다. 칩셋으로 구현하면 레이어 2 및 레이어 3 애플리케이션을 위해서 경제적인 가격대의 성능을 제공한다. 하지만 이러한 칩셋은 클라이언트 요구에 따라서 새시를 역동적으로 재구성할 수 있도록 유연하지 못하다. 이러한 칩셋은 또한 프로토콜 라인 레이트가 변화하는 것을 처리하지 못한다. 대부분의 경우에 클라이언트나 전반적인 데이터 패턴에 프로토콜 변화가 있으면 라인 카드를 물리적으로 교체해야 한다.

66개 전이중 트랜시버 포트를 제공하는 Stratix V FPGA는 무손실 메모리리스 스위치를 기반으로 한 이상적인 스위칭 플랫폼을 제공한다. 부분적 재구성을 이용해서 클라이언트 요구를 충족하기 위해 서 라인 카드나 백플레인 스위치를 동적으로 재구성할 수 있다. 동일 새시 내의 다른 클라이언트 동작에 영향을 미치지 않으면서 원격적으로 이러한 구성이 가능하다. 패킷 전송이 허락되면 스위치가 패킷을 해당 출력 포트로 연결시킨다.

서 라인 카드나 백플레인 스위치를 동적으로 재구성할 수 있다. 동일 새시 내의 다른 클라이언트 동작에 영향을 미치지 않으면서 원격적으로 이러한 구성이 가능하다. 패킷 전송이 허락되면 스위치가 패킷을 해당 출력 포트로 연결시킨다.

Stratix V FPGA로 구현되는 스위치는 이의 50MB 임베디드 메모리를 이용해서 제한적인 큐잉 기능을 수행한다. 대부분의 큐잉 기능은 외부 큐 관리기에 의해서 수행된다. FPGA는 높은 포트 애그리게이션과 백플레인 연결성으로 단순한 크로스바 스위치로 동작한다. 패킷의 전송 및 큐잉이 이루어지고 실제 스위칭 기능이 이루어지며 모든 출력 버퍼링은 큐 관리기의 후위에서 이루어진다.

크로스바 스위칭 및 백플레인 스위칭의 구현

Altera의 28nm Stratix V FPGA는 다수의 주요 혁신 기능을 이용해 설계됨으로써 현재 단일 FPGA로 가장 높은 대역폭, 가장 높은 시스템 레벨 통합, 가장 높은 유연성을 제공한다. 크로스바 스위칭이나 백플레인 스위칭 기능의 구현을

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>