WLAN과 같이 복잡하고 빠른 속도의 IP를 자일링스의 디바이스 플랫폼 상에 구현하면 Wi-Fi 인증 통과는 물론 최고 속도로 동작이 가능하다.

WLAN과 같이 복잡하고 빠른 속도의 IP를 자일링스의 디바이스 플랫폼 상에 구현하면 Wi-Fi 인증 통과는 물론 최고 속도로 동작이 가능하다.

아그네스 페인(Agnes Fain) / Wipro-NewLogic 시니어 디자인 엔지니어

울프강 머크(Wolfgang Meryk) / Wipro-NewLogic 시니어 제품 마케팅 매니저

자료 협조 : 자일링스코리아

IEEE 802.11 무선 LAN 컨트롤러와 같이 복잡하면서도 고속의 IP 코어를 디자인하고 있는 모든 기업들은 설계 동작을 검증하고 높은 품질의 디자인을 구현하는데에 따른 여러 과제에 직면해 있다. 테스트 칩은 IP를 실리콘 상에서 검증하여 확인할 수 있기 때문에 중요하지만, 테스트 칩 단계에서는 오직 한가지 포인트의 하드웨어 디자인 상태만을 확인할 수 있다. 더욱이 IP는 다양한 컨피규레이션 및 애플리케이션을 지원할 수 있도록 유연해야 한다.

WLAN은 여전히 마켓과 연관된 새로운 사양(Wi-Fi, ETSI/FCC)들이 추가되고 있기 때문에 이들 중 일부가 요구되거나 혹은 최소한의 하드웨어 변경으로 혜택을 얻기 위해서는 유연성 및 업그레이드 성능에 대한 추가적인 요건이 필요하다.

Wipro-NewLogic은 이러한 문제를 해결하기 위해 FPGA 기반 플랫폼을 검토하기로 결정했다. 이 회사는 WLAN IP: WiLD a/b/g 명칭을 반영하기 위해 개발 제품을 WiLDSYS 보드로 명명했다.

Wipro-NewLogic은 이 디자인을 위해 몇 가지 핵심 요건을 정리했다. 첫 번째는, 최대 속도(802.11a 및 802.11g를 위한 54Mbps 무선 데이터 전송속도)로 동작하는 WLAN IP를 지원해야 한다는 것이다. 다음은 FPGA와 ASIC에서 모두 사용할 수 있는 단일 데이터베이스가 필요하다는 것. 세 번째로는, ASIC 타겟에도 적용할 수 있도록 FPGA 타겟에서의 테스트 결과 및 버그 조정이 상당히 높은 수준의 안정성을 가져야 한다는 것이다. 마지막으로는 미래에 새로운 인터페이스로 대체할 수 있도록 FPGA의 프로그래머빌리티를 활용하고, 외부 부품 수를 최소화하기 위해 FPGA 상의 호스트 및 모든 무선장치를 외부 인터페이스로 구현할 수 있어야 한다는 점이다. 이 프로젝트가 진행되는 동안 FPGA 플랫폼은 이러한 목표에 모두 부합했으며, WiLDSYS 보드를 위한 완벽한 Wi-Fi 인증 또한 획득할 수 있었다.

그렇다면 WiLDSYS 디자인 개괄 및 FPGA 디바이스 선택부터 출발해 보자.

WiLDSYS 개괄

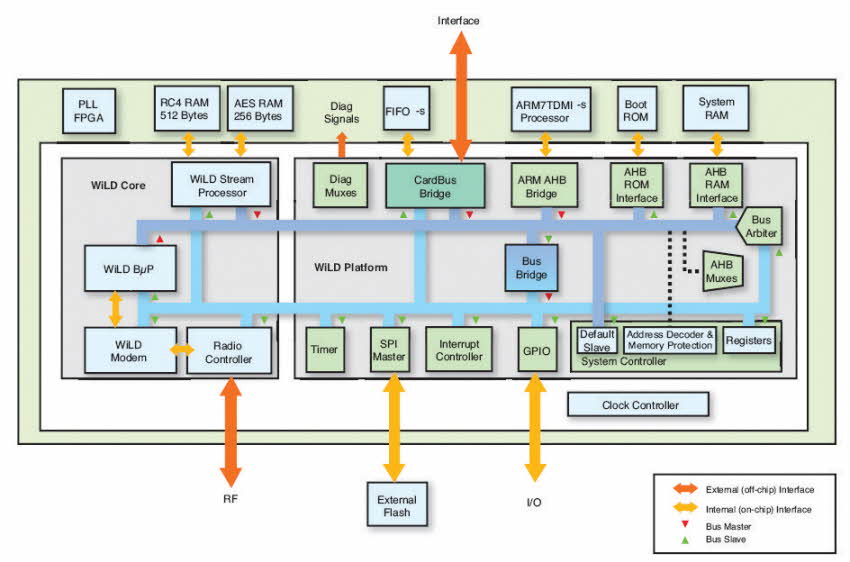

(그림 1)은 실제 디자인에 구현한 WiLDSYS 플랫폼의 블록 다이어그램을 나타낸 것이다. 좌측의  WiLD 코어는 802.11 a/b/g MAC(Media-Access Controller)과 모뎀 하드웨어로 이루어져 있다. 이 MAC의 기능은 WiLD 버스트 프로세서와 버퍼 매지니먼트 유닛/DMA 엔진, WiLD 스트림 프로세서에 걸쳐 나뉘어 동작하며, RC4 및 AES 암호화를 다룬다. 두 블록 모두 중앙의 AHB(Advanced High-Performance Bus) 상의 마스터로 운영되며, 타이밍은 크게 중요하지 않다.

WiLD 코어는 802.11 a/b/g MAC(Media-Access Controller)과 모뎀 하드웨어로 이루어져 있다. 이 MAC의 기능은 WiLD 버스트 프로세서와 버퍼 매지니먼트 유닛/DMA 엔진, WiLD 스트림 프로세서에 걸쳐 나뉘어 동작하며, RC4 및 AES 암호화를 다룬다. 두 블록 모두 중앙의 AHB(Advanced High-Performance Bus) 상의 마스터로 운영되며, 타이밍은 크게 중요하지 않다.

WiLD 모뎀은 802.11 a/b/g 표준을 위한 CCK/DSSS 및 OFDM 시그널 프로세싱 기능을 포함하고 있다. 시그널 프로세싱은 FPGA에 매핑이 쉽지 않은 ASIC을 위해 설계되었으며, 우리는 이 문제 및 솔루션에 대해 이후 보다 자세히 설명할 것이다.

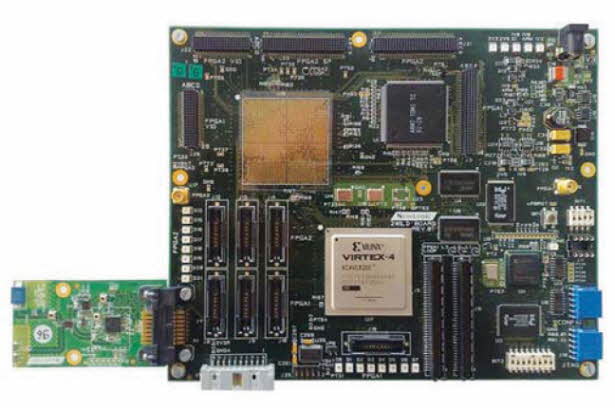

또한 레이어 2 MAC 소프트웨어로 동작하는 완벽한 ARM7 기반 프로세서 플랫폼도 가지고 있다. 우리는 이 소프트웨를 통해 액세스 포인트와 스테이션 모드를 모두 지원한다. 한편 FPGA 보드 상에서 ARM7 칩을 바깥쪽에 배치함으로써 ARM 라이센스가 없는 고객들도 이 보드를 사용할 수 있도록 했다. 또한 FPGA 내부에서 제공하고 있는 메모리 용량을 초과하는 애플리케이션을 위해 외부에 SRAM을 추가했으며, 뿐만 아니라 부팅을 위한 플래시 메모리 디바이스도 제공한다. 모든 외부 인터페이스와 디버그를 위해 FPGA I/O에 액세스할 수 있도록 충분한 수의 헤더 커넥터를 배치했다. 향후 업그레이드 기능을 위해, 지금까지는 사용하지 않아서 가지고 있지 않았던 2세대 FPGA 풋프린트도 추가했다. (그림 2)는 WiLDSYS FPGA 보드 사진이다.

FPGA 선택

이 디자인을 위해 우리는 자일링스 버텍스-4(Virtex®-4) FPGA를 사용했다. 이 디바이스를 선택한 이유는 DSP 블록을 비롯해 내부 메모리, 유연한 I/O 패드, 고성능 클럭킹 지원과 같은 고속의 여러 특화된 리소스를 제공하기 때문이다. 이미 WiLD IP가 700K 게이트에 해당하는 플랫폼을 포함하고 있기 때문에 이 사이즈에 적합한 버텍스-4 LX200 FPGA를 이용했다. (표 1)에는 이 디자인에 사용된 항목들을 나타내었다. 버텍스-4 FPGA는 최대 500MHz의 클럭 속도를 지원한다. Wipro-Newlogic은 자사의 WLAN 무선 칩에서 240MHz로 동작하는 고속의 커스텀 시리얼 인터페이스를 구현할 수 있는 속도가 필요했다. ASIC과 FPGA 타겟 모두를 위한 단일 데이터베이스를 사용하는 것 또한 목표 중 하나였기 때문에 FPGA 리소스를 가장 적절하게 활용하기 위한 최적화 작업을 할 필요없이 ASIC 코드를 FPGA로 매핑해야만 했다.

버텍스-4 FPGA는 최대 500MHz의 클럭 속도를 지원한다. Wipro-Newlogic은 자사의 WLAN 무선 칩에서 240MHz로 동작하는 고속의 커스텀 시리얼 인터페이스를 구현할 수 있는 속도가 필요했다. ASIC과 FPGA 타겟 모두를 위한 단일 데이터베이스를 사용하는 것 또한 목표 중 하나였기 때문에 FPGA 리소스를 가장 적절하게 활용하기 위한 최적화 작업을 할 필요없이 ASIC 코드를 FPGA로 매핑해야만 했다.

일반적으로 ASIC 코드는 보다 긴 복합적인 경로를 사용하기 때문에 FPGA의 최대 속도와 해당 디자인의 최고 클럭 주파수 간의 마진이 필요했다. 자일링스는 버텍스-4 FPGA의 시그널-프로세싱 블록, 특히 멀티플라이어를 획기적으로 향상시켰다. DSP48이라고 명명된 이 전용 블록은 곱셈과 덧셈에 최적화되어 있다. 우리는 FPGA에서 80MHz로 동작하는 802.11 a/g 모뎀을 구동시키기 위해 DSP48 리소스의 이점을 활용했다.

또한 글로벌 클럭 라인의 활용 가능성은 새로운 가능성을 부여했다. 버텍스-4 LX200 FPGA는 32개의 글로벌 클럭 버퍼를 가지고 있으며, 이 중 8개는 특정 FPGA 영역에 제한되어 있지 않다. 따라서 이러한 8개의 클럭 버퍼와 연결된 플립-플롭을 FPGA 내의 어느 곳에든 배치할 수 있기 때문에 디자인 상에서 매핑 및 P&R을 위한 더 많은 옵션을 얻을 수 있었다.

단일 데이터베이스 과제

FPGA 상에서 수행된 검증확인은 이 결과가 오직 ASIC 디자인을 대별할 때에만 유의미하다는 점을 알 수 있었다. FPGA에 매핑된 코드는 ASIC 코드에 추가된 새로운 기능이나 모든 버그 교정을 반영해야 한다. 반대로 FPGA 검증확인이 이뤄지는 동안 수행된 모든 교정 내용은 이후 ASIC 디자인에 반영되어야 하며, ASIC 검증환경을 이용해 완벽하게 시뮬레이션되어야 한다. 우리는 초기 단계부터 FPGA와 ASIC을 모두 타겟하는 단일 디자인 데이터베이스를 유지할 때만 효율적인 방법으로 이 모든 것들을 처리할 수 있다는 것을 직시하고 있었다. 따라서 신속하게 여러 과제들을 해결하고 구현할 수 있었다.

일부 경우의 솔루션에서만 ASIC 코드가 수정되었다. 우리는 자체 OFDM 모뎀에 버텍스-4 디바이스의 80MHz 타이밍과 맞지 않는 로직 경로를 가지고 있었다. 따라서 추가 플립-플롭을 삽입하여 복합 경로를 분리하였다. 이로 인해 전반적인 모뎀의 레이턴시가 증가했지만 여전히 충분한 마진을 가지고 있었기 때문에 문제가 되지는 않았다. 우리는 FPGA 상에서 타이밍을 맞추고 ASIC 타겟 상에서 풀-리그레션(Full Regression) 테스트를 구동한 다음 이러한 수정내용을 다시 ASIC 데이터베이스에 반영했다.

한편 완화된 타이밍으로 인해 ASIC 합성 툴이 보다 적은 수의 버퍼와 더 작은 복합 셀을 사용하기 때문에 ASIC 합성 이후 오히려 수정된 디자인으로 구현한 ASIC에서 몇몇 이득을 얻을 수 있었다.

클럭 컨트롤러는 가장 중요한 ASIC 블록 중 하나이며, 또한 FPGA로 매핑하기 가장 어려운 부분 중 하나다. 결국 FPGA 구현만을 위한 고유의 블록을 생성해야만 했다. 우리는 각각의 타겟에 적합한 블록을 선택하기 위해 ASIC과 FPGA를 위한 합성 스크립트를 설정했다.

우리는 또한 저전력 애플리케이션을 위한 WiLD IP를 개발하고자 했기 때문에 별도의 전력 도메인과 함께 설계에 클럭 게이팅을 지원할 수 있도록 추가했다. FPGA에서 이러한 2가지 기능을 모두 구현할 수 없다는 것을 알았지만, 최소한 클럭 및 전력 도메인의 컨트롤 및 스위칭은 포함하고자 했다. 버텍스-4 LX200 FPGA의 8개 영역의 프리 글로벌 클럭 버퍼로는 ASIC의 모든 클럭 주파수와 클럭-게이팅 기능을 커버할 수 있는 충분한 리소스를 충당하지 못했다. 따라서 시스템에 맞는 정확한 기능에 필요한 클럭 게이팅만 FPGA에 구현하기로 하고 단지 전력소모 절감을 위한 클럭 게이팅은 제외했다.

클럭 트리를 쉽게 만들기 위해 Synplify Pro FPGA 합성 툴에서 지원하는 클럭 게이팅 기능을 사용했다. 이 합성 툴은 클럭 라인에서 게이팅 조건을 제거하고 이를 데이터 입력 혹은 플립-플롭 인에이블 입력 상에 배치한다. 우리는 이 로직 출력이 여전히 버텍스-4 FPGA의 고속 및 낮은 스큐의 글로벌 클럭 라인을 사용하여 라우팅될 수 있도록 하기 위해 클럭 게이팅에 BUFG, BUFGCE 버퍼를 사용했다. BUFGMUX 리소스는 액티브 모드 및 저전력 클럭 사이에서 완벽한 멀티플렉싱을 제공했다.

WiLD 디자인에 서로 다른

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>