USB 인터페이스는 전 세계 공통의 인터페이스로 확고히 자리를 잡았다. 이 글은 FPGA나 ASIC 기반의 시스템에서 효율적인 고속 USB 2.0 인터페이스를 구현하기 위해 활용할 수 있는 가능한 설계 방법을 모색한다.

글 | 흐리다야 발사라주 (Hridya Valsaraju)

고팔라크리슈난 비자야쿠말(Gopalakrishnan Vijayakumar) 수석 애플리케이션 엔지니어

싸이프레스 세미컨덕터(Cypress Semiconductor)

USB(Universal Serial Bus)는 호스트 컴퓨터와 주변기기 간의 연결을 플러그 앤 플레이 기능을 통해 더 빠르고 편리하게, 더 많은 기기를 연결할 수 있도록 발전해 왔다. 주위만 둘러보더라도 많은 장치들이 USB 인터페이스를 가지고 있음을 확인할 수 있다. USB는 호스트 컴퓨터에 인터페이스를 필요로 하는 모든 제품의 1차 옵션으로 고려되고 있다. Low, Full, High에서 Super speed까지 USB가 제공하는 다양한 대역폭으로 인해 이제는 산업 및 의료 장비는 물론, 광범위한 컴퓨터 주변기기에 USB가 채용되고 있다. USB가 제공하는 처리량도 하드디스크드라이브(HDD)나 스캐너 와 같은 고대역폭 애플리케이션에서도 충분하다. 사실 USB는 키보드와 마우스, PDA, 게임패드, 조이스틱, 스캐너, 디지털 카메라, 프린터와 같은 대부분의 컴퓨터 주변기기를 위한 표준 상호연결 방법으로 확고히 자리를 잡았다.

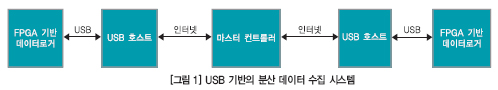

간단한 컴퓨터 주변기기 디바이스와는 별도로, 고속(high speed) USB 인터페이스의 추가로 더 큰 이점을 가질 수 있는 폭넓은 FPGA 기반의 애플리케이션이 존재한다. 디지털 시그널 오실로스코프(DSO), ECG, 비디오카메라, 데이터 수집(DAQ) 시스템 등은 그와 같은 몇 가지 시스템에 해당한다. 디바이스에 USB 인터페이스를 추가하면, 디바이스의 기능을 대폭 확장할 수 있다. 예를 들어, DSO와 ECG 같은 데이터 기록 시스템의 경우 획득한 데이터는 그림 1과 같이 인터넷을 통해 차례로 호스트 머신에 실시간으로 전송할 수 있다. 호스트에서 USB를 통해 데이터 로거 디바이스를 연결하는 원격 데이터 로깅과 같은 애플리케이션에서도 인터넷을 통해 USB 호스트에 연결될 수 있는 마스터 호스트 머신에서 디바이스를 원격으로 조정할 수 있게 설정할 수 있다.

이 글은 FPGA나 ASIC 기반의 시스템에서 효율적인 고속 USB 2.0 인터페이스를 구현하기 위해 활용할 수 있는 가능한 설계 방법을 모색한다.

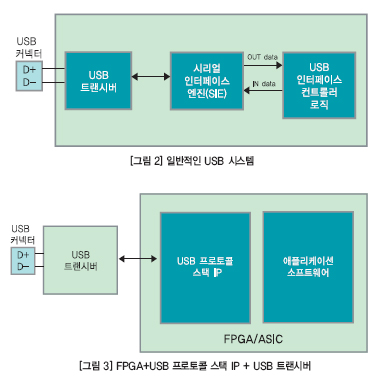

USB 인터페이스를 FPGA나 ASIC 기반의 시스템에 통합할 수 있는 다양한 방법을 찾아보기 위해 우리는 일반적인 USB 시스템이 어떻게 작동하는지 이해할 필요가 있다. 일반적인 USB 시스템은 그림 2처럼 트랜시버, 시리얼 인터페이스 엔진(SIE), 인터페이스 컨트롤러로 구성된다.

트랜시버는 USB 프로토콜의 물리계층(PHY)을 구현한다. 또한 트랜시버는 호스트와 디바이스 간의 데이터 링크의 두 종단을 형성한다. USB 트랜시버는 차동 및 싱글엔드 출력을 둘 다 갖는다. SIE는 시리얼 데이터를 인코딩/디코딩하고, 비트 스터핑(bit stuffing), 오류 정정, 그리고 USB가 요구하는 시그널 차원의 가사작업을 수행한다. 또한 USB 인터페이스로부터 또는 USB 인터페이스로 패러럴 데이터를 전송한다.

SIE는 엔드포인트 제어(control endpoint)를 통한 요청을 호스트에 응답함으로써 높은 수준의 USB 프로토콜을 구현해야 하는 지능형 마스터로 인터페이스 되어야 한다. 또한 마스터는 디바이스의 기능에 필요한 애플리케이션 차원의 작업을 수행한다. 여기서 우리는 USB 인터페이스를 FPGA나 ASIC 기반의 시스템에 추가할 수 있는 3가지 서로 다른 방법에 대해 논의한다.

외부 트랜시버와 함께 USB 프로토콜 스택 IP 사용

맨 첫 번째 방법으로, FPGA나 ASIC 내에 SIE를 구현할 수 있다(그림 3 참조).

SIE IP(Intellectual Property)가 수행해야만 할 주요 기능은 데이터 인코딩 및 디코딩, CRC 생성 및 오류 정정, 비트 스터핑, 패킷 ID 생성, 시리얼에서 패러럴 및 패러럴에서 시리얼로의 변환이다. 이 IP는 직접 개발하거나 제3의 업체로부터 구매할 수 있다. FPGA는 높은 수준의 USB 프로토콜의 구현을 수행해야만 한다. 트랜시버 IC는 싸이프레스 TX2UL 트랜시버 칩과 같은 외부의 칩을 사용할 수 있다. 트랜시버는 USB 2.0 인증 제품이며 트랜시버 매크로셀 인터페이스(UTMI) 사양을 준수한다. Dplus 라인 상의 1.5 kΩ 풀업(pull-up)을 포함한 필요한 모든 종단은 칩에 내장돼 있다.

이러한 접근법의 장점은 외부 하드웨어가 최소한으로 필요하다는 것이다. 반면, 이런 접근법의 단점은 복잡한 USB 스택 IP 개발로 인해 엔지니어링 자원은 물론, 시간을 잡아먹게 된다. 또한 SIE IP의 구현, 더 높은 수준의 프로토콜 및 애플리케이션 기능은 상당한 양의 FPGA 자원을 차지한다. 제3의 IP 사용은 비용이 많이 들 수도 있다.

SIE와 트랜시버를 통합한 USB 브리지 IC의 사용

FPGA 설계로 USB 인터페이스를 통합하는 또 다른 방법은 트랜시버는 물론, 외부 시리얼 인터페이스 엔진 IC를 연결하는 것이다(그림 4 참조).

여기서 FPGA는 높은 수준의 USB 프로토콜 레이어를 구현해야만 한다. USB 호스트로부터 받은 모든 명령은 SIE에 의해 FPGA에 전달된다. 또한 FPGA는 이러한 명령에 적절히 대응하기 위한 로직이 포함될 필요가 있다. 예를 들면, 순차탐색(emum

eration) 과정에서 USB 디바이스는 디스크립터를 위해 요청하는 호스트로부터 명령을 받을 것이다. 이러한 구현에서 외부 하드웨어, 즉 트랜시버 및 SIE는 패킷을 수신할 것이며, 명령이 수신된 것을 인터럽트를 통해 FPGA에 통지한다. 그럼 FPGA는 디바이스가 호스트로부터 GET Descriptor 명령을 받은 것을 이해하기 위해 SIE에 등록한 것을 읽어낼 필요가 있다. 그런 다음 SIE에 올바른 디스크립터들을 보낼 필요가 있다.

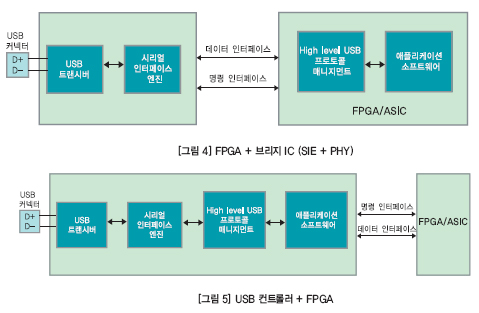

외부 트랜시버와 SIE IC를 사용하는 것보다는 트랜시버와 내장 SIE를 가지고 있는 싸이프레스 Mobl-USB 같은 USB 브리지 IC를 사용하는 것이 유리할 수 있다. 컨트롤러는 Control Endpoint 0 뿐만 아니라, 최대의 유연성과 처리량을 위해 2KB FIFO 영역을 공유하는 2개의 더블 버퍼링 속도를 지원하는 엔드포인트를 가지고 있다.

이러한 구현의 주요 장점은 이런 복잡함의 절반이(즉, 시그널 레벨 프로토콜 관리) FPGA 밖으로 옮겨간다는 것이다. 그러나, 이런 시나리오에서도 FPGA 자원의 일부는 여전히 높은 수준의 USB 프로토콜 구현을 위해 이용되어야 한다. 이 경우에 의사결정은 필요한 외부 하드웨어 비용 vs 저장된 FPGA 자원의 양을 분석함으로써 내려져야 한다.

FPGA와 USB 컨트롤러의 사용

마지막 방법은 FPGA에 완벽한 USB 컨트롤러를 연결하는 것이다(그림 5 참조). 이 경우에 모든 USB 프로토콜 수준의 관리는 FPGA 밖에서 이뤄질 것이다. 전용 USB 컨트롤러 IC는 PHY, SIE 및 프로토콜 제어 로직이 포함돼 있다.

컨트롤러는 설정 가능한 엔드포인트의 수, FIFO 크기에 대한 유연성을 제공할 수 있으며, 심지어 높은 수준의 USB 프로토콜 관리를 처리하는 마이크로컨트롤러가 포함될 수 있다. 이러한 주변기기 컨트롤러는 일부 애플리케이션 수준의 기능을 처리하는 능력을 포함할 수 있으며, 그로 인해 이러한 기능을 수행하려는 필요로부터 FPGA나 ASIC를 자유롭게 한다. 만일 주변기기 컨트롤러가 RAM을 기반으로 한 아키텍처를 포함할 경우, 개발자에게 인-필드 펌웨어 업그레이드의 유연성을 제공한다.

FPGA는 이제 이 칩에 연결하기 위한 로직만을 유지할 필요가 있다. USB 컨트롤러와 FPGA 간의 인터페이스는 SPI, I2C, 혹은 HPI 등의 표준 인터페이스 중 하나가 될 수 있다. 또한 USB 컨트롤러 IC에 지정되어 있는 커스텀 인터페이스일 수 있다.

싸이프레스 FX2LP는 FPGA 또는 ASIC 기반의 시스템에 USB를 통합하기 위한 개발기간을 단축할 수 있는 전용 주변기기 컨트롤러 칩이다. FX2LP는 FPGA 기반의 시스템과 함께 간단한 상호작용을 가능하게 해주는 간단한 “슬레이브 FIFO” 인터페이스를 포함하고 있다. 슬레이브 FIFO 인터페이스는 FX2LP의 4K FIFO 영역에 데이터를 읽고 쓸 수 있는 간편한 슬레이브 읽기(Slave Read) 및 슬레이브 쓰기(Slave Write) 시그널로 기능한다.

ASIC 기반의 시스템으로 인터페이스하기 위한 싸이프레스의 FX2LP는 ASIC이 통신용으로 보유하고 있는 어떤 표준 인터페이스를 위한 인터페이스 파형을 생성할 수 GPIF 또는 일반적인 프로그래머블 인터페이스 로직을 포함하고 있다. 또한 GPIF는 PROM 혹은 프로세서와 같은 별도의 구성 칩에 대한 필요성을 없애주면서 USB 인터페이스를 통해 FPGA를 설정하는 옵션을 제공한다. USB를 통해 FPGA를 설정해도 보드에서 JTAG 헤더를 제거할 수 있다. 따라서, 범용의 전용 USB 컨트롤러는 보드 크기와 비용을 줄임으로써 데이터 루트 그 이상의 역할을 할 수 있다.

이 글에 언급된 3가지 모든 설계 기법은 장점과 단점이 모두 있다. 따라서 비용, 보드 공간, FPGA 자원 사이에 허용되는 장단점을 신중하게 분석하고 선택해야 한다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>