글 | 데이비드 A. 라이스(David A. Rice), 기술 디렉터

크리티컬 링크 (Critical Link), LLC

조셉 쿰즈(Joseph Coombs), 애플리케이션 엔지니어

TMS320C6000™ 디지털 신호 처리기

텍사스 인스트루먼트

문제 : 여러 가지 애플리케이션을 위해 확산 스펙트럼(spread-spectrum) 무선 트랜시버를 개발해야 했던 한 고객이 크리티컬 링크를 찾아왔다. 그 고객은 이미 신호를 변조 및 복조하는데 사용할 알고리즘을 개발해 놓은 상태였지만, 그것을 전체적인 시스템으로 조합하는데 필요한 리소스와 전문지식이 부족했다. 그 고객은 소프트웨어 정의 무선(software defined radio, SDR) 시스템이 발휘하는 극한의 유연성을 활용하고 싶어했다.

플랫폼

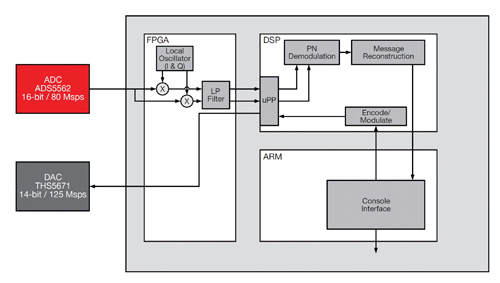

크리티컬 링크는 SDR의 기초로 MityDSP-L138F 시스템-온-모듈을 사용하기로 했다. 처리 능력(processing horsepower) 관점에서 잘 맞을 뿐 아니라, 고객에게는 선행 설계(up-front design) 비용을 상당량 절감해줄 것이기 때문이다. MityDSP-L138F 모듈에는 TI가 구현한 OMAP-L138 DSP+ARM짋 프로세서가 결합돼 있다. 이것은 456 MHz ARM9™ 프로세싱 코어와 456 MHz TMS320C674x DSP 코어를 통합하고 있다. 또한 이 모듈에는 자일링스 스파르탄짋-6 LX16 FPGA와 NAND 및 NOR 플래시, DDR2 메모리가 포함돼 있다.

프로토타입 용도로, TI의 무선용 고속 ADC 및 DAC 평가 키트가 사용됐다. 60 MHz 샘플 주파수에서 변환할 수 있는 데이터 컨버터가 필요했다.

A/D 컨버터의 경우, TI의 ADS5562가 선택됐다. 이것은 80 Msps에서 16 bit의 정밀성으로 변환한다. 확산 스펙트럼 무선은 주위 노이즈에서 신호를 끌어내야 하기 때문에, 높은 다이내믹 레인지(dynamic-range)가 이러한 무선에서는 매우 중요하다.

DAC의 경우, TI의 14 bit, 125 Msps 차동 전류 출력 DAC인 THS5671을 선택했다. 프로젝트를 위해 고객은 이 시스템에 프론트엔드 설계를 제공했다. 설계는 다음 페이지에 나와 있다.

데이터 이동 문제

수많은 DSP 기반 애플리케이션들은 고속 데이터 전송으로 시스템이 데이터를 획득, 처리할 수 있거나 외부 디바이스로 데이터를 전송할 수 있기를 요구하고 있다. 일반적으로 DSP에는 비동기식 어드레스/데이터 버스가 들어 있어서 프로세서가 외부 디바이스에 읽기와 쓰기를 할 수 있다. 이러한 인터페이스는 낮은 속도에서 데이터를 이동시키는데 적합한 편이지만 고속에서는 병목현상이 일어날 수 있다.

OMAP-L138 DSP+ARM 프로세서는 주소/데이터 버스로 하여금 외부 메모리 인터페이스 A(EMIFA)를 호출하게 한다. 이 EMIFA는 외부 메모리 또는 디바이스의 어드레싱을 허용한다.

비동기식으로 포함된 여러 가지 제어 핀들을 통해 다양한 대기-상태와 전송 폭 등이 가능하다. 이 인터페이스는 매우 일반적인 용도이기 때문에, 각각의 트랜잭션은 다수의 클록 사이클로 완성될 수 있다. 예컨대, 최소한의 읽기 사이클에는 16 bit 당 3개 사이클이 필요할 것이다. 100 MHz에서 EMIFA를 실행하면, 그 외 어떤 것도 그 버스에서 진행 중인 것이 없다고 가정했을 때 66 MBytes/s의 데이터 전송 속도를 기대할 수 있다. 그 버스에 읽기와 쓰기를 끼워 넣으면 이것이 크게 줄어든다. 추가 턴어라운드 사이클이 추가되어야 하기 때문이다.

OMAP-L138 프로세서에도 범용 병렬 포트(Universal Parallel Port, uPP)라는 좀더 특정한 목적의 인터페이스가 들어 있다. 이 인터페이스는 프로세서의 메모리 안팎으로 많은 양의 데이터를 계속 이동시키도록 특별히 고안된 것이다. 이 uPP는 클록 사이클 당 하나의 데이터 워드(8 또는 16 bit)를 클록할 수 있다(또는 더블 데이터 속도에서는 클록 당 두 개. 그러나 클록 속도는 빠른 만큼 절반이 된다). 이 uPP 클록 속도는 프로세서 클록 속도의 절반까지 가능하다. 300 MHz에서 실행되는 OMAP-L138 프로세서의 경우, 이 uPP 클록이 75 MHz까지 가능하다. 그러면 최대 150 MBytes/s의 처리량이 가능해진다.

OMAP-L138 프로세서에는 사실 두 개의 uPP 인터페이스가 들어 있는데, 각각을 독립적으로 구성할 수 있다. 우리의 애플리케이션에서는 이것을 통해 한 포트는 전송용으로, 다른 한 포트는 수신용으로 설정할 수 있었고, 그렇게 싱글 버스에서 나타날 수 있는 경합을 제거할 수 있었다.

하드웨어 관점에서 uPP 인터페이스는 제법 간단한 동기식 데이터 인터페이스다. 여기에는 유효한 데이터와 시작/대기 조건들을 표시하는 클록 핀과 데이터 핀, 여러 개의 제어 핀이 들어 있다. 사실, 이 인터페이스는 몇몇 병렬 ADC 및 DAC와 함께 사용될 수 있다.

아키텍처

SDR에는 DSP를 오가는 고속 데이터 이동이 필요하기 때문에, 우리는 uPP 포트를 이용해 FPGA 인터페이스를 구현하기로 했다. 한 포트는 인터페이스의 전송용으로, 다른 한 포트는 수신용으로 사용한다. 이 프로세싱 시스템은 사실상 동시에 전송과 수신이 가능하다. 물론, 이것은 시스템 요건이 아니었다. 이러한 기능의 장점은 트랜스미터나 리시버를 루프백하여 꽤 많은 테스트와 디버깅을 할 수 있었다는 것이다.

10 MHz 반송파의 경우, 이런 종류의 변조에 필요한 프로세싱의 속성으로 인해 OMAP-L138 프로세서에서 DSP의 프로세싱 모두를 하는 것은 지나치다. 좀더 느린 애플리케이션의 경우, DSP만으로 데이터 속도를 관리할 수 있지만 고객은 더 높은 속도에서 데이터를 전송할 수 있기를 바랐기 때문에 프로세싱 작업들 중 일부에서 FPGA의 도움을 받아야 했다.

FPGA는 매우 높은 주파수에서 반복적인 작업에 특히 뛰어나다. 그래서 FPGA에서 초기 복조 및 베이스밴딩(base-banding) 처리를 하기로 했다. 이것을 통해 데이터의 10분의 1을 줄일 수 있고 데이터 속도를 DSP로 줄일 수 있다. 전송 측면에서 DSP는 최종 RF 신호를 미리 계산할 수 있어, 페이로드 데이터의 인코딩에 약간의 시간만 소요된다. 이 때문에 FPGA는 그저 uPP 포트에서 DAC로 전송 파형 데이터만 전달하면 된다. 이것은 사실상 FPGA를 사용하지 않고도 할 수 있었겠지만, 도움이 필요한 경우를 대비해 경로에 FPGA를 넣어 시스템 설계를 했다.

FPGA는 사인/코사인 룩업 테이블(lookup table, LUT)이 듀얼 포트 RAM에 들어 있다. 이것은 리시버를 위해 로컬 오실레이터 신호를 합성하는데 사용된다. FPGA의 곱셈기/누적기는 필요할 때 그 신호를 복조하는데 사용된다.

전송 프로세싱 체인

전송 프로세스는 ARM 프로세서의 소프트웨어가 전송을 위해 메시지 패킷을 DSP로 발신할 때 시작된다. DSP는 이 데이터를 확산 스펙트럼 변조 시퀀스로 인코딩하고, 미리 계산하여 변조시킨 사인파 LUT로 인덱싱을 한다. 그런 다음 DSP는 uPP의 빌트인 DMA 엔진을 이용하여 DMA 전송을 설정하고 DSP 메모리의 데이터를 DAC로 전송한다. FPGA는 중개 역할을 하며 프로그래머블 클록을 DAC와 uPP에 제공하여 전송 샘플 레이트를 설정한다.

수신 프로세싱 체인

수신 프로세스는 지속적으로 실행된다. ADC 샘플들은 FPGA로 클록된다. 여기에서 데이터는 입력 샘플들을 쿼드러처 사인 및 코사인 파형과 곱하여 베이스밴드 되고 통합되어, 줄어든 데이터 속도에서 인페이즈(in-phase) 및 쿼드러처 샘플들을 DSP에 제공하게 된다. 이러한 샘플들은 uPP DMA 엔진에 의해 DSP 메모리로 DMA 된다. 여기에서 DSP는 DSP 확산 스펙트럼 복조를 위해 남아있는 프로세싱 단계들을 수행한다. 신호가 복조되면, 그로 인한 데이터 패킷이 TI의 DSPLink 인터프로세서 커뮤니케이션 라이브러리를 이용해 ARM짋 프로세서로 다시 전송된다. ARM 소프트웨어는 디코딩된 데이터를 수신하고 그것을 명령 인터페이스를 통해 사용자에게 제시하게 된다.

FPGA를 이용해 리시버용 초기 베이스밴딩을 수행하면, DSP의 프로세싱이 완화되면서 남아 있는 복조와 디코딩 모두가 원활하게 수행된다. 입력 신호의 샘플 레이트가 이 시스템에서 60 MHz 보다 크게 낮은 경우, DSP를 믿고 FPGA의 도움 없이 베이스밴딩을 실행할 수 있다.

이 시스템의 초기 작업은 LF 대역에서 반송파 주파수를 사용했다(수 십 또는 수 백 kHz). 이 초기 구현에서 FPGA는 단순히 데이터를 DSP로 넘겨주는 것이었고, 그러면 DSP가 모든 복조 기능을 수행했다. 그 효과는 뛰어났지만, 높은 샘플 레이트가 필요한 애플리케이션에는 불충분했다. FPGA에서 베이스밴딩을 수행함으로써, 최대 샘플 레이트에서 디지털로 베이스밴딩과 필터링을 할 수 있고 그것을 통해 언더 샘플링으로는 불가능한 방식으로 시스템의 노이즈 성능을 개선할 수 있다.

결론

이 프로젝트의 최종 결과는 다양한 애플리케이션에서 콘셉트 증명(proof-of-concept)으로 사용돼온 프로토타입 시스템이었다. 이 시스템의 성능은 이상적인 확산 스펙트럼 무선의 이론상 성능과 비교했을 때 꽤 훌륭했다. TI의 OMAP-L138 DSP+ARM짋프로세서와 FPGA의 조합은 뛰어난 성능의 경제적인 솔루션을 가능하게 한다. DSP에서 FPGA로의 오프로딩 프로세싱을 통해 이 시스템은 저비용, 저전력 프로세서를 이용한 구축이 가능해졌고, GHz 등급의 DSP로 전체 작업을 할 필요가 없어졌다. uPP 인터페이스는 단순한 FPGA 인터페이스를 가능하게 해주고, DSP에서 이용 가능한 다른 인터페이스들을 사용하는 것보다 성능상 이점이 뛰어나다. uPP에서 DMA를 사용해 DSP의 데이터 이동을 완화시킴으로써 보다 중요한 작업에 DSP 사이클을 사용할 수 있게 됐다.

OMAP-L1x 플랫폼에 ARM 프로세서를 추가하면, 임베디드 리눅스짋 사용이 가능해져 사용자 인터페이스와 시스템의 모든 하우스키핑 기능을 관리할 커뮤니케이션 인프라가 제공된다. 또한 SD카드, USB 드라이브, 이더넷 연결을 이용해 시스템 소프트웨어(ARM, DSP, FPGA)를 현장 업그레이드 할 수 있다. 그러면 프로세싱 알고리즘의 진화에 따라 SDR 시스템의 탄력성을 최대한 활용할 수 있게 된다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>