3D-IC 집적의 혁신

상용화 기술 속속 등장… 가격대비 낮은 수율이 걸림돌

스마트폰이나 태블릿PC, 디지털카메라 등과 같은 휴대용 기기들은 더 다양한 기능을 수행하면서도 긴 배터리 수명과 작고 가벼운 제품 설계를 요구하고 있다. 이러한 수요에 맞춰 전체적인 시스템 측면에서 더 작고 가볍게 할 수 있는 기술이 필요하다. 그 대안으로 3D 패키지 기술이 떠오르고 있다. 크기를 늘리지 않으면서 기능과 메모리 용량을 늘리는 패키지 기술이 바로 3D 패키지다. 이제 막 연구실을 걸어 나온 3D-IC가 휴대용 기기에 적용되기 시작했다.

3D-IC 패키지는 2개 이상의 다이(로직, 메모리, 아날로그, RF 등)를 쌓아서 탑재할 수 있다. 당연히 다른 프로세스 노드(28nm High Speed Logic, 130nm Analog)의 탑재도 가능하다. TSV(Through Silicon Via) 기반의 3D-IC는 네트워크, 그래픽, 모바일 통신 및 컴퓨터 등에 적합하며, 특히 초경량, 소형, 저소비 전력이 요구되는 제품 영역에서 기대를 모으고 있다. 그 중에는 서버와 같은 데이터 전송 대역폭을 최대화하기 위해 사용되는 경우도 있지만, 그 대상 중 대부분은 소비자 제품이다.

3D-IC 패키지는 2개 이상의 다이(로직, 메모리, 아날로그, RF 등)를 쌓아서 탑재할 수 있다. 당연히 다른 프로세스 노드(28nm High Speed Logic, 130nm Analog)의 탑재도 가능하다. TSV(Through Silicon Via) 기반의 3D-IC는 네트워크, 그래픽, 모바일 통신 및 컴퓨터 등에 적합하며, 특히 초경량, 소형, 저소비 전력이 요구되는 제품 영역에서 기대를 모으고 있다. 그 중에는 서버와 같은 데이터 전송 대역폭을 최대화하기 위해 사용되는 경우도 있지만, 그 대상 중 대부분은 소비자 제품이다.

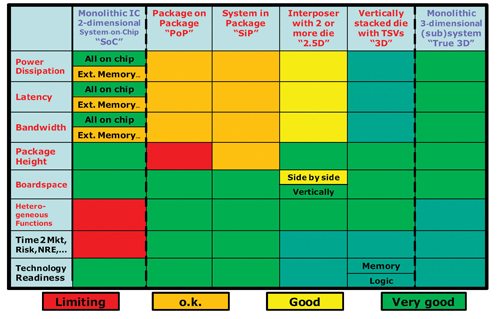

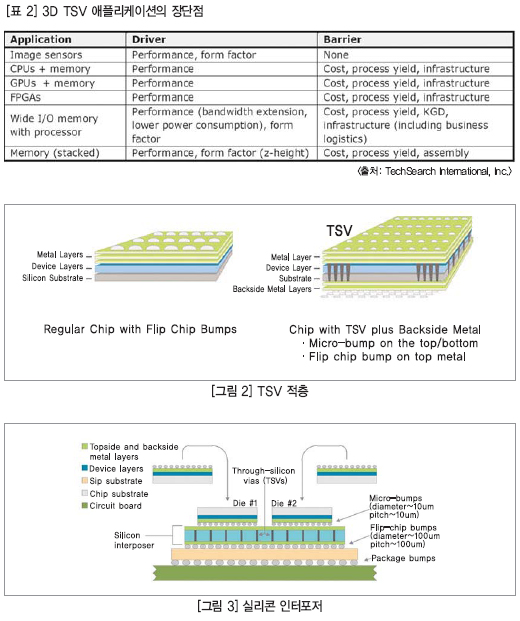

3D 실리콘(Si) 집적과 달리, 3D-IC 집적은 TSV 및 마이크로 범프를 이용해 무어의 법칙을 따르는 어떠한 칩들도 3차원으로 적층할 수 있다. 기본적으로 3D-IC 집적에는 두 가지가 있다. 하나는 메모리 칩 적층, 다른 하나는 실리콘 인터포저(interposer)이다.

첨단 공정의 SoC 또는 TSV 적층 또는 실리콘 인터포저의 트레이드오프는 한때 SoC 또는 SiP라는 논쟁이 있었던 것처럼, 각 구조에 대한 장단점 데이터 수집이 이루어지고 있다.

첨단 공정 SoC

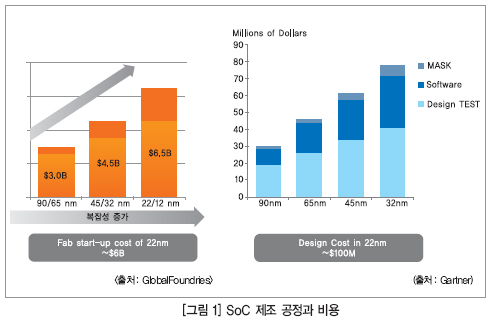

첨단 공정의 SoC는 개발 비용의 지속적인 상승을 피할 수 없다. 그림 1에 나와 있는 그래프는 SoC의 각 공정에 대한 팹(Fab) 가동 개시 비용과 설계비용을 보여주고 있다. 큰 볼륨이 기대되는 제품 외에는 첨단 공정을 사용하기엔 무리가 따르지만, 성능향상과 저전력 측면에서는 장점이 많다.

TSV를 이용한 3D-IC는 서로 다른 공정의 IC를 연결할 수 있기 때문에, 예를 들면 디지털 칩, 아날로그 칩, 메모리, RF 칩 등 다양한 공정의 IC 적층 구조를 실현할 수 있다. 또한 와이어 본드를 사용하지 않기 때문에, 접속 거리가 짧아 신호 속도가 극적으로 향상된다. 대역폭이 크게 향상되고, I/O 셀을 사용하지 않고 칩 간 접속을 실현하는 것도 가능하다. 이것은 기존의 SiP에 비하면 저전력화에 크게 기여한다. 그러나 TSV 구조는 여러 가지 문제가 있다. SoC의 디자인 룰은 물론, 새로운 TSV용 룰도 필요하다는 것이다. 즉, 레이아웃 룰(정렬 등), 레이아웃 레이어(백사이드 RDL), TSV의 전기 특성, TSV의 플로어 플랜(floor planning)과 플레이스먼트 룰(Hard Macro, Memory 등), 기타 열, 메커니컬 컨스트레인트(mechanical constraint), 모델 등 새로운 TSV의 사용 룰에 대한 책정이 시급하다.

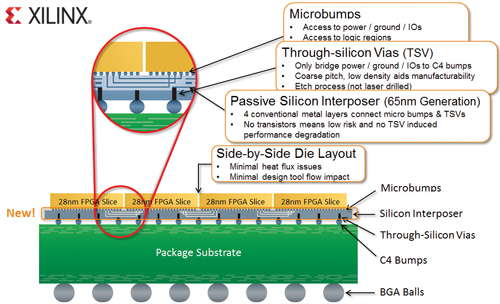

실리콘 인터포저는 소위 배선 레이어 만의 인터포저에서, TSV를 채용한 구조와 달리 각 IC는 기존의 IC 설계 기술로 설계가 가능하다. 멀티 칩으로 했을 때 칩 사이의 타이밍이나 전원공급 문제 등이 있지만, 기본적으로는 기존의 기술로 대응할 수 있다.

예를 들면, 자일링스의 Virtex-7은 4개의 FPGA 다이를 한데 묶어 수평으로 실리콘 인터포저 위에 얹은 구조(그림 4)로 칩 간 통신이 실리콘 인터포저를 통해 이루어져 매우 고성능 통신과 저전력 구조를 실현하고 있다. 그러나, 면적 문제로 적층을 고려할 경우는 반드시 TSV 기술이 필요하다.

3D-IC의 도전 과제

3D-IC를 설계하기 위해서는 어떤 설계 방법이 필요한가?

1. 3D 플로어 플래닝: 타이밍, 전력, 열에 대한 요건을 충족시키는 위치에 마이크로 범프(Micro bump) 및 TSV의 위치를 결정하고 배치한다.

2. 구현: TSV/Pad의 플레이스먼트와 플립칩 및 패키지의 통합 설계(co-design)에 의한 최적화, 다이 사이의 신호 및 전원 배선을 한다.

3. 최종적으로는 3D-IC 설계에 다음과 같은 기술이 필요하다.

· 여러 칩에 기능 분할

· 각 기능별로 최적의 실리콘 기술의 선택(DDR, GPU, 트랜스미터, DCC, DAC 등)

· 적층 구조의 선택

· 3D 플로어 플래닝에 의한 정확한 위치 결정, 전원공급, 성능 분석과 최적화

이와 관해서는 시스템 아키텍처 설계와 연계한 설계 접근법이 요구되며, 앞으로 3D-IC 설계의 과제라고 할 수 있다.

4. 다이 적층에 있어서 열 문제는 아주 중요한 문제다.

열을 포함한 멀티 다이의 전원, 신호의 무결성(integrity)은 3D-IC의 실현에 있어서 키포인트다.

5. 다음으로 중요한 과제는 테스트다.

새로운 3D의 멀티 다이에 대한 테스트 방법에 대해 새로운 표준 책정이 필요하며, 당연히 툴은 새로운 표준을 지원해야 한다.

6. 마지막으로, 시스템을 최종적으로 PCB로부터 패키지, 3D-IC와 최적화하기 위해서는 IC-PKG-PCB의 통합 설계 기술이 필요하다.

높은 가격도 문제

이처럼 열관리, 개발 인프라 외에도 3D-IC 기술의 보급 확산에 있어서 높은 장벽은 가격이다. 현재 기술로는 양산까지 갈 수 있을 만큼 가격대비 수율이 보장되지 않는다는 분석이다.

작년 10월 미국 캘리포니아 주 산타클라라에서 열린 인터내셔널 웨이퍼 레벨 패키징 컨퍼런스에 기조연설자로 나선 매튜 노박 퀄컴 선임 엔지니어는 “TSV 기술이 차세대 메모리 기술인 Wide I/O와 결합해 차세대 모바일 DRAM의 대표 기술 자리를 노리고 있지만 제조비용은 비싼 반면, 판매 이용을 낮춰야 하는 부담이 있다고 밝혔다. 또한 새로운 기술 도입에 따른 실패 위험을 떠안아야 한다는 우려 탓에 반도체 업체들이 양산에 이 기술을 적용하는 것을 주저하고 있다고 주장했다.

TSV의 상용화를 위한 국제협의기구인 반도체 3D 장비 및 재료 컨소시엄(EMC-3D)은 이 기술을 사용할 경우 웨이퍼 한 장당 120달러의 추가비용이 발생한다고 밝혔다. 기술만큼이나 가격경쟁력이 중요한 반도체 산업에서 TSV 기술은 ‘그림의 떡’인 셈이다.

이에 따라, TSV 기술에 의존하지 않고 고집적도로 인터포저(수동 소자를 포함하거나, 안 하거나) 및 수직 인터커텍트 구조를 이용한 베어 다이 적층으로 3D-IC를 구현하려는 업체들도 등장하고 있다. 온 세미컨덕터(On Semiconductor)는 SiP 기반의 기술을 이용하는 새로운 방식으로 보다 전통적인 프로세스와 어셈블리 기법들을 채택함으로써 소량/중량의 애플리케이션에 매우 안정적인 솔루션을 제공한다. 이 적층 기술은 협피치(fine-pitch) 플립칩, 웨이퍼 박막화, 고밀도 후막 세라믹 기판 분야에서의 발전된 기술을 이용해 디스크리트 소자 또는 수동부품들과 통합 패키징되며, 동일하거나 다른 소자와의 멀티 칩 어셈블리 설계가 가능하다. 따라서 TSV와 같은 멀티 칩 패키징 기법에서 직면하게 되는 진입방벽을 피해갈 수 있다는 게 온 세미컨덕터의 주장이다. 특히 특정 파운드리 공정에 의존하지 않기 때문에, 서로 다른 반도체 제조원의 여러 IC의 통합 설계에 적합하다는 설명이다.

TSV 연구개발 동향

TSV 연구개발 동향

현재 TSV를 개발하고 있는 곳은 삼성전자를 비롯해 엘피다, 프랑크 프라운호퍼 IZM, Georgia Tech, HKUST, IBM, IMEC, IME, 인피니언, 인텔, KAIST, 마이크론, NEC, Oki, 퀄컴, RPI, 테세라, TSMC, 자일링스, 집트로닉스 등을 포함한 산업계, 학교, 연구소 등 40여 곳에 이른다. 이미 해상도가 낮은 저가형 CMOS 이미지센서에는 TSV가 적용되고 있으며, 메모리나 로직에 TSV를 적용한 제품의 양산을 위해 여러 업체들이 원가절감 및 신뢰성 확보에 전력을 다하고 있다.

웨이퍼 천공, 비아 충진, 웨이퍼 박화 등의 TSV 기본 공정을 가장 먼저 정립한 업체는 Tru-Si Technologies로, 이에 대한 원천특허를 다수 확보하고 있다. TSV를 개발하기 위해서는 디자인에서부터 구멍을 뚫고, 채우고, 검사까지 모든 부분에 있어 선행되어야 할 과제가 많다.

많은 업체들은 얇은 웨이퍼를 다루고 연삭하는 공정 개발을 위해 활발히 연구를 진행 중이다. 얇아진 웨이퍼는 휨이 심해 비아 내부의 응력을 증가시킨다. 웨이퍼를 캐리어 웨이퍼에 부착하여 공정을 진행하는 방법이 대세를 이루고 있으나 웨이퍼를 붙이고 떼는 과정에서 수율 저하를 피할 수 없다. 이것을 막는 것이 관건이다. 얇은 칩을 적층하는 다양한 방법이 시도되고 있다.

TSV로 연결된 적층 칩의 검사방법에 대한 연구도 활발히 진행되고 있다. 기존의 탐침보다 더 작은 범프와 피치에 대응해야 하는 점과 적층된 3D 메모리칩의 KGP(Known Good Package) 검사를 수행하기 위한 인프라 구축이 IDM 업체들을 중심으로 준비되고 있다.

IBM은 2008년부터 무선통신에 사용되는 전력증폭기 소자와 마이크로프로세서의 그라운드용 TSV 기술 개발을 완료했다.

인텔은 CPU 위에 TSV Wide I/O로 메모리를 연결하는 제품의 양산화를 2012년 목표로 준비 중이다. 캐시 메모리로 고속 메모리를 올리는 경우와 전원 차단 시 데이터 저장이 가능한 비휘발성 메모리를 올리는 경우 모두를 준비하고 있다.

퀄컴은 휴대전화에 들어가는 베이스밴드 프로세서 위에 TSV로 메모리를 올리는 기술을 개발 중이다. 또한 RF를 포함한 무선 칩에 TSV를 적용하여 전원과 그라운드를 연결해서 고주파 성능을 향상시키는 방안도 병행하고 있다.

도시바는 TSV 기술을 CMOS 이미지센서에 적용하여 2008년부터 생산 중에 있다. TSV 전극이 붙은 칩을 제조하는 것으로 웨이퍼 상태에서 카메라 모듈 부품의 실장 조립을 가능하게 한다.

ST마이크로일렉트로닉스는 2007년부터 참가해 온 IBM주도의 Common Process Platform Alliance에서 공동 개발을 진행하는 한편, 벨기에 IMEC의 3D 패키지 기술의 공동개발 프로그램에도 참가하여 개발을 진행하고 있다.

KAIST 테라랩은 작년에 TSV에 대한 연구 및 전기적 설계 응용 기술을 하이닉스 반도체와 공동 개발, 기술 이전했다. 태라랩은 단순한 전기적 해석 및 설계 기술뿐만 아니라, 열이나 기구적인 문제가 결부된 3D IC 설계 기술을 꾸준히 개발하고 있다.

멘토 그래픽스의 캘리버(Calibre짋) 플랫폼은 디자인 룰 검사(Design Rule Checking, DRC)와 레이아웃 대 회로도(Layout vs. Schematic, LVS) 검사를 비롯해 TSV가 사용된 실리콘 인터포저 구성에 채택되는 디자인의 추출을 지원한다. 멘토 그래픽스의 테센트(Tessent짋) 실리콘 테스트 제품 스위트에서는 3D-IC 디자인에 대한 포괄적인 테스트를 지원한다. 또한 이 제품을 사용하면 로직, 적층 메모리, 임베디드 CPU 코어, Wide I/O 버스나 고속 시리얼 I/O를 갖춘 인터포저 및 3D 구성을 테스트할 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>