차세대 PCB 전성시대

고다층화, 고집적화, 환경친화적 PCB 개발 대세

SMT 부품까지 내장

스마트 단말기 및 관련 전자부품의 경박·단소화에 대한 요구가 급증하고 있다. 특히, 유기 소재를 기반으로 하는 인쇄회로기판(PCB) 및 패키징 분야에서는 3차원 고집적 패키징을 위하여 빌드업 기판 기술, 임베디드 능·수동소자 기술 및 마이크로비아 기술 등이 활발히 연구되어 상용화가 이루어지고 있다. 임베디드 PCB는 저항이나 커패시터 등 수동부품과 IC 등을 심는 대신 그 기능을 PCB에 내장해 면적과 신호 간섭을 줄인 차세대 제품이다.

휴대전화 등의 모바일 기기의 소형화는 기존 전자부품의 소형화와 SMD(표면실장부품)화가 주도해 왔다. 예를 들어, 휴대전화에는 많은 적층 세라믹 칩커패시터가 사용되고 있다. 같은 용량으로 비교하면, 1980년대부터 현재까지 체적은 100분의 1 이하로 소형화되었다. 또한 같은 크기로 비교해 보면, 커패시턴스는 약 1,000배나 대용량화되었다.

휴대전화 등의 모바일 기기의 소형화는 기존 전자부품의 소형화와 SMD(표면실장부품)화가 주도해 왔다. 예를 들어, 휴대전화에는 많은 적층 세라믹 칩커패시터가 사용되고 있다. 같은 용량으로 비교하면, 1980년대부터 현재까지 체적은 100분의 1 이하로 소형화되었다. 또한 같은 크기로 비교해 보면, 커패시턴스는 약 1,000배나 대용량화되었다.

이러한 소형화와 대용량화가 진행되는 한편, 최근 적층 세라믹 커패시터는 1 mm 미만의 박형화가 요구되고 있다. PCB에 전자부품을 수평 배치하는 기존 방식에 의한 고밀도 실장이 한계에 다다르고 있기 때문이다. 이 한계를 극복하기 위해 등장한 기술이 바로 부품 내장 기판이다. 이것은 다층화된 PCB 내부에 집적회로(IC)와 커패시터와 같은 수동부품을 박형화해 내장하는 기술이다.

공간절약 꾀하는 패키징 기술

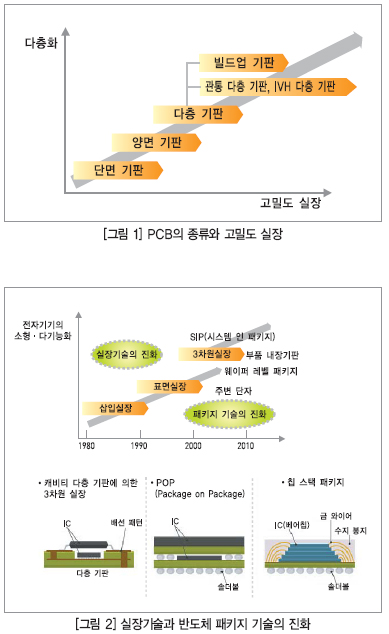

실장 기술은 전자부품의 소형화와 함께 발전해 왔다. 1970년대의 실장기술은 디스크리트 부품의 리드 선을 PCB에 삽입하는 방식이었다. 1980년대에는 리드 선을 없앤 SMD 타입의 전자부품이 많아졌고, 전자기기의 소형·경량화가 빠르게 진행되었다. 카폰과 숄더폰의 실패를 거쳐 휴대전화가 등장한 것도 이 무렵이다.

커패시터와 같은 수동부품의 소형화가 진행되면서, IC도 공간 절약이 요구되기 시작했다. 웨이퍼 상에 잘려진 반도체 칩(다이) 자체는 작지만, 리드프레임에 탑재하는 기존 패키지는 면적과 체적이 동시에 커지기 때문이다(리드프레임은 반도체 칩 표면의 단자를 금 Au 선으로 연결하는 금속 프레임을 말한다. 연결 후 수지 등으로 몰딩하여 분리하면 리드프레임은 지네 다리 같은 리드 선이 된다). 그래서 칩 뒷면에 격자 모양의 단자를 마련하고 미세한 솔더 볼로 연결하는 방식이 채택되었다. 이것을 BGA(Ball Grid Array) 등으로 부르고 있다.

또한 여러 개의 IC를 기판에 수평으로 배치하는 대신에 적층하여 공간 절약을 도모할 수 있게 되었다. 반도체 칩(베어 칩) 자체를 적층하는 형태는 CoC(Chip on Chip) 혹은 칩 적층 패키지라고 하고, 패키징된 반도체를 적층하는 형태는 PoP(Package on Package) 등으로 부르고 있다. 또한 여러 개의 IC를 포함하는 시스템 전체를 3차원으로 실장하여 단일 패키지화 한 SiP(System in Package) 형태의 실장 방식도 급성장하고 있다.

부품 내장의 3가지 방법

현재까지 PCB에 부품을 내장하기 위한 많은 기술들이 개발됐다. 각각의 방법은 나름대로 장단점을 갖고 있다. 수동부품은 대부분 내장되고 있는 추세이며, IC를 내장하려는 연구도 활발하게 진행되고 있다. 이 경우에는 테스트와 검증이 대단히 중요하다.

일반적으로 수동부품을 내장하기 위해서는 기존의 수동부품을 내장하는 방법, 특별하게 제작된 얇은 수동부품을 내장하는 방법, 인쇄나 다른 공정으로 필름 디바이스를 제작하는 방법 등이 있다.

기존 수동부품을 내장하는 경우, 처리할 수 있는 부품의 종류에 제약이 없으며, 장비 제조업체들은 자신이 원하는 저항이나 커패시턴스를 얻을 수 있다. 기존의 부품을 사용하기 때문에 기존 제조장비도 그대로 이용할 수 있다. 한 가지 단점은 보드가 선택된 부품을 수용해야 하기 때문에 두꺼워져야 한다는 것이다. 또한 부품을 부착하기 위해 보드에 구멍을 뚫는 등의 표면실장 공정 이외에 부품 내장을 위한 별도의 공정이 추가되기 때문에 비용이 상승하게 된다.

특별히 제작된 얇은 부품을 이용하는 경우, 보드의 두께를 대폭 줄일 수 있고, 얇은 부품에 보드 레이어를 덮으면 보드에 구멍을 뚫을 필요가 없다. 이 방법은 같은 두께를 갖는 세 번째 방법에 비해 패키지 전에 결함이 있는 부품을 골라낼 수 있다는 장점이 있다. 히지만, 어떤 경우이든 이 방법을 이용하려면 부품 패키지 단계가 필요하다.

인쇄 과정을 통해 필름 디바이스를 형성하는 방법은 필름 디바이스를 한 번에 만들 수 있기 때문에 패키지 공정 개수와 비용을 줄일 수 있다. 본딩 안전성이 향상되어 솔더 본드의 개수가 줄어 제품이 가벼워지며 환경 부담도 줄일 수 있다. 하지만, 필름 디바이스에는 몇 가지 특성 제한이 있어 임베디드 부품 사용에 제한이 되고 있다.

초박형 적층 세라믹 커패시터

CoC, PoP, SiP를 과밀 도시에서 건물의 고층화에 의한 공간절약 기술에 비유한다면, 지하공간을 이용하는 것에 해당하는 것이 바로 임베디드 PCB 기술이다. 이것은 다층 기판 내부에 공동(cavity)을 마련하고, 거기에 반도체 소자(IC)는 물론, 커패시터, 인덕터와 같은 수동부품을 내장해 보다 고밀도 실장을 실현하는 기술이다.

커패시터와 인덕터 같은 수동소자를, 다층 기판 사이에 구성하는 기존 기술로 LTCC(저온 소성 다층 기판) 공법이 있다. 이것은 유전체 시트에 커패시터와 인덕터 소자의 도체 패턴을 스크린 인쇄하여, 이를 소정의 순서로 쌓아 압착한 후 약 900 ℃의 온도에서 소성하는 공법이다.

LTCC는 휴대전화의 고주파 모듈 등의 제조에 사용되고 있다. 그러나, 반도체 소자 등을 포함하는 다층 기판은 200 ℃ 이하의 저온 공정이기 때문에, 빌드업(Build up) 공법이 채용되고 있다. 이것은 도금 인쇄 등에 의하여 차례로 도체층, 절연층을 쌓아 다층 기판을 만드는 공법이다.

기판 간의 배선은 비아(도통 홀)에 의해 연결되며, 또한 빌드업 과정에서 다층 기판 내부에 구멍을 만들어 IC나 수동부품을 내장할 수 있다.

하지만, IC 칩도 그대로는 너무 두껍기 때문에 기판을 얇게 깎아서 내장한다. 예컨대 TDK는 IC 칩을 50 μm까지 얇게 가공하여, 이것을 기판 내에 내장하는 IC 내장 기판 기술을 개발했다.

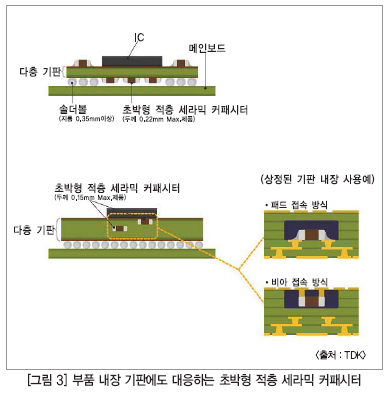

적층 세라믹 커패시터를 다층 기판 내부에 포함시키려면, 미크론 단위의 박형화가 요구된다. 첨단 재료기술과 정밀 적층기술 등을 결합해 TDK가 개발한 것이 초박형 적층 세라믹 커패시터다.

두께 0.22 mm 제품은 솔더 볼의 지름(0.35 mm 이상)보다 작기 때문에, BGA 기판 뒷면의 틈새에 탑재가 가능하다. 또한 두께 0.15 mm 제품은 다층 기판 내부에 내장할 수도 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>