산업 데이터 수집 시스템 설계의 최근 추세는 인터페이스 클록 신호와의 동기화를 고려하지 않고 있기 때문에, 마이크로컨트롤러와 대응하는 ADC 및 DAC 사이의 거리가 수 미터이상 될 수 있다. 이로 인한 인터페이스 오작동의 원인과 그 해결책을 알아본다.

글 | 토마스 쿠겔슈탓트(Thomas Kugelstadt)

글 | 토마스 쿠겔슈탓트(Thomas Kugelstadt)

선임 애플리케이션 엔지니어

텍사스 인스트루먼트(Texas Instruments)

SPI(Serial Peripheral Interface) 버스는 집적회로 간의 단거리 통신을 위해 설계된 일방(unbalanced) 또는 싱글 엔드(single-ended) 직렬 인터페이스다. 일반적으로 마스터 디바이스는 한 개 이상의 슬레이브 디바이스와 데이터를 교환한다. 이 데이터 교환은 전이중(full-duplex)으로, 여기에는 인터페이스 클록 신호와의 동기화가 필요하다. 그러나, 산업 데이터 수집 시스템 설계의 최근 추세는 이런 동기화를 고려하지 않고 있기 때문에, 마이크로컨트롤러와 대응하는 ADC 및 DAC 사이의 거리가 100 m 이상이 될 수 있다.

추가 전파 지연이 데이터-투-클록 동시성(data-to-clock synchronicity)에 미치는 영향이 종종 무시되는 경우가 있으며, 실험실 환경에서 완벽하게 동작하는 인터페이스 설계라도 작업 현장에서 구현되면 동작이 멈출 수 있다. 이러한 인터페이스 오작동의 원인은 여러 가지가 있을 수 있다. 이 글은 다음과 같은 주요 원인을 몇 가지 밝혀본다:

- 신호 경로의 대규모 전파 지연으로 인한 동기화 부족

- 장거리의 일방 신호 경로로 인한 노이즈 내성(immunity) 감소

- 대규모 GPD(Ground-Potential Differences)로 인해 손상된 트랜시버

- 비종단(unterminated) 데이터 라인으로 인한 데이터 전송 오류

- 대규모 전기적 과도현상(transient)으로 인한 트랜시버 래치업(latch-up) 및 네트워크 정지시간

동시성(Synchronicity)

SPI는 주로 세 개의 인터페이스 라인을 사용한다:

- 동기화 데이터 전송을 보증하기 위해 마스터 디바이스가 개시(initiated)하는 인터페이스 클록

- 마스터가 슬레이브로 보내는 데이터를 위한 데이터 라인

- 슬레이브가 마스터로 보내는 데이터를 위한 데이터 라인

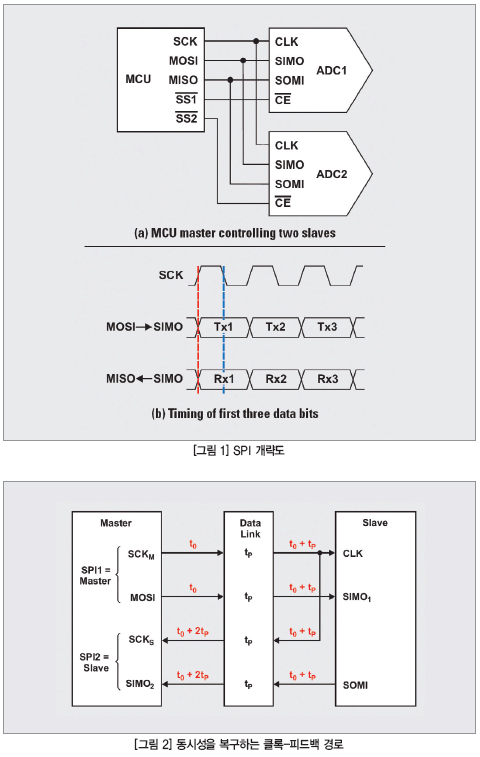

슬레이브-선택 신호라는 것을 나르는 네 번째 와이어는 인터페이스 흐름을 제어하는데 필요한 것이 아니라, 슬레이브 디바이스의 범위에서 벗어난 특정 슬레이브를 어드레싱 하기 위해 필요하다. 그림 1a는 MCU가 마스터 역할을 하며, 슬레이브를 나타내는 두 개의 데이터 컨버터를 제어하는 모습을 그린 개략도이다.

8~12비트의 바이트 길이와 그에 관한 멀티플, 그리고 1~120 Mbps 범위의 데이터 레이트를 제공하는 표준 SPI 구성은 짧은 전파 시간을 허용하기 때문에, 두 방향에서 전송된 데이터와 인터페이스 클록 사이에서 동시성을 유지하려면 단거리에서만 가능하다. 그림 1b는 SPI가 상승 클록 에지에서 데이터를 바꾸고 하강 클록 에지에서 데이터를 샘플링하도록 구성했을 경우에 처음 세 개 데이터 비트의 인터페이스 타이밍을 보여주고 있다.

그러나, 장거리에서 이 전송 케이블은 신호 경로에 상당한 전파 지연을 초래한다. 신호 속도가 보통 5 ns/m라고 가정했을 때, 100-m 케이블은 500 ns의 전파 지연을 초래한다. 마스터에서 슬레이브로 보내는 데이터는 마스터가 개시한 인터페이스 클록과 같은 지연을 경험하기 때문에, 둘은 여전히 전체 데이터 링크에서 싱크 상태를 유지하게 될 것이다. 그러나 반대 방향인 경우, 슬레이브는 첫 번째 클록 에지가 슬레이브에 도달한 때에만 마스터로 데이터를 보낸다. 또한, 이 데이터는 마스터로 되돌아갈 때 두 번째 지연을 경험하게 될 것이고, 따라서 슬레이브 데이터는 그 케이블 전파 지연의 두 배까지 싱크를 벗어나게 될 것이다.

물론, 100-m 케이블에서의 통신은 해당 라인 드라이버와 리시버 없이는 불가능할 것이다. 이 컴포넌트들은 약 5 ns 가량 더 전파 지연을 증가시켜 총 550 ns의 전파 지연을 일으킬 것이다. 따라서, 슬레이브 데이터는 데이터 레이트가 10 Mbps라고 가정했을 때 첫 번째 클록 에지보다 총 1100 ns, 즉, 11 bit 뒤처지게 될 것이다.

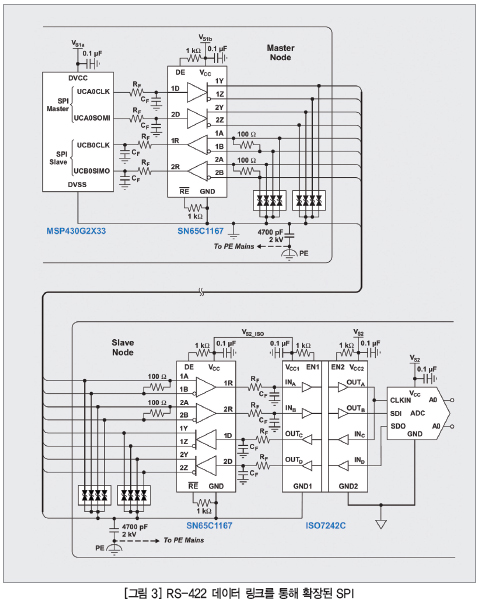

슬레이브 데이터와 인터페이스 클록 사이의 동시성을 복구하면서 고속 데이터 레이트를 유지할 수 있는 유일한 방법은 슬레이브에서 다시 마스터로 클록 신호를 공급하는 것이다. 그림 2는 클록 피드백의 이점을 명확히 보여주고 있다. 여기에서 t0은 첫 번째 상승 클록 에지, 즉 데이터 전송의 시작을 나타내며, tP는 데이터-링크 전파 지연이다. 데이터 링크를 오간 후, 마스터 클록(SCKM)과 마스터 데이터(MOSI) 둘 다 싱크 상태를 유지한다. 마스터 클록 신호를 다시 공급하면, 그 클록이 슬레이브 데이터와 동기화되면서 둘 다 똑같이 지연되어 마스터에 도달하게 된다. 유일한 요건이라면, 하나는 마스터(SPI1)로 구성되고 다른 하나는 슬레이브(SPI2)로 구성되는 두 개의 독립 SPI 포트를 마스터가 제공해야 한다는 것이다. 최신 마이크로컨트롤러는 대부분 두 개 이상의 SPI 포트를 가지고 있기 때문에, 이러한 요건은 더 이상 문제되지 않는다.

그럼에도 불구하고 장거리의 SPI 호환 인터페이스를 실제로 구현하는 일은 그리 쉽지 않다. 장거리 데이터 링크는 항상 외부 노이즈 소스, GPD (Ground-Potential Differences), 유도 부하 스위칭으로 인한 전압 및 전류 서지, 심지어 잘못된 종단이나 종단 없음으로 인한 반사 등에 영향을 받기 쉽다. 그림 3의 흐름도는 이러한 감손 효과를 중화시킬 수 있는 다양한 트랜시버 및 보호회로를 소개함으로써 이러한 요소들 모두를 해결하려고 한다.

노이즈 내성 증가

일방 또는 싱글 엔드 드라이버와 리시버는 장거리에서 견고한 데이터 링크를 달성하는 데 부적합하다. 공통 모드 노이즈(common-mode noise)에 취약하기 때문이다. SPI처럼 동기식 전이중 인터페이스에서 공통 모드 노이즈를 제거할 수 있는 좋은 방법은 RS-422 차동 드라이버 및 리시버 회로를 연선(twisted pair wire)과 조합하여 사용하는 것이다.

연선의 컨덕터는 빈틈없이 전기적으로 커플링되어 있기 때문에, 두 컨덕터 모두에 똑같이 유도된 외부 노이즈는 리시버 입력 위치에서 공통 모드 노이즈로 나타난다. 차동 리시버들이 신호 차이에 민감하더라도, 이들은 공통 모드 신호에 내성이 있다. 따라서, 이 리시버는 공통 모드 노이즈를 거부하게 되고, 신호 무결성은 유지된다.

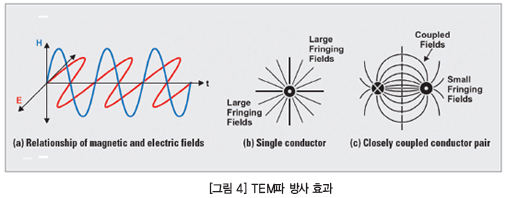

빈틈없는 전기 커플링의 또 다른 장점은 이 두 컨덕터의 전류가 서로를 상쇄하는 자기장을 만들어낸다는 것이다. 그래서 이 두 컨덕터의 초기 TEM (Transversal Electromagnetic) 파는 크게 감소되어 주변으로 방출될 수 없는 전기장이 된다(그림 4). 이 컨덕터 루프 밖의 훨씬 작은 프린징 필드만 방출될 수 있기 때문에, EMI(Electromagnetic Interference)가 훨씬 더 낮아진다.

그라운드 루프와 GPD 제거

RS-485 및 RS-422 표준은 접지선이 없는 데이터 링크를 최대 ±7 V의 GPD로 작동시킬 수 있다고 명시하고 있지만, 이 값들이 최대 GPD를 나타낸다고 가정하지 않는 것이 좋다.

산업 플랜트에서는 훨씬 더 높은 값들을 접할 때가 많으며 가끔은 수 백 볼트, 심지어 수 천 볼트에 달하기까지 한다. GPD는 전기설비/전기모터 및 발전기의 수 같은 시스템 설계자의 통제를 벗어나는 요소에 주로 좌우되기 때문에, 큰 접지전위(ground potential) 변동으로 인한 트랜시버 손상을 막는 가장 안전한 방법은 버스로부터 원거리 네트워크 노드를 갈바니 절연하는 것이다. 그림 3의 회로는 원거리 트랜시버만 버스에 연결시킴으로써 이를 잘 보여주고 있다. 반면, 데이터-컨버터 회로는 갈바니 절연되어 있다.

또한 원거리 트랜시버의 입력 신호와 출력 신호를 안정적인 기준접지(ground reference)에 제공하기 위해 이 트랜시버의 접지 단자와 디지털 아이솔레이터의 접지 단자(GND1)가 별도의 접지 도체(ground conductor)를 통해 마스터 접지전위에 연결되어 있다. 이러한 형태의 그라운딩을 단일 기준접지라고 한다.

라인 종단을 통한 안테나 피하기

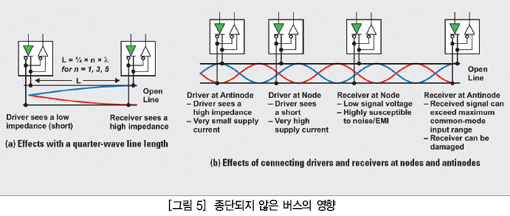

그림 3의 데이터 링크는 RS-422 표준이 제시하는 대로, 버스 케이블의 독특한 임피던스에 맞춰 100-W 저항으로 종단된다. 길이가 수 미터인 버스 케이블이나 낮은 데이터 레이트로 작동하는 데이터 링크를 가진 버스 케이블은 종단이 필요 없다는 통념이 있다. 절대로 믿어서는 안 된다. 종단 없이 버스를 작동시키면, 전송 라인이 형편없는 리시버/트랜스미터 안테나로 바뀔 수 있다. 종단 저항의 결여는, 대개의 경우 드라이버가 보내는 입사파력(incident wave power)을 흡수하여, 정재파(standing waves)를 발생시키고, 전체 입사파가 그 버스에 반사된다. 반사된 파는 다른 입사파들과 혼합되어 신호 주파수를 위한 정재파를 내놓게 된다. 이때 그 신호 주파수의 1/4 파장이나 그에 관한 멀티플은 데이터 링크의 길이와 동일하다.

위치에 따라 그 웨이브 노드(최소)와 안티노드(최대)는 버스 트랜시버에 다양한 영향을 미칠 수 있다(그림 5 참조). 안티노드에 가까운 드라이버라면 임피던스가 높아 버스에 부족한 에너지를 전송하게 된다. 노드에 가까운 드라이버라면, 매우 낮은 임피던스를 보게 되거나 쇼트를 보게 된다. 그로 인한 출력 전류는 해당 드라이버의 최대 드라이브 능력을 초과할 수 있고, 심지어 약 250 mA에서 전류 한계를 유발시킬 수도 있다. 안티노드에 위치한 리시버는 그 리시버의 공통 모드 입력 범위를 초과하는 지나치게 큰 입력 신호로 인해 손상을 입을 수 있다. 노드에 가까운 리시버는 신호 세기가 불충분해서 노이즈 및 EMI에 매우 취약하다. 상기 내용 모두가 잘못된 데이터의 전송으로 인한 데이터 오류나 잘못된 데이터의 수신으로 인한 데이터 오류를 일으킬 수 있다.

해로운 과도현상으로부터 네트워크 보호

ESD(Electrostatic Discharge), 유도 부하의 스위칭, 낙뢰 등으로 인한 전기적 과압 과도현상은 그 영향을 줄이기 위한 적절한 조치가 취해지지 않은 한, 데이터 전송에 오류를 일으키고 버스 트랜시버를 손상시킨다. 그림 3처럼 최신 TVS(Transient Voltage Suppression) 소자는 그 낮은 커패시턴스로 인해 고속 데이터 전송용 보호 부품으로 선호되고 있으며, 데이터 레이트를 감소시키지 않고도 이것을 멀티노드 네트워크의 모든 노드 안에 설계해 넣을 수 있다.

선택한 TVS 소자의 전력 등급에 따라, 최대 클램프 전압은 25~35 V까지 다양하다. 이것은 표준 트랜시버의 최대 버스 전압 14 V보다 더 높다. 이런 경우, 그 트랜시버의 내부 보호회로는 반드시 나머지 클램프 에너지를 흡수하여 디바이스의 손상을 막아야 한다.

ESD 및 버스트 과도현상의 경우, 짧은 펄스 길이 때문에, 클램프 에너지가 다소 낮은 편이지만 내부 ESD 셀에 문제를 일으키지 않는다. 그러나, 서지 과도현상으로 인한 클램프 에너지는 펄스 길이가 훨씬 더 길기 때문에 심각한 문제를 야기할 수 있다. ESD 내성이 낮게 지정되어 있는 트랜시버의 경우, 트랜시버를 흐르는 나머지 전류를 줄이기 위해 직렬 저항이 필요할 수도 있다. 공통 저항 값은 5~10 W 범위이다. 이 저항들은 높은 펄스 강건성을 제공하기 위해 반드시 정격 서지이어야 한다.

TVS 다이오드가 큰 과도 전류를 접지로 전환시킨다 하더라도, 나머지 회로의 기준접지를 교란시키는 일없이 이 전류들이 진정한 대지전위(true earth potential)로 추가 전환되도록 해야 한다. 이것은 한 플레이트는 접지에, 다른 한 플레이트는 보호 접지(Protective-Earth, PE) 아일랜드에 연결시킨 고전압 커패시터를 구현하는 방식으로 이루어지는 경우가 많다. 그러면 이 아일랜드는 짧은 저-인덕턴스 접지선을 통해 로컬 메인 서플라이의 PE 단자에 연결된다.

이 억제장치(suppressor)의 버스 측 동작과 더불어 트랜시버의 싱글 엔드 측에 신호 하락을 막을 수 있는 추가 보호가 필요하다. 이것은 R-C 로우-패스 필터로 가능하다. 이것은 수신 경로에서 잔류 과도 전류를 여과하여 고주파수 노이즈가 전송 경로로 들어가는 것을 막는다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>