수볼타(SuVolta, www.suvolta.com)는 미국 워싱턴 D.C.에서 개최된 2011 IEDM에서 자사의 저전력 트랜지스터 기술인 DDC (Deeply Depleted Channel™)의 세부내용을 공개했다.

수볼타(SuVolta, www.suvolta.com)는 미국 워싱턴 D.C.에서 개최된 2011 IEDM에서 자사의 저전력 트랜지스터 기술인 DDC (Deeply Depleted Channel™)의 세부내용을 공개했다.

DDC는 수볼타의 저전력 CMOS 플랫폼 파워슈링크(PowerShrink™)의 기초가 되는 기술이며, 동작 속도에 영향을 주지 않으면서도 소비 전력을 50% 줄일 수 있게 해준다. 수볼타는 최신 전압 스케일링 기법과 DDC 기술을 적용하면, 전력 소모를 80% 이상 줄일 수 있다고 주장한다.

수볼타의 사장 겸 대표이사인 브루스 맥윌리엄스(Bruce McWilliams) 박사는 “실리콘 측정 결과로 증명된 수볼타 기술은 반도체 업계에서 많은 관심을 불러 모으고 있다”면서 “DDC 트랜지스터 기술을 좀 더 상세하게 공개함으로써 어떻게 수볼타 기술이 전력 소모를 감소시키고 동작 전압을 낮추며, 20 nm 이하의 공정에서도 스케일링이 가능하게 하는 지를 보여 주고자 한다.”고 말했다.

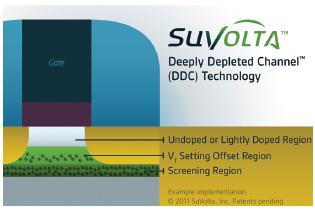

수볼타의 DDC 트랜지스터는 문턱전압(VT) 변화폭을 줄임으로써 지속적인 CMOS 스케일링을 가능하게 해준다. 이것은 게이트에 전압이 가해지면, 채널 영역의 공핍층이 기판 방향으로 깊게 퍼져가는 구조를 이용한다. DDC 채널 구조는 일반적으로 불순물(dopant)이 거의 포함되지 않는 영역과 VT를 설정해야 할 오프셋 영역, 그리고 스크리닝 영역으로 이루어져 있다. 하지만, 실제로 웨이퍼 팹 시설 및 칩 설계 요구조건에 따라 달라질 수 있다.

이 불순물이 거의 없는 영역에서는 채널의 불순물을 제거함으로써 공핍층이 채널 가득 퍼지게 되어 랜덤 도펀트변동(Random Dopant Fluctuation, RDF)이 줄고 VDD를 스케일링 할 수 있으며 이동성이 향상돼 유효 전류가 증가하게 된다.

또한 VT를 설정하기 위한 오프셋 영역은 채널 이동성을 저하시키지 않으면서 트랜지스터의 문턱전압을 설정하는 부분이다. 이 영역도 기존 트랜지스터보다 VT의 편차가 적게 개선되는 효과가 있다.

스크리닝 영역은 전하를 제한하여 공핍층의 깊이를 결정하는 부분이지만, 이 공간을 활용하면 필요에 따라 기판 바이어스에 의해 VT를 동적으로 조정하는 것도 가능하다고 한다.

따라서, DDC 트랜지스터는 전원 전압을 낮출 수 있고 저전력 동작을 실현할 수 있다. 또한 VT의 편차를 줄임으로써 성능저하 없이 동작 전압을 30% 줄일 수 있으며, 누설 전류의 제언, 그리고 수율 개선이 가능하다.

게다가 DDC 트랜지스터는 오늘날 저전력 제품 설계 시 반드시 필요한 멀티 VT 설정도 가능하기 때문에, 채널 이동성을 향상시켜 구동 전류를 증가시키거나 드레인에 의한 배리어 감소 효과(Drain Induced Barrier Lowering, DIBL)를 줄일 수 있고 바디 계수(Body coefficient) 증가에 의한 VT 제어 범위를 확대할 수 있다.

수볼타의 최고기술책임자(CTO)인 스콧 톰슨(Scott Thompson) 박사는 “칩은 더 이상 소형화해도 의미가 없는 시대가 다가오고 있다. 리소그래피 비용이 상승하고 트랜지스터 당 제조비용이 정체되어감에 따라 무어의 법칙의 종말이 다가오고 있음을 보여주고 있다. 오랫동안 지속될 것이라고 믿고 있는 28 nm와 20 nm 공정에서도 그러한 때가 다가오고 있다.”며, “마이크로프로세서를 제외하고, 모바일용 칩의 대부분은 가격과 저전력 소모에 프리미엄이 있다. DDC 트랜지스터는 오늘날 널리 사용되고 있는 CMOS 공정과 호환성이 있는 기술이며, 이 기술을 통해 반도체 기업들은 수년에 걸쳐 개발한 레거시 회로 IP 블록을 보존하고 사용할 수 있다.”고 말했다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>