래티스 반도체는 LatticeECP3™에 기반을 둔 와이어-본드 패키지의 저비용 저전력 미드-레인지 FPGA인 LatticeECP4™ 제품군을 발표했다.

래티스 반도체는 LatticeECP3™에 기반을 둔 와이어-본드 패키지의 저비용 저전력 미드-레인지 FPGA인 LatticeECP4™ 제품군을 발표했다.

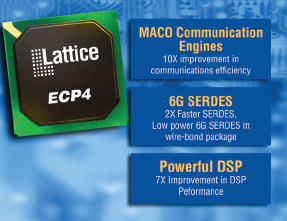

LatticeECP4 FPGA는 임베디드 PCS(Physical Coding Sub-layer) 블록과 함께 최대 16개의 CEI-호환 6 Gbps SERDES 채널을 포함하고 있다. 특히, 저비용 와이어본드와 고성능 플립칩 패키지로 제공되기 때문에, 칩-투-칩 또는 장거리 백플레인 애플리케이션에 채용할 수 있다. 다목적 설정 가능 SERDES/PCS는 하드 통신 엔진과 통합될 수 있기 때문에 경제적으로 완벽한 고대역폭 서브시스템을 구축할 수 있다. 통신 엔진은 유사한 FPGA 패브릭 구현방법 대비 최대 10배의 전력 및 비용절감 효과를 제공한다. LatticeECP4 통신 엔진 포트폴리오는 PCI Express 2.1, 복수의 10기가비트 이더넷 MAC, 3배속 Ethernet MAC 등은 물론, Serial Rapid I/O (SRIO) 2.1을 포함한다.

LatticeECP4 제품군은 18×18 곱셈기, 와이드 ALU, 덧셈기-트리, 캐스케이드 기능을 위한 캐리 체인 등과 함께 강력한 DSP 블록을 제공한다. 독창적인 부스터 로직은 각각의 Lattice ECP4 DSP 블록이 4개의 LatticeECP3 DSP 블록과 동일하다는 것을 의미하며, 이전 세대인 LatticeECP3 디바이스 대비 최대 4배의 신호처리 성능을 지원한다. 유연한 18×18 곱셈기는 9×9로 분리 또는 36×36로 통합 가능하기 때문에, 애플리케이션 요구사항과 완벽하게 일치될 수 있다. 또한 최대 576개의 곱셈기를 함께 캐스케이딩 할 수 있기 때문에 무선 RRH, MIMO-기반 RF 안테나 솔루션, 비디오 처리 애플리케이션 등을 위한 복잡한 필터를 구축할 수 있다.

LatticeECP4 FPGA는 이전 세대보다 최대 50% 빠른 성능을 제공하며, 1066 Mbps DDR3 메모리 인터페이스와 시리얼 기가비트 이더넷 인터페이스로도 이용 가능한 1.25 Gbps LVDS I/O를 제공한다. 또한 66% 많은 로직 자원과 42% 많은 임베디드 메모리를 제공하기 때문에 설계 엔지니어들이 완벽한 시스템-온-칩을 FPGA로 구축할 수 있도록 지원한다.

LatticeECP4 FPGA는 래티스 다이아몬드 1.4 베타 설계 소프트웨어를 사용해 설계할 수 있다. 샘플은 2012년 상반기에 공급될 예정이며, 대량생산은 2012년 하반기로 예정돼 있다.

www.latticesemi.com

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>