후지쯔 반도체와 수볼타는, 수볼타의 파워슈링크(PowerShrink™) 저전력 CMOS 플랫폼을 후지쯔의 저전력 공정기술에 적용하여, 최소 전원전압이 0.425V까지 동작하는 초저전압 SRAM 블럭의 동작을 성공적으로 시연했다고 발표했다. 전력소모를 감소시켜주는 이 기술은 가까운 미래에 최상의 친환경적 제품 출시를 가능하게 해 줄 것이다. 본 기술에 대한 자세한 내용과 결과는 12월 5일부터 워싱턴 DC 에서 열린 2011년 국제전자소자학회 (IEDM)에서 발표됐다.

소비전력을 조절하는 것은 모바일 기기에서부터 서버, 네트웍 장비 등에 이르는 제품에 기능을 추가하는 데 있어 가장 큰 제약사항이다. 전력소모에 가장 큰 영향을 주는 것은 전원전압으로, 과거에는 CMOS 전원전압이 꾸준히 감소하여 130nm 공정기술노드에서 약 1.0V까지 줄었지만, 이후 반도체 공정 기술이 28nm 노드로 스케일되는 데 비해 전원전압은 더 이상 줄어들지 않고 있다. 전원전압을 줄이는 데 있어 가장 큰 장애물은 내장 SRAM 블럭의 최소동작전압이다.

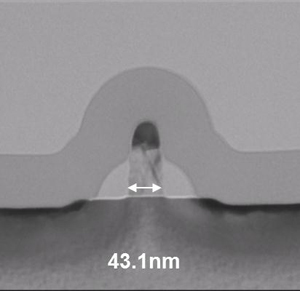

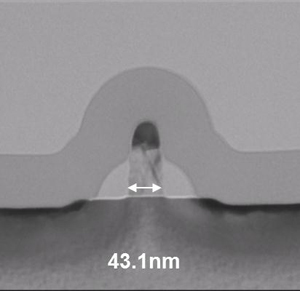

수볼타 파워슈링크(PowerShrink™) 플랫폼의 기초가 되는 DDC 트랜지스터 기술과 후지쯔 반도체의 정교한 공정기술의 접목을 통해, 두 회사는 CMOS 트랜지스터의 문턱전압 변동폭을 반으로 줄임으로써, 576kb SRAM이 약 0.4V에서 잘 동작하는 것을 보여 주었다. 이 기술은 기존의 SoC 설계 레이아웃, 바디 전압 조절과 같은 설계 기술, 양산 장비 툴 등의 기존 인프라와 호환이 잘 된다.

스케일링 법칙에 따라, CMOS 의 전원전압은 130nm 노드에서 대략 1.0V까지 꾸준히 감소되어 왔다. 그러나, 그 이후 공정기술이 130nm에서 28nm까지 계속해서 스케일 되고 있음에도 불구하고, 전원전압은 약 1.0V 정도에서 계속 머물고 있다. 다이나믹 파워는 전원전압의 제곱에 비례하기 때문에 전력소모는 CMOS 기술의 주요 쟁점이 되어 왔다. 전원전압 스케일링이 130nm 노드 이하에서 더 이상 줄어들지 않고 있는 이유는 랜덤 도펀트 변동 (RDF) 을 포함한 몇 가지 변동 요인들 때문이다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

후지쯔 반도체와 수볼타는, 수볼타의 파워슈링크(PowerShrink™) 저전력 CMOS 플랫폼을 후지쯔의 저전력 공정기술에 적용하여, 최소 전원전압이 0.425V까지 동작하는 초저전압 SRAM 블럭의 동작을 성공적으로 시연했다고 발표했다. 전력소모를 감소시켜주는 이 기술은 가까운 미래에 최상의 친환경적 제품 출시를 가능하게 해 줄 것이다. 본 기술에 대한 자세한 내용과 결과는 12월 5일부터 워싱턴 DC 에서 열린 2011년 국제전자소자학회 (IEDM)에서 발표됐다.

후지쯔 반도체와 수볼타는, 수볼타의 파워슈링크(PowerShrink™) 저전력 CMOS 플랫폼을 후지쯔의 저전력 공정기술에 적용하여, 최소 전원전압이 0.425V까지 동작하는 초저전압 SRAM 블럭의 동작을 성공적으로 시연했다고 발표했다. 전력소모를 감소시켜주는 이 기술은 가까운 미래에 최상의 친환경적 제품 출시를 가능하게 해 줄 것이다. 본 기술에 대한 자세한 내용과 결과는 12월 5일부터 워싱턴 DC 에서 열린 2011년 국제전자소자학회 (IEDM)에서 발표됐다.