수볼타는 2011년 국제전자소자학회 (IEDM)에서 발표할 자사의 DDC (Deeply Depleted Channel™) 저전력 트랜지스터 기술을 공개 했다. 파워슈링크 저전력 CMOS 플랫폼의 기초가 되는 수볼타의 DDC 기술은 동작속도에 영향을 주지 않으면서도 소비전력의 50%를 줄일 수 있게 해 주는 저전력 기술을 제공한다. 또한 보다 진보적인 전압 스케일링 기법과 함께 DDC 기술을 적용하면, 전력 소모를 80% 혹은 그 이상 줄일 수 있다.

수볼타의 사장 겸 대표이사인 브루스 맥윌리엄스(Bruce McWilliams) 박사는 “실리콘 측정 결과로 증명된 수볼타 기술은 반도체 업계에서 많은 관심을 불러 모으고 있다”며, “우리의 DDC 트랜지스터 기술을 좀더 상세하게 공개함으로써, 업계의 기술자들에게 어떻게 수볼타 기술이 전력소모를 감소시키고, 전원전압을 낮추며, 20nm 이하의 공정에서도 스케일링이 가능하게 하는 지를 보여 주고자 한다.”고 말했다.

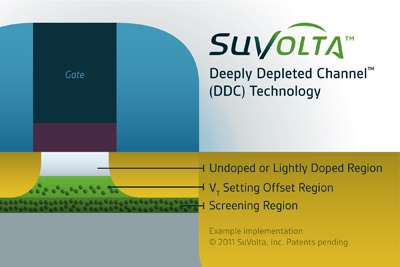

수볼타의 DDC 트랜지스터는 문턱전압 변화폭을 줄임으로써 지속적인 CMOS 스케일링을 가능하게 해 준다. 이 구조는 게이트에 전압이 가해졌을 때 깊게 공핍된 채널(Deeply Depleted Channel)의 형성을 통해 동작된다. DDC 채널의 전형적인 구조는 몇 가지 영역들, 즉, 도핑 되지 않았거나 혹은 매우 낮게 도핑 된 영역, 문턱전압 셋팅 오프셋 영역, 스크리닝 영역으로 이루어져 있다. 수볼타의 DDC 트랜지스터 구조 구현 방식은 반도체 웨이퍼 팹 시설 및 특정한 칩 설계 요구 조건에 따라 달라질 수 있다.

도핑 되지 않았거나 혹은 매우 낮게 도핑 된 영역은 채널의 도펀트를 제거함으로써 깊게 공핍된 채널을 이루게 한다. 이렇게 함으로써 랜덤 도펀트 변동(RDF)을 줄이고 VDD 스케일링을 가능하게 하며 모빌리티를 증가시켜서 유효전류를 크게 해준다.

문턱전압 셋팅 오프셋 영역은 채널 모빌리티를 감소시키지 않으면서 트랜지스터의 문턱전압 레벨을 셋팅 할 수 있게 한다. 이 영역은 기존 트랜지스터 대비해 VT 변화폭이 적어지도록 개선해 준다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>