알테라가 ARM 코어텍스-A9 기반 SoC FPGA 및 이 디바이스를 겨냥해서 특정 디바이스 임베디드 소프트웨어를 신속하게 개발할 수 있도록 지원하는 SoC FPGA ‘버추얼 타깃’이라는 가상설계 플랫폼도 제공한다.

알테라가 ARM 코어텍스-A9 기반 SoC FPGA 및 이 디바이스를 겨냥해서 특정 디바이스 임베디드 소프트웨어를 신속하게 개발할 수 있도록 지원하는 SoC FPGA ‘버추얼 타깃’이라는 가상설계 플랫폼도 제공한다.

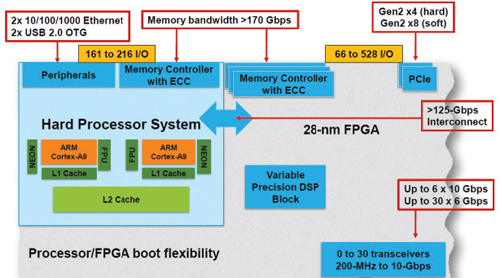

‘SoC FPGA’ 디바이스는 단일 칩으로, 28나노미터 사이클론V 또는 아리아V FPGA 패브릭과 듀얼 코어 ARM 코어텍스-A9 MPCore 프로세서, ECC 보호 메모리컨트롤러 및 주변 장치 그리고 고대역폭 인터커넥트를 통합한 ARM 기반 제품이다.

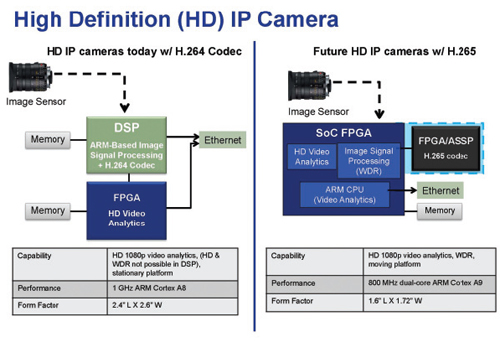

사용자들은 알테라의 SoC FPGA 개발 플로우를 이용해서 자동차, 산업용, 비디오 감시, 무선인프라, 컴퓨터, 스토리지 등의 다양한 분야의 애플리케이션용으로 임베디드 시스템의 보드 크기, 전력, 비용을 절감하면서 성능을 향상시키는 맞춤형 ARM 기반시스템을 빠르게 작성할 수 있다. 또한 소프트웨어 개발 툴, 디버거, 운영체제, 미들웨어, 애플리케이션을 포함한 ARM의 풍부한 에코시스템을 활용할 수도 있다.

ARM 프로세서부문 마케팅 부사장인 짐 니콜라스는 “28나노 프로세스 기술을 기반으로 한 이들 SoC FPGA 제품은 향상된 성능과 용량으로 전혀 새롭고 흥미로운 임베디드 시스템을 개발할 수 있도록 할 것이다. 이들 디바이스 제품은 임베디드 시스템 디자이너들이 출시 시간을 단축하고, 비용을 절감하고, 에너지 효율을 향상시킬 수 있도록 할 뿐만 아니라 ARM 소프트웨어 에코시스템의 포괄적인 지원을 활용할 수 있도록 할 것”이라고 말했다.

이 프로세서 시스템은 1.8와트 미만으로 4,000DMIPS에 이르는 피크 성능을 제공한다. 프로세서 시스템과 FPGA 패브릭을 개별적으로 구동할 수 있으며, 어떠한 순서로나 구성하고 부팅할 수 있다. 작동을 시작한 다음에는 필요에 따라서 FPGA 부분의 전력을 낮춤으로써 시스템 전력을 절약할 수 있다.

코어텍스-A9 MPCore 프로세서 시스템과 FPGA를 쓰루 풋이 높은 데이터패스로 인터커넥트함으로써 데이터 일관성과 함께 125Gbps 이상의 피크대역폭을 달성한다. 이와 같은 수준의 성능은 2칩 솔루션으로는 달성할 수 없는 것이다. 또한 통합적인 단일칩 SoC FPGA로서 보드 디자이너들이 프로세서와 FPGA 사이에 외부적인 I/O 경로를 제거할 수 있으므로 시스템 전력을 크게 절약할 수 있다.

알테라의 SoC FPGA 제품

이들 SoC FPGA 제품은 알테라의 28나노 제품 포트폴리오를 활용한다. 이들 FPGA 제품은 프로세스 기술, 트랜시버기술, I/O 자원, 하드 IP 등의 측면에서 혁신을 이룸으로써 사용자들의 전력, 성능 및 비용 요구를 충족할 수 있도록 설계되었다.

알테라는 사이클론V 및 아리아V SoC FPGA 제품들을 제공함으로써 임베디드 프로세싱 시장을 위한 제품 포트폴리오를 더욱더 다양화할 수 있게 되었다. 이들 사이클론V 및 아리아V SoC FPGA 제품은 저전력 28나노 프로세스를 기반으로 한다. 이들 제품은 각기 최대 5Gbps 및 10Gbps로 동작하는 임베디드 트랜시버를 포함한다. FPGA 패브릭으로는 가변 정밀도DSP블록과 최대 3개 ECC 보호 메모리컨트롤러를 포함한다.

사이클론V SoC FPGA는 최대110KLE

(logic element)를 제공하며 시스템비용과 전력이 업계에서 가장 낮은 수준이며 차세대 산업용 ‘drive on a chip’, 첨단 운전자 지원, 비디오 감시 등의 대량수량애플리케이션을 차별화하기에 적합한 높은 수준의 성능을 제공한다.

그리고 아리아V SoC FPGA 제품은 중급 수준 애플리케이션에 이용할 수 있도록 가격과 성능을 절충시켰으며 총 전력이 아주 낮은 제품들이다. 이들 디바이스 제품은 최대 460KLE를 제공하며 원격 무선 헤드, LTE 기지국, 다기능 프린터 같은 애플리케이션의 높은 성능 요구를 충족할 수 있도록 설계되었다.

SoC FPGA 개발환경

알테라의 SoC FPGA는 하드웨어 팀과 소프트웨어 팀이 코어텍스-A9 MPCore 프로세서와 FPGA를 지원하는 공통적인 툴 및 개발 플로우를 이용함으로써 생산성을 극대화할 수 있도록 한다.

디자이너들이 알테라의 Quartus II 소프트웨어를 이용해서 맞춤형 주변 장치와 하드웨어 가속화기를 작성하고 이들을 알테라의 Qsys 시스템통합 툴을 이용해서 프로세서 시스템과 통합할 수 있다.

Qsys툴이 IP(intellectual property) 기능과 서브 시스템을 접속하기 위한 인터커넥트로 직을 자동으로 작성하므로 하드웨어 설계작업을 가속화할 수 있다. Qsys가 FPGA 최적화 NoC (network-on- a-chip) 인터커넥트를 자동으로 작성하므로 더욱더 뛰어난 성능을 달성하고 디자인 재사용을 향상시킬 수 있으며 더욱더 빠르게 검증이 가능하다.

Qsys는 ARM의 아발론 메모리-Mapped, 아발론 스트리밍, AMBA AXI 등의 산업표준 인터페이스를 지원하므로 사용자가 단일 디자인으로 다양한 인터페이스를 이용하는 IP코어들을 활용하고 재사용할 수 있다.

SoC FPGA 버추얼 타깃

한편 SoC FPGA 버추얼 타깃을 이용해서 SoC FPGA를 기반으로 한 시스템에 이용하기 위한 소프트웨어를 빠르게 개발할 수 있다.

빈스 후 알테라의 제품 및 마케팅 부사장은 “알테라는 고성능 프로세싱 시스템, 저전력 28나노 FPGA 패브릭, 하드웨어-소프트웨어 개발 플로우, 버추얼 타깃 개발 플랫폼을 결합함으로써 SoC 기술의 새로운 기준을 제시하고 있다. 알테라의 전반적인 임베디드 사업의 일환으로서 SoC FPGA는 임베디드 개발자들을 위해서 시스템 성능, 전력, 비용, 보드 크기 면에서 대대적인 향상을 달성하고 있다”고 말했다.

또 그는 “임베디드 프로젝트에 이용하기 위한 애플리케이션 소프트웨어를 개발하기 위해서는 많은 시간과 엔지니어링 자원을 필요로 한다. 우리 회사의 SoC FPGA 버추얼 타깃을 이용함으로써 엔지니어들이 소프트웨어 개발에 신속하게 착수할 수 있을 것이며 생산성을 극대화하고 신속하게 제품을 시장에 내놓을 수 있을 것”이라고 말했다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>