FPGA 레벨에서 신속한 개발을 BDTI가 검증

알테라의 모델 기반 부동소수점 DSP 설계 플로가 검증되었다.

BDTI가 독립적인 분석을 통해 알테라의 Stratix 및 Arria FPGA 제품군에서의 부동소수점 DSP 설계 구현의 높은 성능, 효율, 편의성 등을 검증한 보고서를 최근 발표한 것.

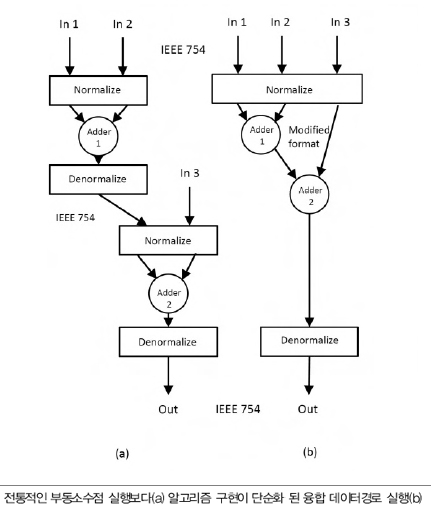

BDTI의 보고서는 ‘기본적인 부동소수점 연산자 등으로 구성된 데이터경로를 구축하는 것보다 부동소수점 컴파일러가 기본적인 연산자들을 단일 기능 또는 데이터경로로 통합한 융합 데이터경로(fused datapath)를 생성하며, 이로써 전통적인 부동소수점 FPGA 설계에서 나타나는 불필요한 중복들이 제거된다. 그리고 융합 데이터경로 방법론을 통해 복잡한 부동소수점 데이터경로들을 이전에 가능했던 것보다 높은 성능과 효율을 제공하도록 구현할 수 있다’고 결론지었다.

이번에 시연된 FPGA 상에서의 부동소수점 DSP 설계 플로는 알테라의 업계 최초 모델 기반 부동소수점 최신 설계 툴이다.

알테라 부동소수점 DSP 설계 플로는 DSP Builder Advanced Blockset에 통합된 부동소수점 DSP 컴파일러, Quartus II RTL 툴 체인, ModelSim 시뮬레이터와 FPGA 상에서 DSP 알고리즘 구현 과정을 단순화시켜주는 매스웍스의 MATLAB, Simulink 툴을 포함하고 있다.

부동소수점 설계 플로는 알고리즘 모델링 및 시뮬레이션, RTL 생성, 신세시스, 배치 및 배선(place-and-route) 등의 기능과 설계 검증 단계들을 통합하고 있다. 이러한 통합으로 알고리즘 레벨은 물론 FPGA 레벨에서 신속한 개발과 설계 공간 탐색이 가능하기 때문에 궁극적으로는 전체 설계 활동을 줄여준다.

알테라의 제품 및 기업 마케팅 담당 부사장인 빈스 후는 “알테라의 하이 레벨 DSP 모델 기반 플로를 사용하여 설계자들은 전통적인 HDL-기반 설계를 통해 가능한 것보다 효율적이면서도 신속하게 부동소수점 알고리즘을 구현 및 검증할 수 있다”면서 “일단 알고리즘을 하이 레벨에서 모델링 및 디버그하고 나면 설계를 간편하게 신세시스하여 어떠한 알테라 FPGA에도 적용할 수 있다”고 설명했다.

알테라의 새로운 설계 플로는 부동소수점이 제공하는 동적 영역을 일반적으로 필요로 하는 어려운 선형 대수학 문제들에 적합하다. BDTI는 파라미터화가 가능한 부동소수점 역행렬 설계를 벤치마크했다. 역행렬은 레이더 시스템, MIMO 무선 시스템, 의료용 이미징 등을 포함한 다양한 DSP 애플리케이션에서 사용되는 대표적인 처리 형태이다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>