[기고] 넓은 대역폭의 애플리케이션에서 제로 드리프트 증폭기를 활용하는 방법

2023-02-07 사이먼 바실리코(Simon Basilico) 설계 엔지니어, 아나로그디바이스(Analog Devices, Inc.)

이 글에서는 제로 드리프트 연산 증폭기(zero-drift operational amplifier) 사용과 관련하여 쵸핑(chopping)과 오토 제로(auto-zeroing)에 대한 간단한 개념, 그리고 제로 드리프트 아티팩트의 발생원에 대해서 설명하고, 증폭기 설계 엔지니어가 이러한 영향을 줄이기 위해 사용할 수 있는 몇 가지 기법들을 간단하게 살펴본다.

이와 함께 정밀 신호 체인에서 잔류 AC 아티팩트의 영향을 최소화할 수 있는 방법으로서, 입력 소스 임피던스 매칭, 필터링, 주파수 계획 등에 대해 설명한다.

제로 드리프트 연산 증폭기는 쵸핑이나 오토 제로, 또는 이 두 가지 기법을 조합하여 사용함으로써 오프셋이나 1/f 잡음 같은 원치 않는 저주파 오차를 제거한다. 기존에는 이들 증폭기가 낮은 대역폭에서 동작하는 애플리케이션에 주로 사용되어 왔다. 이러한 동적 기법들이 보다 높은 주파수대에서 아티팩트를 발생하기 때문이다. 하지만 리플, 글리치, 상호변조 왜곡(IMD) 같은 고주파 오차들을 고려해서 시스템을 설계하기만 한다면 넓은 대역폭에서 동작하는 애플리케이션에서도 제로 드리프트 연산 증폭기의 뛰어난 DC 성능을 유용하게 활용할 수 있다.

다양한 제로 드리프트 기법들

쵸핑(chopping)1-7

첫 번째 제로 드리프트 기법으로서 쵸핑을 들 수 있는데, 이는 오차를 보다 높은 주파수로 변조함으로써 오프셋과 저주파 잡음을 신호와 분리하는 것이다.

그림 1은 쵸핑이 입력 신호(파란색 파형)를 구형파로 변조하고, 이 신호를 증폭기로 처리한 다음(b), 출력단에서 다시 DC로 복조하는 방법(c)을 보여준다. 이와 동시에 증폭기의 저주파 오차(빨간색 파형)는 출력단에서 구형파로 변조되며(c), 그런 다음에 저역통과 필터(LPF)를 사용해 필터링된다(d).

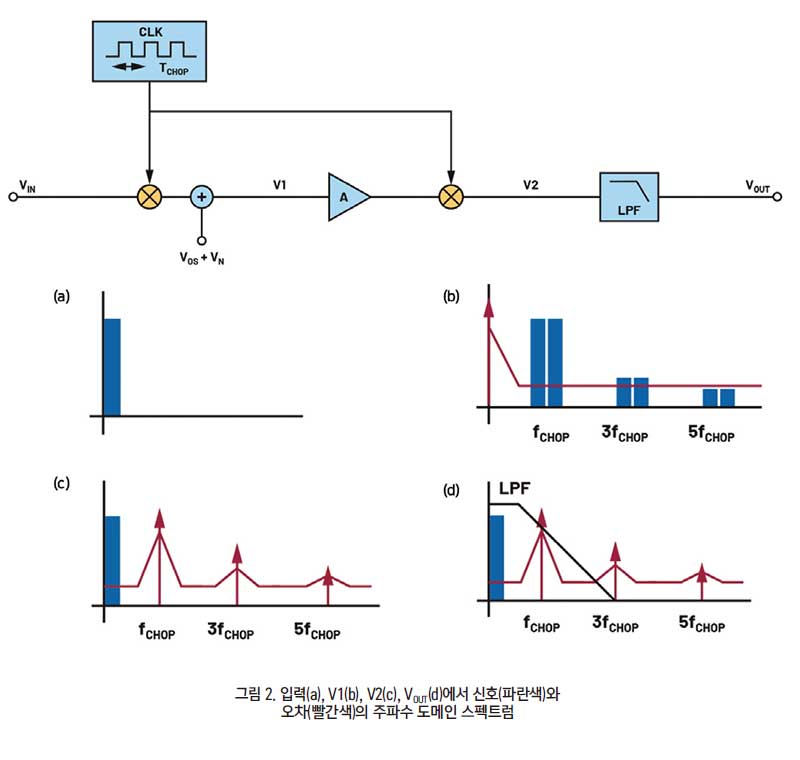

마찬가지로 주파수 도메인에서도 입력 신호(그림 2에서 파란색 신호)를 쵸핑 주파수로 변조하고, fCHOP에서 이득 스테이지로 처리하고(b), 출력단에서 다시 DC로 복조한 다음(c), 마지막으로 LPF를 사용해서 필터링한다(d). 이 증폭기의 오프셋과 잡음 소스(그림 2에서 빨간색 신호)는 이득 스테이지를 통해서 DC로 처리되고, 출력 쵸핑 스위치를 사용해서 fCHOP으로 변조되며(c), LPF를 사용해서 필터링된다(d). 구형파 변조를 사용하기 때문에 변조 주파수의 홀수 배수 부근에서 변조가 일어난다.

주파수 도메인과 시간 도메인 그림에서 볼 수 있듯이, LPF가 현실적으로 이상적일 수 없으므로 변조 잡음과 오프셋으로 인한 약간의 잔류 오차가 있을 수 있다.

오토 제로(auto-zero)1-3, 5-7

두 번째 제로 드리프트 기법으로서, 오토 제로는 증폭기에서 저주파 오차 소스를 샘플링하고 차감하는 식으로 작동하는 동적 교정 기법이다.

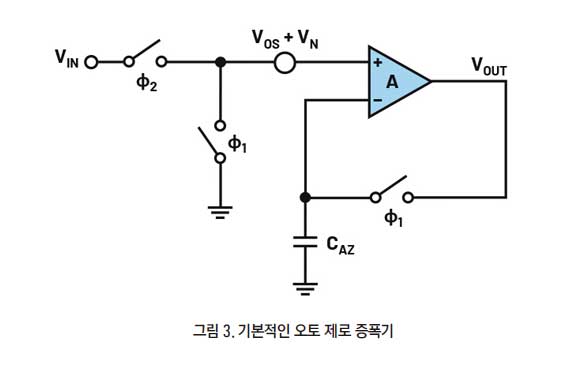

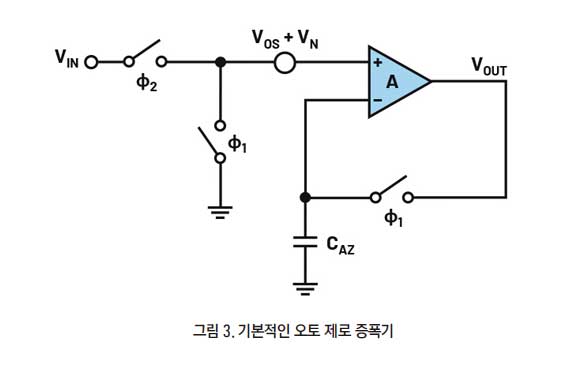

그림 3은 기본적인 오토 제로 증폭기를 보여준다. 이는 오프셋과 잡음을 포함하는 증폭기, 입력과 출력을 재구성하기 위한 스위치, 오토 제로 샘플링 커패시터로 구성된다.

오토 제로 구간인 φ1에는 회로 입력이 공통 전압으로 단락되고 오토 제로 커패시터가 입력 오프셋 전압과 잡음을 샘플링한다. 이 구간에서는 증폭기가 신호 증폭을 하지 못한다. 오토 제로 증폭기가 연속적으로 동작하기 위해서는 2개의 동일한 채널을 인터리브해야 한다. 이것을 ‘핑퐁 오토 제로’라고 한다.

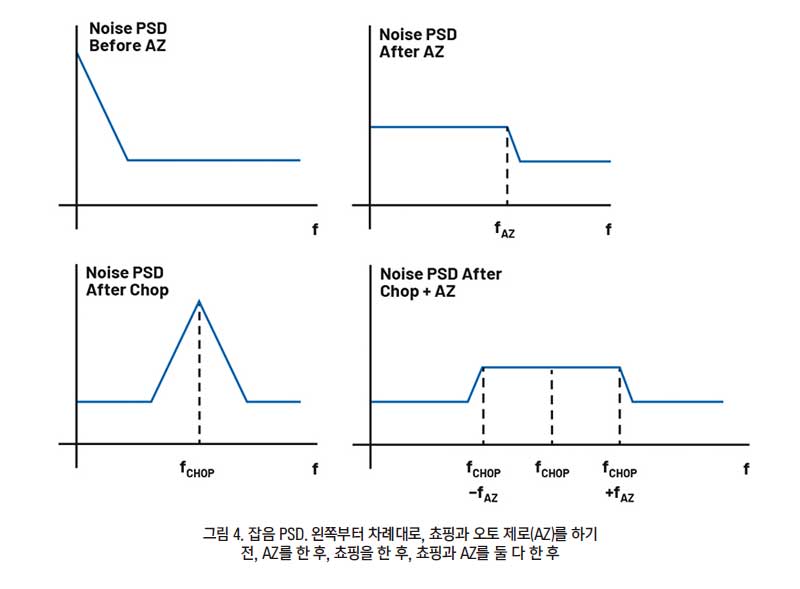

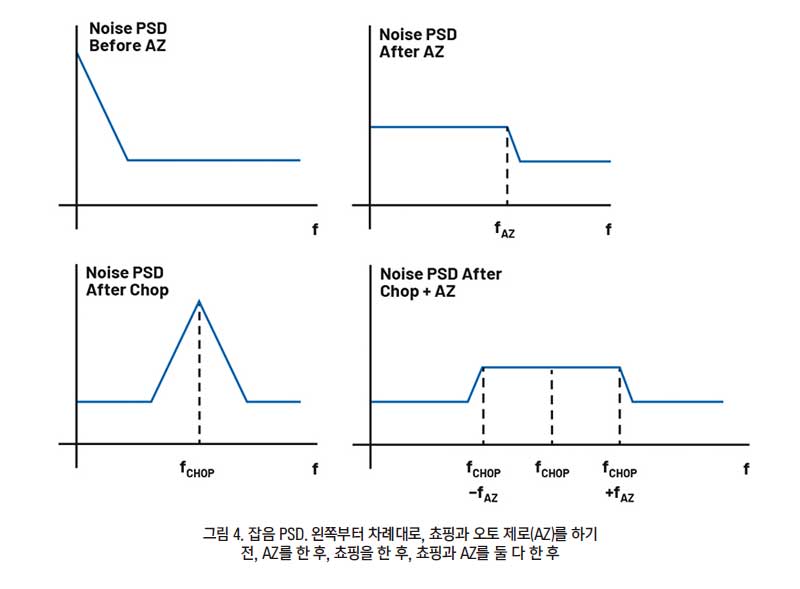

증폭 구간인 φ2에는 입력이 다시 신호 경로로 연결되고 증폭기가 신호를 증폭할 수 있다. 오토 제로에 의해서 저주파 잡음, 오프셋, 드리프트가 제거되며, 잔류 오차는 전류 값과 이전 오차 샘플 사이의 차이다. 저주파 오차 소스들은 φ1에서 φ2가 되면서 그리 많이 달라지지 않으므로 이 같은 차감 방식이 효과적으로 작동한다. 반면에 고주파 잡음은 베이스밴드로 에일리어싱되며, 그 결과 백색 잡음 플로어는 증가한다(그림 4).

잡음 폴딩이 있고 연속 동작을 위해 추가적인 채널을 필요로 한다는 점에서, 독립형 연산 증폭기에는 쵸핑이 좀더 전력 효율적인 제로 드리프트 기법일 수 있다.

쵸핑 아티팩트1-3, 5-7

쵸핑은 원치 않는 오프셋, 드리프트, 1/f 잡음을 제거하는 데에는 효과적이지만, 출력 리플이나 글리치 같은 원치 않는 AC 아티팩트를 만든다. 아나로그디바이스(Analog Devices)의 최신 제로 드리프트 제품들은 이러한 아티팩트의 크기를 줄이고 보다 높은 주파수대로 위치시키는 조치들을 도입함으로써 시스템 차원에서 필터링을 수월하게 한다.

리플 아티팩트

리플은 저주파 오차들을 쵸핑 주파수의 홀수 고조파로 이동시키는 쵸핑 변조 기법에서 기본적으로 수반되는 결과이다. 증폭기 설계 엔지니어는 다음과 같은 방법들을 사용해서 리플의 영향을 줄일 수 있다.

• 생산 시에 오프셋 트리밍: 일회성으로 일차적인 트리밍을 실시함으로써 공칭 오프셋을 크게 낮출 수 있다. 하지만 오프셋 드리프트와 1/f 잡음은 남는다.

• 쵸핑과 오토 제로 결합: 증폭기에 먼저 오토 제로를 실시하고 그 다음에 쵸핑을 실시해서 높아진 잡음 스펙트럼 밀도(NSD)를 더 높은 주파수대로 상향변조한다. 그림 4는 쵸핑과 오토 제로를 거친 후의 잡음 스펙트럼 결과를 보여준다.

• 자동교정 피드백(ACFB): 로컬 피드백 루프를 사용해서 출력단에서 변조된 리플을 검출하고 소스단에서 저주파 오차를 제거할 수 있다.

글리치 아티팩트

글리치는 쵸핑 스위치들에 의해 야기되는 전하 주입 불일치로 인해서 발생하는 순간적 스파이크이다. 이러한 글리치의 크기는 소스 임피던스와 전하 불일치 양 같은 여러 요인에 따라서 좌우된다.1

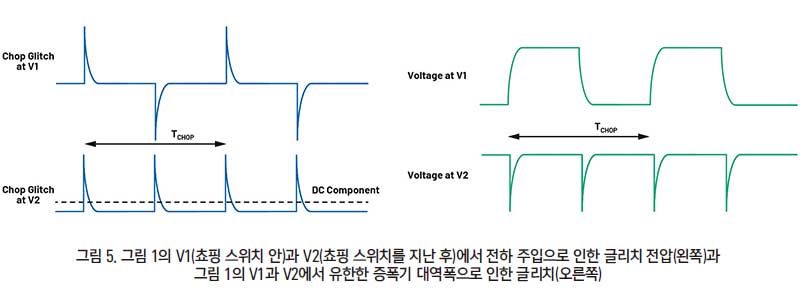

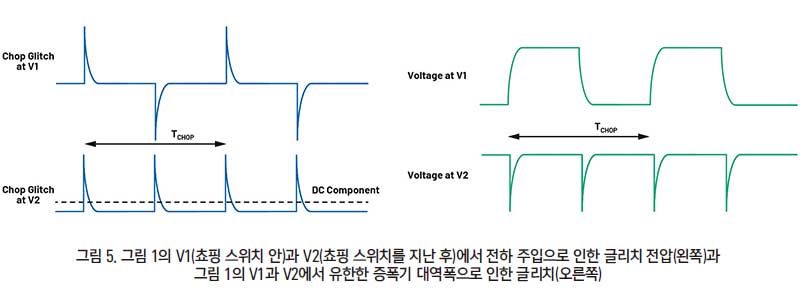

글리치 스파이크는 쵸핑 주파수의 짝수 고조파에 아티팩트를 일으킬 뿐만 아니라 잔류 DC 오프셋을 발생하는데, 이는 쵸핑 주파수에 비례한다. 그림 5의 왼쪽은 그림 1의 V1(쵸핑 스위치 안)과 V2(출력 쵸핑 스위치를 지난 후)에서 이러한 스파이크가 어떤 모습인지 보여준다. 그림 5의 오른쪽에서는 유한한 증폭기 대역폭으로 인해서 쵸핑 주파수의 짝수 고조파에 추가적인 글리치 아티팩트가 발생한다는 것을 알 수 있다.

리플과 마찬가지로, 증폭기 설계 엔지니어들은 다음과 같은 방법을 사용해서 제로 드리프트 증폭기에서 글리치의 영향을 낮출 수 있다:

• 전하 주입 트리밍: 쵸핑 증폭기의 입력에 주입되는 전하를 조절해서 전하 불일치를 보정할 수 있는데, 이는 연산 증폭기 입력단에서 입력 전류의 양을 줄여준다.

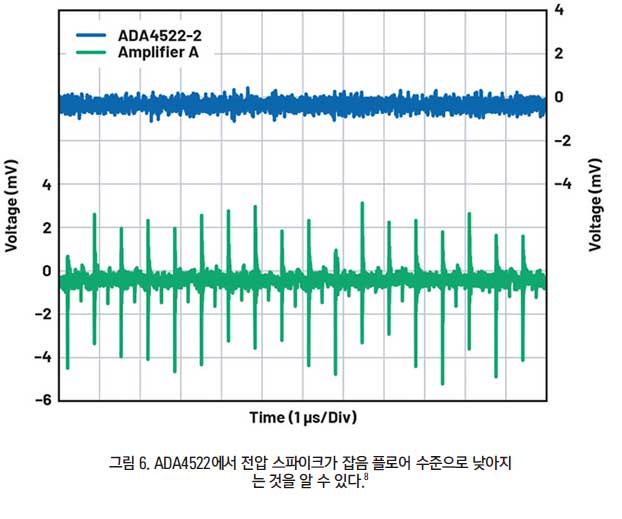

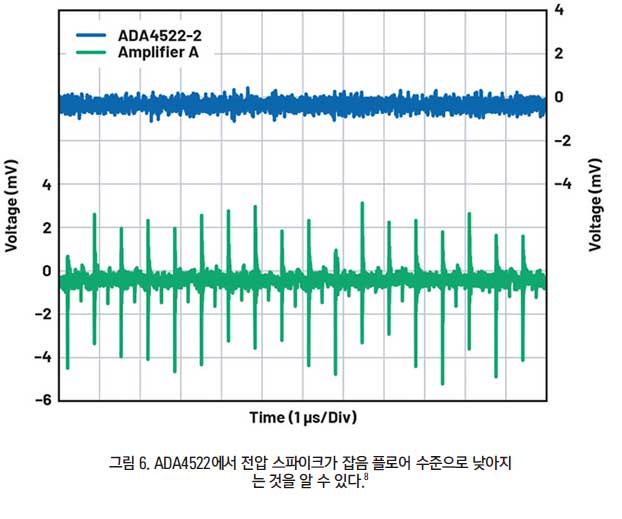

• 다중채널 쵸핑: 이 방법은 글리치의 크기를 줄일 뿐 아니라 글리치를 더 높은 주파수대로 이동시킴으로써 필터링을 수월하게 한다. 이 방법은 단순히 쵸핑을 더 높은 주파수에서 실시하는 것에 비해 글리치를 좀더 빈번하게 하면서 크기도 더욱 줄인다. 그림 6은 통상적인 제로 드리프트 증폭기와 ADA4522를 비교한 것으로, 이 기법을 사용해서 어떻게 글리치의 영향을 크게 낮출 수 있는지 보여준다.

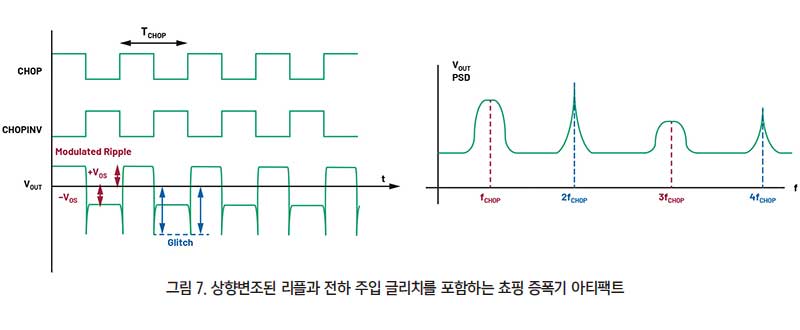

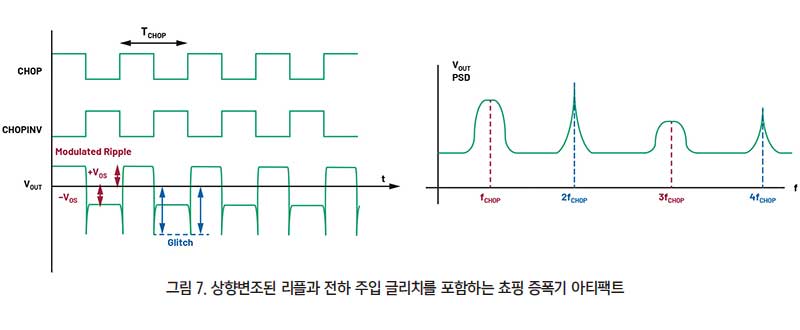

그림 7에서는 쵸핑 증폭기 출력 전압에 다음과 같은 아티팩트가 발생한다는 것을 알 수 있다:

• 상향변조 오프셋으로 인한 리플과 쵸핑 주파수의 홀수 배수에서 나타나는 1/f

• 쵸핑 스위치들의 전하 주입 불일치로 인한 글리치와 유한한 증폭기 대역폭으로 인해 쵸핑 주파수의 짝수 배수에 나타나는 글리치

시스템 차원의 설계 고려사항

데이터 수집 시스템에 제로 드리프트 증폭기를 사용할 때는 어느 위치에서 주파수 아티팩트가 발생하는지 이해하고 그에 따라서 적절히 설계할 필요가 있다.

데이터 시트에서 쵸핑 주파수 구하기

통상적으로 쵸핑 주파수는 데이터 시트에 명시적으로 표기 되는데, 잡음 스펙트럼 플롯으로부터 구할 수도 있다. ADI의 몇몇 최신 제로 드리프트 증폭기 제품의 데이터 시트에서는 스펙트럼 상의 어느 지점에서 아티팩트가 발생하는지 명확히 표기하고 있다.

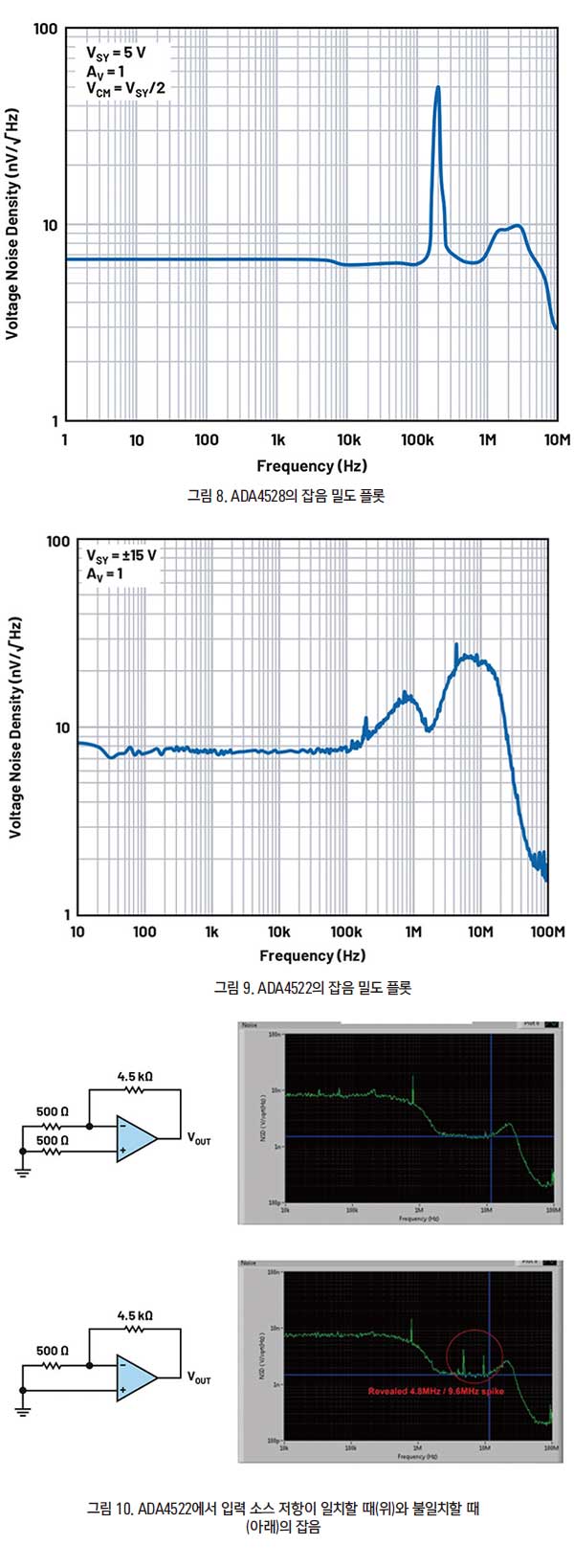

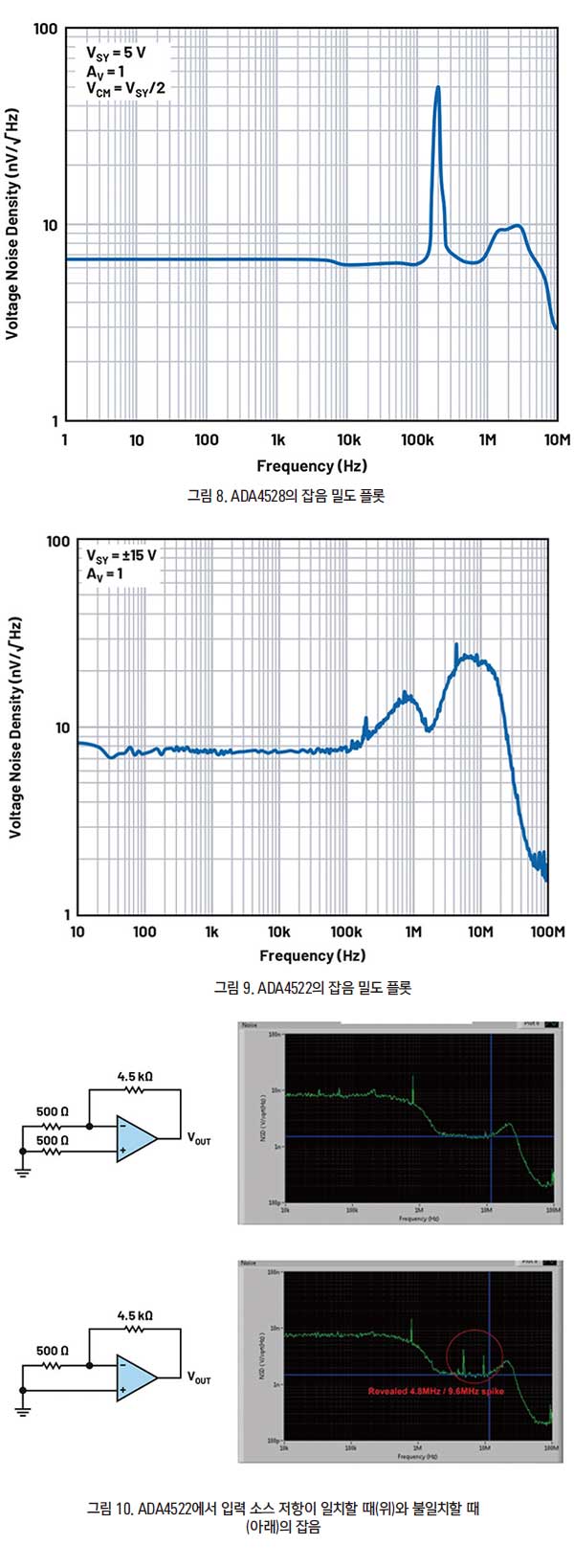

ADA4528 데이터 시트에서는 “애플리케이션 정보(Application Information)” 부분에서 쵸핑 주파수를 200kHz로 표기하고 있을 뿐만 아니라, 그림 8의 잡음 밀도 플롯에서도 이것을 알 수 있다.

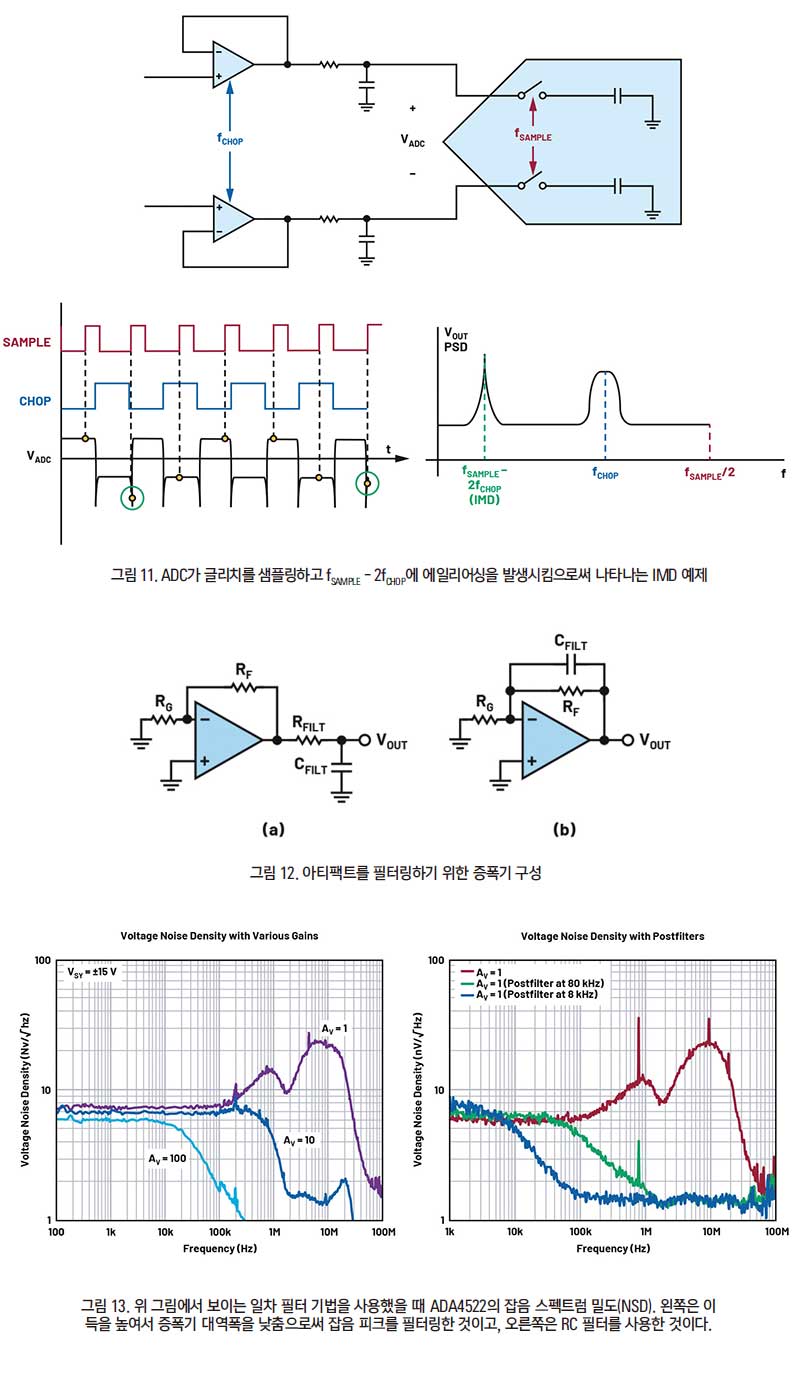

ADA4522 데이터 시트의 “작동 원리(Theory of Operation)” 부분에서는 오프셋 및 리플 교정 루프를 800kHz로 실행할 때의 쵸핑 주파수를 4.8MHz로 표기하고 있다. 그림 9는 ADA4522의 잡음 밀도를 보여주는데, 어느 위치에서 잡음 피크들이 발생하는지 알 수 있다. 6MHz에서도 잡음 범프가 발생하는 것을 볼 수 있는데, 이는 단위 이득일 때 이 루프의 위상 마진 감소로 인한 것으로서 제로 드리프트 증폭기에서만 일어나는 것이 아니다.

한 가지 유의할 점은, 데이터 시트에 표기되어 있는 주파수는 정격 수치로서, 부품마다 약간의 차이가 있을 수 있다는 것이다. 그러므로 만약에 자신의 시스템에 차동 신호 컨디셔닝을 위해서 2개의 쵸핑 증폭기가 필요한 경우에는 듀얼 증폭기를 사용하는 것이 좋다. 2개의 단일 증폭기를 사용하면 쵸핑 주파수가 약간 다르기 때문에 두 주파수가 상호작용하고 추가적인 IMD를 발생시킨다.

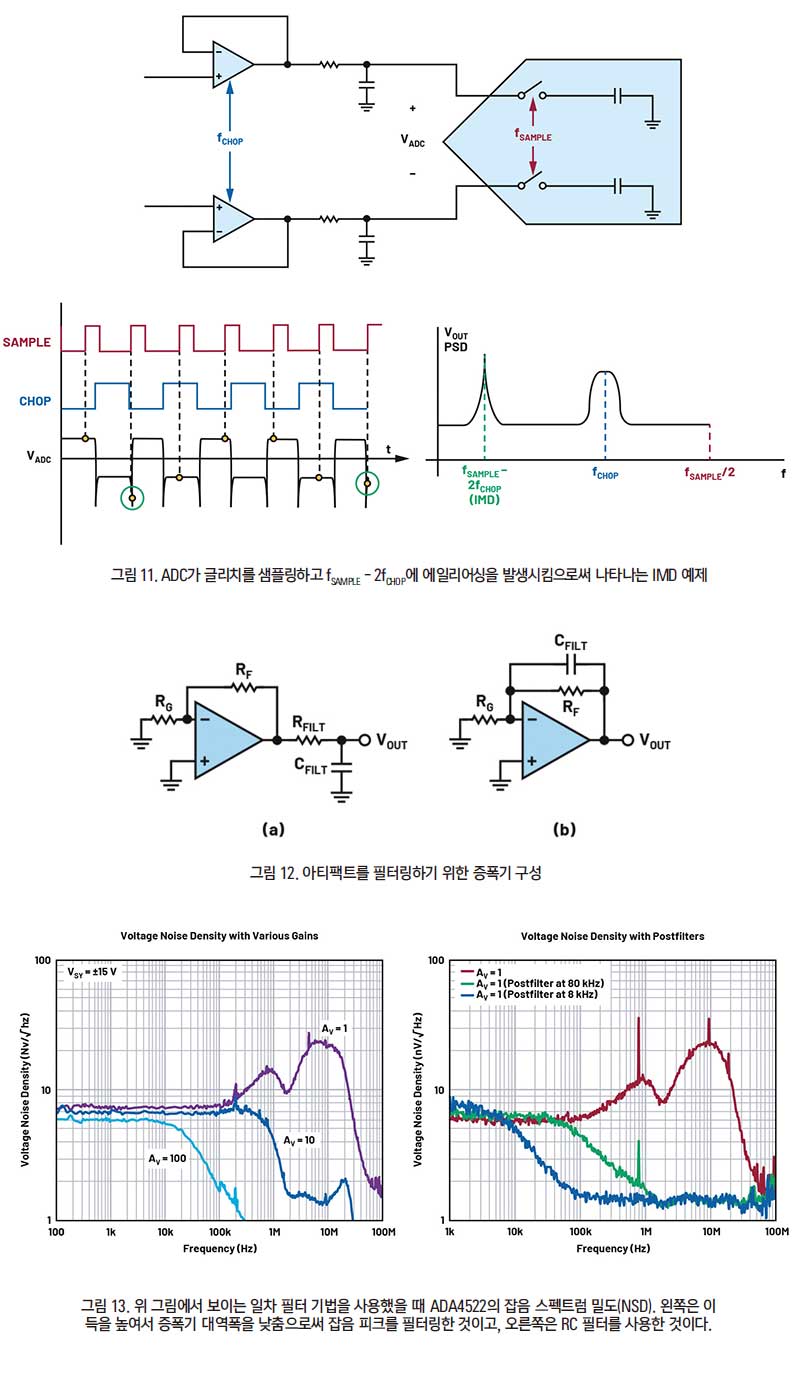

입력 소스 임피던스 매칭

순간 전류로 인한 글리치가 입력 소스 임피던스와 상호작용해서 차동 전압 오차를 일으킬 수 있는데, 이는 잠재적으로 쵸핑 주파수의 배수에 추가적인 아티팩트를 일으킬 수 있다. 그림 10에서는 ADA4522의 잡음 밀도 플롯에서 소스 저항 불일치로 인한 스파이크가 발생하는 것을 볼 수 있다(아래). 이 잠재적 오차 요인을 완화하기 위해서는 쵸핑 증폭기의 양쪽 입력에 보여지는 임피던스를 동일하게 해야 한다(위).

IMD와 에일리어싱 아티팩트

쵸핑 증폭기를 사용할 때 입력 신호가 쵸핑 주파수 fCHOP과 믹스되어서 fIN ± fCHOP, fIN ± 2fCHOP, 2fIN ± fCHOP…에서 IMD를 발생시킬 수 있다. 특히 fIN이 쵸핑 주파수에 근접할수록 이러한 IMD 성분들이 관심 대역으로 유입될 수 있다. 이러한 문제를 피하기 위해서는 쵸핑 주파수가 입력 신호 대역폭보다 훨씬 높은 제로 드리프트 증폭기를 선택하고 증폭기 스테이지에 앞서서 fCHOP에 가까운 주파수들에서 간섭 요인들을 필터링하도록 한다.

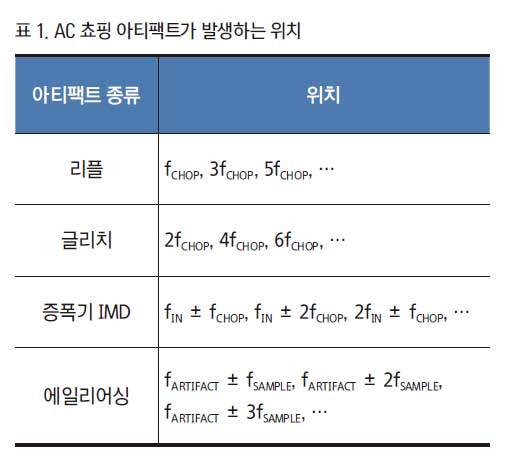

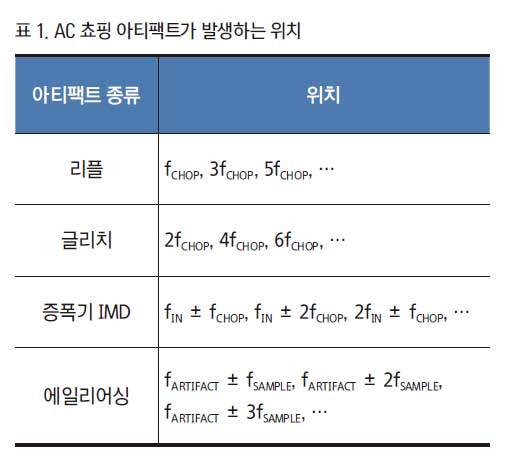

또한 증폭기 출력을 ADC를 사용해서 샘플링 할 때 쵸핑 아티팩트가 에일리어싱 될 수 있다. 그림 11은 ADC가 샘플을 취할 때 글리치 주파수 에일리어싱으로 인한 IMD 성분들을 보여준다. 이러한 IMD 성분은 글리치와 리플 크기에 따라 좌우되며 부품마다 약간씩 차이가 있을 수 있다. 그러므로 신호 체인을 설계할 때 이러한 IMD를 줄이기 위해서는 ADC 전위에 에일리어싱 방지 필터를 포함할 필요가 있다.

쵸핑 아티팩트 필터링

시스템 차원에서 이러한 고주파 아티팩트를 처리할 수 있는 가장 효과적인 방법은 필터링을 하는 것이다. 제로 드리프트 증폭기와 ADC 사이에 LPF를 사용해서 쵸핑 아티팩트를 줄이고 에일리어싱을 방지할 수 있다. 이러한 이유로, 쵸핑 주파수가 높은 증폭기는 LPF의 요구조건을 완화하고 더 넓은 신호 대역폭을 가능하게 한다.

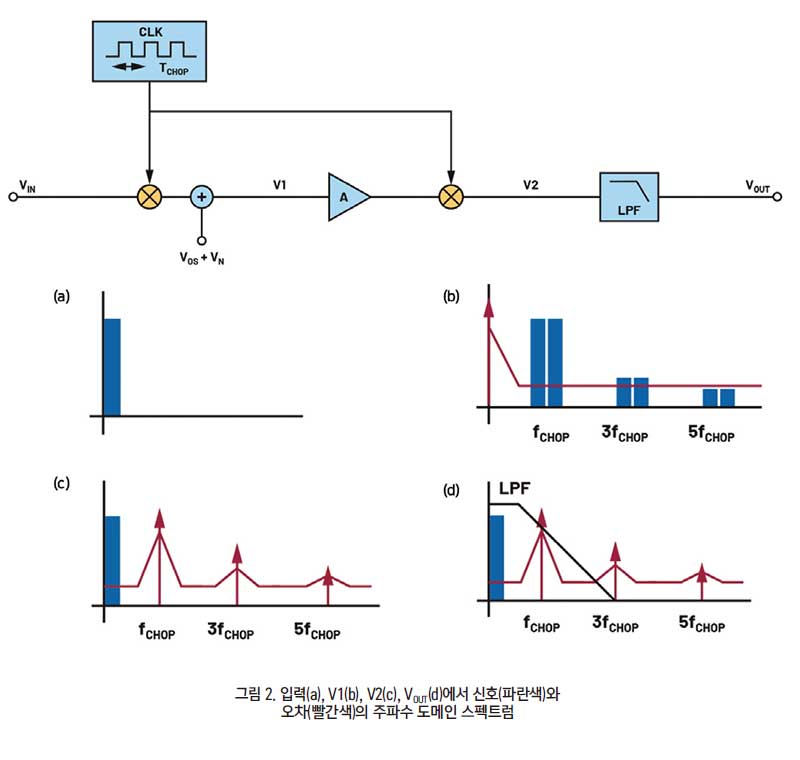

이러한 예로서 그림 13은 ADA4522로 그림 12의 기법들을 사용해서 쵸핑 아티팩트를 완화했을 때의 효과를 보여준다. 기법들은 폐쇄 루프 이득을 높이고, 후위 필터링을 하고, 피드백 저항과 병렬로 커패시터를 사용하는 것이다.8

시스템에서 얼마나 많은 대역외 제거가 필요한가에 따라서 더 높은 차수의 능동 필터가 필요할 수 있다. ADI는 필터 설계를 돕기 위해서 다중 피드백 필터 튜토리얼과 온라인 필터 설계 툴 같은 자원을 제공한다.

쵸핑 아티팩트가 어디에서 발생할지를 이해함으로써 필요한 필터를 설계할 수 있다. 표 1은 제로 드리프트 증폭기로 인해서 어느 위치에서 AC 아티팩트가 발생할지를 보여준다.

맺음말

제로 드리프트 증폭기에서 고주파 아티팩트를 이해함으로써 넓은 대역폭으로 동작하는 애플리케이션에서도 제로드리프트 연산 증폭기를 좀더 확신을 가지고 사용할 수 있다. 그러기 위해서는 다음과 같은 점들을 고려해서 시스템을 설계해야 한다:

• 제로 드리프트 증폭기의 양쪽 입력에 보여지는 소스입력 임피던스 매칭

• 차동 신호 컨디셔닝을 위해서 듀얼 증폭기 사용

• 데이터 시트에서 잡음 스펙트럼을 확인해서 아티팩트의 주파수 위치 이해

• 동적 오프셋 감소 기법에 수반되는 고주파 아티팩트의 영향을 줄이도록 필터 설계

• 주파수 도메인에서 고주파 아티팩트를 이해하고 그에 따라서 계획

참고 문헌

1. Yoshinori Kusuda. “Reducing Switching Artifacts in Chopper Amplifiers.” Delft University of Technology, the Netherlands, May 2018.

2. Christian Enz and Gabor C. Temes. “Circuit Techniques for Reducing the Effects of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization.” Proceedings of the IEEE, Vol. 84, No. 11, November 1996.

3. Boris Murmann. EE315A: VLSI Signal Conditioning Circuits: Chaper 7, Precision Analog Circuit Techniques. Stanford University, 2014.

4. James Bryant. “Multipliers vs. Modulators.” Analog Dialogue, Vol. 47, June 2013.

5. A. T. K. Tang. “A 3/spl mu/V Offset Operational Amplifier with 20nV//spl radic/Hz Input Noise PSD at DC Employing Both Chopping and Autozeroing.” IEEE, February 2002.

6. Michiel Pertijs and Wilko J. Kindt. “A 140 dB-CMRR Current-Feedback Instrumentation Amplifier Employing Ping-Pong Auto-Zeroing and Chopping.” IEEE Journal of Solid-State Circuits, Vol. 45, No. 10, October 2010.

7. Johan F. Witte, Kofi A. A. Makinwa, and Johan H. Huijsing. “A CMOS Chopper Offset-Stabilized Opamp.” IEEE Journal of Solid-State Circuits, Vol. 42, No. 7, July 2007.

8. Yoshinori Kusuda and Vicky Wong. “Zero-Drift Amplifiers: Now Easy to Use in High Precision Circuits.” Analog Dialogue, Vol. 49, July 2015.

ADA4523 data sheet. Analog Devices, Inc., April 2020.

AD7768-1 data sheet. Analog Devices, Inc., May 2019.

Kusuda, Yoshinori. “Analysis of Input Current Noise with Even Harmonics Folding Effect in a Chopper Op Amp.”

Analog Dialogue, Vol. 53, May 2019.

저자 소개

사이먼 바실리코(Simon Basilico)는 아나로그디바이스(Analog Devices) 정밀 신호 체인 그룹의 설계 엔지니어이다(캘리포니아주 산타클라라). 통합 혼합신호 설계와 시스템-인-패키지(SiP) 솔루션을 비롯해서 정밀 신호 체인을 주로 맡고 있다.

이와 함께 정밀 신호 체인에서 잔류 AC 아티팩트의 영향을 최소화할 수 있는 방법으로서, 입력 소스 임피던스 매칭, 필터링, 주파수 계획 등에 대해 설명한다.

제로 드리프트 연산 증폭기는 쵸핑이나 오토 제로, 또는 이 두 가지 기법을 조합하여 사용함으로써 오프셋이나 1/f 잡음 같은 원치 않는 저주파 오차를 제거한다. 기존에는 이들 증폭기가 낮은 대역폭에서 동작하는 애플리케이션에 주로 사용되어 왔다. 이러한 동적 기법들이 보다 높은 주파수대에서 아티팩트를 발생하기 때문이다. 하지만 리플, 글리치, 상호변조 왜곡(IMD) 같은 고주파 오차들을 고려해서 시스템을 설계하기만 한다면 넓은 대역폭에서 동작하는 애플리케이션에서도 제로 드리프트 연산 증폭기의 뛰어난 DC 성능을 유용하게 활용할 수 있다.

다양한 제로 드리프트 기법들

쵸핑(chopping)1-7

첫 번째 제로 드리프트 기법으로서 쵸핑을 들 수 있는데, 이는 오차를 보다 높은 주파수로 변조함으로써 오프셋과 저주파 잡음을 신호와 분리하는 것이다.

그림 1은 쵸핑이 입력 신호(파란색 파형)를 구형파로 변조하고, 이 신호를 증폭기로 처리한 다음(b), 출력단에서 다시 DC로 복조하는 방법(c)을 보여준다. 이와 동시에 증폭기의 저주파 오차(빨간색 파형)는 출력단에서 구형파로 변조되며(c), 그런 다음에 저역통과 필터(LPF)를 사용해 필터링된다(d).

마찬가지로 주파수 도메인에서도 입력 신호(그림 2에서 파란색 신호)를 쵸핑 주파수로 변조하고, fCHOP에서 이득 스테이지로 처리하고(b), 출력단에서 다시 DC로 복조한 다음(c), 마지막으로 LPF를 사용해서 필터링한다(d). 이 증폭기의 오프셋과 잡음 소스(그림 2에서 빨간색 신호)는 이득 스테이지를 통해서 DC로 처리되고, 출력 쵸핑 스위치를 사용해서 fCHOP으로 변조되며(c), LPF를 사용해서 필터링된다(d). 구형파 변조를 사용하기 때문에 변조 주파수의 홀수 배수 부근에서 변조가 일어난다.

주파수 도메인과 시간 도메인 그림에서 볼 수 있듯이, LPF가 현실적으로 이상적일 수 없으므로 변조 잡음과 오프셋으로 인한 약간의 잔류 오차가 있을 수 있다.

오토 제로(auto-zero)1-3, 5-7

두 번째 제로 드리프트 기법으로서, 오토 제로는 증폭기에서 저주파 오차 소스를 샘플링하고 차감하는 식으로 작동하는 동적 교정 기법이다.

그림 3은 기본적인 오토 제로 증폭기를 보여준다. 이는 오프셋과 잡음을 포함하는 증폭기, 입력과 출력을 재구성하기 위한 스위치, 오토 제로 샘플링 커패시터로 구성된다.

오토 제로 구간인 φ1에는 회로 입력이 공통 전압으로 단락되고 오토 제로 커패시터가 입력 오프셋 전압과 잡음을 샘플링한다. 이 구간에서는 증폭기가 신호 증폭을 하지 못한다. 오토 제로 증폭기가 연속적으로 동작하기 위해서는 2개의 동일한 채널을 인터리브해야 한다. 이것을 ‘핑퐁 오토 제로’라고 한다.

증폭 구간인 φ2에는 입력이 다시 신호 경로로 연결되고 증폭기가 신호를 증폭할 수 있다. 오토 제로에 의해서 저주파 잡음, 오프셋, 드리프트가 제거되며, 잔류 오차는 전류 값과 이전 오차 샘플 사이의 차이다. 저주파 오차 소스들은 φ1에서 φ2가 되면서 그리 많이 달라지지 않으므로 이 같은 차감 방식이 효과적으로 작동한다. 반면에 고주파 잡음은 베이스밴드로 에일리어싱되며, 그 결과 백색 잡음 플로어는 증가한다(그림 4).

잡음 폴딩이 있고 연속 동작을 위해 추가적인 채널을 필요로 한다는 점에서, 독립형 연산 증폭기에는 쵸핑이 좀더 전력 효율적인 제로 드리프트 기법일 수 있다.

쵸핑 아티팩트1-3, 5-7

쵸핑은 원치 않는 오프셋, 드리프트, 1/f 잡음을 제거하는 데에는 효과적이지만, 출력 리플이나 글리치 같은 원치 않는 AC 아티팩트를 만든다. 아나로그디바이스(Analog Devices)의 최신 제로 드리프트 제품들은 이러한 아티팩트의 크기를 줄이고 보다 높은 주파수대로 위치시키는 조치들을 도입함으로써 시스템 차원에서 필터링을 수월하게 한다.

리플 아티팩트

리플은 저주파 오차들을 쵸핑 주파수의 홀수 고조파로 이동시키는 쵸핑 변조 기법에서 기본적으로 수반되는 결과이다. 증폭기 설계 엔지니어는 다음과 같은 방법들을 사용해서 리플의 영향을 줄일 수 있다.

• 생산 시에 오프셋 트리밍: 일회성으로 일차적인 트리밍을 실시함으로써 공칭 오프셋을 크게 낮출 수 있다. 하지만 오프셋 드리프트와 1/f 잡음은 남는다.

• 쵸핑과 오토 제로 결합: 증폭기에 먼저 오토 제로를 실시하고 그 다음에 쵸핑을 실시해서 높아진 잡음 스펙트럼 밀도(NSD)를 더 높은 주파수대로 상향변조한다. 그림 4는 쵸핑과 오토 제로를 거친 후의 잡음 스펙트럼 결과를 보여준다.

• 자동교정 피드백(ACFB): 로컬 피드백 루프를 사용해서 출력단에서 변조된 리플을 검출하고 소스단에서 저주파 오차를 제거할 수 있다.

글리치 아티팩트

글리치는 쵸핑 스위치들에 의해 야기되는 전하 주입 불일치로 인해서 발생하는 순간적 스파이크이다. 이러한 글리치의 크기는 소스 임피던스와 전하 불일치 양 같은 여러 요인에 따라서 좌우된다.1

글리치 스파이크는 쵸핑 주파수의 짝수 고조파에 아티팩트를 일으킬 뿐만 아니라 잔류 DC 오프셋을 발생하는데, 이는 쵸핑 주파수에 비례한다. 그림 5의 왼쪽은 그림 1의 V1(쵸핑 스위치 안)과 V2(출력 쵸핑 스위치를 지난 후)에서 이러한 스파이크가 어떤 모습인지 보여준다. 그림 5의 오른쪽에서는 유한한 증폭기 대역폭으로 인해서 쵸핑 주파수의 짝수 고조파에 추가적인 글리치 아티팩트가 발생한다는 것을 알 수 있다.

리플과 마찬가지로, 증폭기 설계 엔지니어들은 다음과 같은 방법을 사용해서 제로 드리프트 증폭기에서 글리치의 영향을 낮출 수 있다:

• 전하 주입 트리밍: 쵸핑 증폭기의 입력에 주입되는 전하를 조절해서 전하 불일치를 보정할 수 있는데, 이는 연산 증폭기 입력단에서 입력 전류의 양을 줄여준다.

• 다중채널 쵸핑: 이 방법은 글리치의 크기를 줄일 뿐 아니라 글리치를 더 높은 주파수대로 이동시킴으로써 필터링을 수월하게 한다. 이 방법은 단순히 쵸핑을 더 높은 주파수에서 실시하는 것에 비해 글리치를 좀더 빈번하게 하면서 크기도 더욱 줄인다. 그림 6은 통상적인 제로 드리프트 증폭기와 ADA4522를 비교한 것으로, 이 기법을 사용해서 어떻게 글리치의 영향을 크게 낮출 수 있는지 보여준다.

그림 7에서는 쵸핑 증폭기 출력 전압에 다음과 같은 아티팩트가 발생한다는 것을 알 수 있다:

• 상향변조 오프셋으로 인한 리플과 쵸핑 주파수의 홀수 배수에서 나타나는 1/f

• 쵸핑 스위치들의 전하 주입 불일치로 인한 글리치와 유한한 증폭기 대역폭으로 인해 쵸핑 주파수의 짝수 배수에 나타나는 글리치

시스템 차원의 설계 고려사항

데이터 수집 시스템에 제로 드리프트 증폭기를 사용할 때는 어느 위치에서 주파수 아티팩트가 발생하는지 이해하고 그에 따라서 적절히 설계할 필요가 있다.

데이터 시트에서 쵸핑 주파수 구하기

통상적으로 쵸핑 주파수는 데이터 시트에 명시적으로 표기 되는데, 잡음 스펙트럼 플롯으로부터 구할 수도 있다. ADI의 몇몇 최신 제로 드리프트 증폭기 제품의 데이터 시트에서는 스펙트럼 상의 어느 지점에서 아티팩트가 발생하는지 명확히 표기하고 있다.

ADA4528 데이터 시트에서는 “애플리케이션 정보(Application Information)” 부분에서 쵸핑 주파수를 200kHz로 표기하고 있을 뿐만 아니라, 그림 8의 잡음 밀도 플롯에서도 이것을 알 수 있다.

ADA4522 데이터 시트의 “작동 원리(Theory of Operation)” 부분에서는 오프셋 및 리플 교정 루프를 800kHz로 실행할 때의 쵸핑 주파수를 4.8MHz로 표기하고 있다. 그림 9는 ADA4522의 잡음 밀도를 보여주는데, 어느 위치에서 잡음 피크들이 발생하는지 알 수 있다. 6MHz에서도 잡음 범프가 발생하는 것을 볼 수 있는데, 이는 단위 이득일 때 이 루프의 위상 마진 감소로 인한 것으로서 제로 드리프트 증폭기에서만 일어나는 것이 아니다.

한 가지 유의할 점은, 데이터 시트에 표기되어 있는 주파수는 정격 수치로서, 부품마다 약간의 차이가 있을 수 있다는 것이다. 그러므로 만약에 자신의 시스템에 차동 신호 컨디셔닝을 위해서 2개의 쵸핑 증폭기가 필요한 경우에는 듀얼 증폭기를 사용하는 것이 좋다. 2개의 단일 증폭기를 사용하면 쵸핑 주파수가 약간 다르기 때문에 두 주파수가 상호작용하고 추가적인 IMD를 발생시킨다.

입력 소스 임피던스 매칭

순간 전류로 인한 글리치가 입력 소스 임피던스와 상호작용해서 차동 전압 오차를 일으킬 수 있는데, 이는 잠재적으로 쵸핑 주파수의 배수에 추가적인 아티팩트를 일으킬 수 있다. 그림 10에서는 ADA4522의 잡음 밀도 플롯에서 소스 저항 불일치로 인한 스파이크가 발생하는 것을 볼 수 있다(아래). 이 잠재적 오차 요인을 완화하기 위해서는 쵸핑 증폭기의 양쪽 입력에 보여지는 임피던스를 동일하게 해야 한다(위).

IMD와 에일리어싱 아티팩트

쵸핑 증폭기를 사용할 때 입력 신호가 쵸핑 주파수 fCHOP과 믹스되어서 fIN ± fCHOP, fIN ± 2fCHOP, 2fIN ± fCHOP…에서 IMD를 발생시킬 수 있다. 특히 fIN이 쵸핑 주파수에 근접할수록 이러한 IMD 성분들이 관심 대역으로 유입될 수 있다. 이러한 문제를 피하기 위해서는 쵸핑 주파수가 입력 신호 대역폭보다 훨씬 높은 제로 드리프트 증폭기를 선택하고 증폭기 스테이지에 앞서서 fCHOP에 가까운 주파수들에서 간섭 요인들을 필터링하도록 한다.

또한 증폭기 출력을 ADC를 사용해서 샘플링 할 때 쵸핑 아티팩트가 에일리어싱 될 수 있다. 그림 11은 ADC가 샘플을 취할 때 글리치 주파수 에일리어싱으로 인한 IMD 성분들을 보여준다. 이러한 IMD 성분은 글리치와 리플 크기에 따라 좌우되며 부품마다 약간씩 차이가 있을 수 있다. 그러므로 신호 체인을 설계할 때 이러한 IMD를 줄이기 위해서는 ADC 전위에 에일리어싱 방지 필터를 포함할 필요가 있다.

쵸핑 아티팩트 필터링

시스템 차원에서 이러한 고주파 아티팩트를 처리할 수 있는 가장 효과적인 방법은 필터링을 하는 것이다. 제로 드리프트 증폭기와 ADC 사이에 LPF를 사용해서 쵸핑 아티팩트를 줄이고 에일리어싱을 방지할 수 있다. 이러한 이유로, 쵸핑 주파수가 높은 증폭기는 LPF의 요구조건을 완화하고 더 넓은 신호 대역폭을 가능하게 한다.

이러한 예로서 그림 13은 ADA4522로 그림 12의 기법들을 사용해서 쵸핑 아티팩트를 완화했을 때의 효과를 보여준다. 기법들은 폐쇄 루프 이득을 높이고, 후위 필터링을 하고, 피드백 저항과 병렬로 커패시터를 사용하는 것이다.8

시스템에서 얼마나 많은 대역외 제거가 필요한가에 따라서 더 높은 차수의 능동 필터가 필요할 수 있다. ADI는 필터 설계를 돕기 위해서 다중 피드백 필터 튜토리얼과 온라인 필터 설계 툴 같은 자원을 제공한다.

쵸핑 아티팩트가 어디에서 발생할지를 이해함으로써 필요한 필터를 설계할 수 있다. 표 1은 제로 드리프트 증폭기로 인해서 어느 위치에서 AC 아티팩트가 발생할지를 보여준다.

맺음말

제로 드리프트 증폭기에서 고주파 아티팩트를 이해함으로써 넓은 대역폭으로 동작하는 애플리케이션에서도 제로드리프트 연산 증폭기를 좀더 확신을 가지고 사용할 수 있다. 그러기 위해서는 다음과 같은 점들을 고려해서 시스템을 설계해야 한다:

• 제로 드리프트 증폭기의 양쪽 입력에 보여지는 소스입력 임피던스 매칭

• 차동 신호 컨디셔닝을 위해서 듀얼 증폭기 사용

• 데이터 시트에서 잡음 스펙트럼을 확인해서 아티팩트의 주파수 위치 이해

• 동적 오프셋 감소 기법에 수반되는 고주파 아티팩트의 영향을 줄이도록 필터 설계

• 주파수 도메인에서 고주파 아티팩트를 이해하고 그에 따라서 계획

참고 문헌

1. Yoshinori Kusuda. “Reducing Switching Artifacts in Chopper Amplifiers.” Delft University of Technology, the Netherlands, May 2018.

2. Christian Enz and Gabor C. Temes. “Circuit Techniques for Reducing the Effects of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization.” Proceedings of the IEEE, Vol. 84, No. 11, November 1996.

3. Boris Murmann. EE315A: VLSI Signal Conditioning Circuits: Chaper 7, Precision Analog Circuit Techniques. Stanford University, 2014.

4. James Bryant. “Multipliers vs. Modulators.” Analog Dialogue, Vol. 47, June 2013.

5. A. T. K. Tang. “A 3/spl mu/V Offset Operational Amplifier with 20nV//spl radic/Hz Input Noise PSD at DC Employing Both Chopping and Autozeroing.” IEEE, February 2002.

6. Michiel Pertijs and Wilko J. Kindt. “A 140 dB-CMRR Current-Feedback Instrumentation Amplifier Employing Ping-Pong Auto-Zeroing and Chopping.” IEEE Journal of Solid-State Circuits, Vol. 45, No. 10, October 2010.

7. Johan F. Witte, Kofi A. A. Makinwa, and Johan H. Huijsing. “A CMOS Chopper Offset-Stabilized Opamp.” IEEE Journal of Solid-State Circuits, Vol. 42, No. 7, July 2007.

8. Yoshinori Kusuda and Vicky Wong. “Zero-Drift Amplifiers: Now Easy to Use in High Precision Circuits.” Analog Dialogue, Vol. 49, July 2015.

ADA4523 data sheet. Analog Devices, Inc., April 2020.

AD7768-1 data sheet. Analog Devices, Inc., May 2019.

Kusuda, Yoshinori. “Analysis of Input Current Noise with Even Harmonics Folding Effect in a Chopper Op Amp.”

Analog Dialogue, Vol. 53, May 2019.

저자 소개

사이먼 바실리코(Simon Basilico)는 아나로그디바이스(Analog Devices) 정밀 신호 체인 그룹의 설계 엔지니어이다(캘리포니아주 산타클라라). 통합 혼합신호 설계와 시스템-인-패키지(SiP) 솔루션을 비롯해서 정밀 신호 체인을 주로 맡고 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

본 기사의 전문은 PDF문서로 제공합니다.

(로그인필요)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

100자평 쓰기

.jpg)