반도체공정과 정합성을 고려한 설계방법론에 대하여

시스템 반도체인 파운드리(Foundry)의 공정기술은 매년 발전하고 있다. 8n, 5n, 3n 등 공정 미세화와 더불어 Fin-fet, GAA 등 새로운 공정 개발이 진행되고 있다. 공정 미세화와 공정 개발에 따른 집적도가 향상되었지만 그에 반해 설계의 어려움 또한 발생하고 있다. 이는 미세화되고 집적화되는 공정 개발로 인해 공정 영향성 또한 증가하기 때문이다. 공정 영향성으로 인해 파운드리에서 설계에 제공하는 ‘spice model’과 ‘silicon data’ 간의 정합성이 문제가 되고 있기 때문이다. 반도체회사에서 설계업무를 하는 저자는 공정 효과로 인한 spice model과 silicon data 간의 정합성을 고려한 설계 방법론에 대해 이야기해보고자 한다.

.jpg) 글/고려대학교 주병권 교수님 연구실

글/고려대학교 주병권 교수님 연구실

주병권 (고려대학교 전기전자공학부 교수)

김용범 (고려대학교 전기전자컴퓨터공학부 석사과정)

목 차

1. 반도체 공정의 개요

1-1 반도체 개념설명

1-2 반도체 공정의 변화과정

1-3 현재 진행중인 반도체 공정

2. 공정effect과 정합성을 고려한 설계방법

3. 향후 반도체 산업의 전망

4. 결론

5. 참고 문헌

4차 산업혁명이 도래하고 있다. IT, 인공지능 분야에 대한 연구와 발전이 이루어지고 있다. 그와 더불어 IT, 인공지능의 핵심 부품 소자인 반도체에 대한 연구와 발전도 이루어지고 있다.

반도체는 기억장치의 핵심을 담당하는 메모리 반도체, 전자제품 동작의 머리, 눈, 힘을 담당하는 시스템 반도체로 나눌 수 있다. 한국은 글로벌 반도체의 핵심 국가이며, 삼성과 하이닉스 등의 글로벌 반도체 기업들이 포진해 있다. 이로 인해 어쩌면 21세기는 한국의 위상을 세계에 더욱더 떨칠 수 있는 기회가 될 수 있을 것이다.

시스템 반도체인 파운드리(Foundry)의 공정기술은 매년 발전하고 있다. 8n, 5n, 3n 등 공정 미세화와 더불어 Fin-fet, GAA 등 새로운 공정 개발이 진행되고 있다. 공정 미세화와 공정 개발에 따른 집적도가 향상되었지만 그에 반해 설계의 어려움 또한 발생하고 있다. 이는 미세화되고 집적화되는 공정 개발로 인해 공정 영향성 또한 증가하기 때문이다. 공정 영향성으로 인해 파운드리에서 설계에 제공하는 ‘spice model’과 ‘silicon data’ 간의 정합성이 문제가 되고 있기 때문이다.

반도체회사에서 설계 업무를 하는 저자는 공정 효과로 인한 spice model과 silicon data 간의 정합성을 고려한 설계 방법론에 대해 이야기해보고자 한다.

1. 반도체 공정의 개요

1-1 반도체 개념 설명

반도체는 도체와 부도체 사이의 물성을 가진 소자이다. 영어로는 ‘Semiconductor’라 한다.

반도체는 특정 조건하에만 전기가 통하는 물질이 되며, 전류를 조절하는 목적으로 사용된다. 전류를 조절하는 것은 전압이나 열 등으로 전류를 조절할 수 있으며, 기본적으로 웨이퍼에 패턴을 형성하여 패키지 이후에 전자제품 부품으로 사용한다.

반도체 물질로는 주로 실리콘(Si)을 사용하며, 불순물을 첨가하여 특성에 맞게 만들어지게 된다. 대표적인 반도체 소자는 다이오드, 트랜지스터 등이 있다.

위에도 언급했듯이 불순물 첨가와 패턴 등을 웨이퍼에 만들기 위해서는 대표적인 반도체 8대 공정을 거쳐야만 한다.

네이버, 구글 등에서 반도체 8대 공정을 검색하면 웨이퍼 제조부터 EDS 테스트 등의 제조 순서를 구현했을 뿐 실제 Foundry Line에서 제작하는 8대 공정은 Photo, Etch, Implant, Diffusion, CMP(Chemical Mechanical Polishing), CVD(Chemical vapor deposition), Metal, Clean로 반도체 공정이 이루어진다.

각 공정은 한번만 이루어지는 것이 아니라 생성되는 레이어의 패턴을 생성위해 수차례 반복된다. 공정 순서는 개의치 않아도 된다.

반도체의 트랜지스터 공정으로는 크게 Planar, SOI(Silicon On Insulator), Fin-fet, GAA(Gate All Around)로 나눌 수 있으며, 공정이 미세화 됨에 따라 Fin-fet과 GAA로 진행되고 있는 상황이다.

반도체 제작을 위해서는 그전에 회로 설계와 레이아웃 설계가 먼저 진행되어야 한다. 회로설계에는 크게 아날로그 와 디지털 설계로 나누어지며, 레이아웃 또한 회로 설계와 같이 나눌 수 있다.

1-2 반도체 공정의 변화과정

예전 대형 브라운관 TV나 2G Phone, 그 외 전자제품에 쓰이던 반도체들은 2D 공정으로 진행되어 왔다. 대표적으로 Planar 공정으로 반도체 제작을 진행했으며 사용하던 공정 또한 350나노, 180나노 등으로 제작돼 왔다.

21세기 초부터 스마트폰 보급과 브라운관 TV의 쇠퇴, IoT 등 산업 발전으로 인한 반도체 미세화가 추진되었다. 이에 기존 Planar 공정을 탈피하고 3D Fin-fet 공정을 적용하여 스마트폰 및 각종 IT 기계에 탑재되고 있다.

이후 더 소형화되고 각종 기능이 탑재된 전자제품이 개발되고 있어 반도체 또한 더욱 미세공정화에 주력하게 될 것이다.

최근 진행되고 있는 공정기술로는 GAA(Gate All Around) 공정을 삼성에서 진행하고 있다. 향후에도 공정 미세화를 위한 파운드리 업체의 개발 노력을 계속될 것으로 보인다.

1-3 현재 진행중인 반도체 공정

진행 중인 반도체 공정으로는 Planar, SOI, Fin-fet, GAA가 진행되고 있다.

Planar 공정은 트랜지스터의 전류의 흐름을 단면으로만 가져갔다. 즉,

그림 1과 같이 전류가 흐르는 전류의 길(Channel)이 형성되었으며 이는 미세화되지 않은 공정에서 사용되어 왔으며 현재도 디스플레이 칩과 파워 칩 등에서 주로 사용되고 있는 반도체 공법이다.

.png)

그림 1. Planar MOSFET 구조[1]

주로 DDI(Display Driver IC)와 PMIC(Power Management IC)의 제품군에서 쓰이며 이는 TV 패널, 스마트폰 패널, 스마트폰 내 파워 칩 등으로 사용된다.

각종 전자제품들의 성능이 향상되고 소형화됨에 따라 전자제품의 소재인 반도체 또한 미세공정화가 되어야 한다. 이에 반도체 공정도 기존 Planar 공정에서의 한계가 발생하였으며, 이에 대응하고자 Fin-fet 공정을 도입하게 된다.

Fin-fet 공정의 ‘Fin’은 ‘상어의 지느러미’를 뜻하며, 기존 2D 구조의 반도체의 한계를 한단계 극복하여 칩을 좀더 집적화할 수 있게 되었다.

Fin-fet은 Planar와 다르게 3D 구조를 가지는 반도체 구조로서 전류의 흐름이 되는 길인 전류의 길 형성을

그림 2와 같이 가지게 된다. 이는 Planar 공정 대비 더 많은 긍정적인 특성을 가질 수 있으며 Planar 대비 집적화되어 좀더 미세화된 패턴에서 더 좋은 성능을 낼 수 있는 것이다.

그림 2. Fin-Fet 구조[2]

주로 SoC(System on Chip), 센서(Sensor) 등의 제품군에서 사용되며 이는 스마트폰의 AP, 카메라 센서 등에 사용된다. 그 외 각종 빛을 감지하는 센서나 각종 연산이 필요한 전자제품 등에 사용된다.

GAA 공정은 채널(Channel)의 형성을 3면으로 형성하는 Fin-fet 대비 4면으로 형성하여 Fin-fet 보다 특성적인 측면에서 우위에 있다, 이는 Fin-fet과 같은 3D 공정기법이지만 Fin-fet 보다 같은 사이즈 내에서 더 좋은 성능을 낼 수 있다. 다만 ‘off current’ 등의 공정 특성적인 측면이 아직 보완되지 않아 양산을 위한 수율을 끌어올리는데 노력하고 있다. GAA 공정기법은

그림 3과 같다.

.png)

그림 3. GAA-Fet 구조[3]

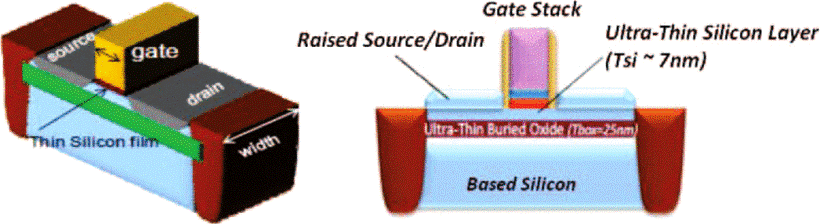

SOI 공정은 웨이퍼에 절연막이 처지게 된다. 이는 CMOS 구조의 취약점인 Latch-up, leakage event 등에서 다른 공정에 비해 우위의 특성을 가지게 되며, 좀 더 조밀한 구조를 가질 수 있다. 그리고 절연 막으로 인한 트랜지스터의 기판 바이어스 효과를 조절하여 트랜지스터의 특성 조절이 가능하다. 단점으로는 일반 웨이퍼에 비해 가격이 비싸서 조밀한 구조 대비 가성비 여부는 제품에 따라 다르다. SOI의 공정기법은

그림 4와 같다.

그림 4. SOI MOSFET구조[4]

2. 공정 effect 과 정합성을 고려한 설계방법

반도체 공정에 주로 사용되는 소자는 다이오드와 트랜지스터이다. 주로 사용되는 트랜지스터를 CMOS(Complementary Metal Oxide Semiconductor)라 하며 이 CMOS를 웨이퍼 위에 구현함으로써 집적회로를 만들 수 있는 것이다.

그림 1은 CMOS(P/NMOS)의 단면 구조이다. 위와 같이 CMOS는 PN 구조로 구성되어 있다. PMOS는 N type 위에 만들어지며 Source와 Drain은 P type의 구조를 가지게 된다. NMOS는 이와 반대의 구조를 가지게 된다.

이렇게 PN 구조의 CMOS를 웨이퍼 위에 구현하고 점점 집적화됨에 따라 의도치 않은 공정 영향성들이 발생하게 된다. 이런 영향성들로 트랜지스터의 특성 변화로 인한 spice와 silicon data 간의 정합성이 문제가 발생하게 된다.

대표적으로 STI EFFECT, WPE, BODY EFFECT, SHORT CHANNEL EFFECT, LATCH-UP 등의 공정 영향성들이 있으며 이외에 수많은 공정 영향성이 발생한다. 저자는 그중 STI EFFECT, WPE, BODY EFFECT 3가지 공정 영향성에 대해 기술하겠다.

-STI EFFECT

STI EFFECT은 Shallow Trench Isolation의 약자로 실제로 패턴이 생성되어 전류가 흐를 수 있는 Silicon 영역을 만들 때 발생하는 공정 영향성이다.

STI 진행시 트랜지스터별로 Si 구분을 위해 웨이퍼 위 전면에 도포된 Si를 깎아내는 Etch 공정을 진행하게 된다. 이후 깎아낸 공간을 산화시켜 채우게 되는데 이때 깎아낸 트랜지스터 Si의 양 끝에 압착 현상이 발생하게 되어 Si 격자구조에 변형을 주게 된다. 이로 인해 트랜지스터의 특성이 변하게 되어 칩의 특성 변화를 일으킬 수 있다.

PMOS의 경우 STI 영향성으로 인한 spice data 보다 silicon data의 전류가 증가하게 되며, NMOS의 경우 반대로 전류가 감소하게 된다,

그림 5. STI effect [5]

그림 6. STI effect에 따른 전류 변화[6]

STI 영향성으로 인한 spice data와 silicon data 간의 차이가 발생하면서 설계 진행 시 영향성을 고려한 설계를 진행하게 된다. 회로에서 대부분의 트랜지스터들은 포화 상태로 동작되게 되어있어 크게 문제가 되지 않지만 차동 증폭기의 입력과 같은 매칭 트랜지스터들은 두 입력 간의 비교를 위해 해당 STI에 대한 영향성을 가지게 된다. 이를 극복하기 위한 트랜지스터 양 끝에 Silicon 영역을 확장하거나 더미 트랜지스터를 배치하여 해당 효과에 대한 영향성을 없애고 있다.

-WPE

WPE는 Well Proximity Effect의 약어로 반도체 8대 공정 중 Implant 공정에서 Well Implant 진행 시 웰 양끝 쪽으로 이온 들이 몰리게 되고 그 위에 트랜지스터가 형성되었을 때 트랜지스터의 문턱전압에 변화를 주게 된다. 아래 트랜지스터 전류 공식을 참조했을 때 문턱전압의 변화가 전류의 변화에 영향을 줄 수 있다는 것을 볼 수 있다. (μ

_n, μ

_p: 이동도, C

_ox: 유전율)

그림 7. WPE에 따른 문턱전압의 변화[7]

웰 양끝으로 몰린 P/N 특성의 이온 위로 트랜지스터가 올라오게 되면 문턱전압 증가로 인한 Id(드레인 전류)가 감소하게 되어 회로 특성에 영향을 끼치게 된다.

그림 8. WPE 설명[8]

이 같은 영향성을 극복하고자 설계진행 시 웰 양끝과 트랜지스터 간의 이격을 진행하고 있다.

집적화와는 상반되는 이격을 진행하고 있지만 WPE가 트랜지스터에 미치는 영향이 상당하기에 어쩔 수없이 이격을 진행하게 된다. 특히 고전압을 사용하는 트랜지스터의 경우 웰에 불순물을 첨가하여 고전압 웰을 만들고 있어 더 큰 영향성을 가지게 되므로 현재까지 이격 외에는 마땅한 설계 방법이 없는 상황이다.

-기판 바이어스 효과(BODY EFFECT)

기판 바이어스 효과란 WPE와 같이 문턱 전압의 변화로 인한 트랜지스터의 전류 변화를 유도하게 된다. 이는 오직 공정 특성으로만 발생하는 영향성은 아니며 회로 설계로 인한 공정 특성 변화가 트랜지스터의 전류 변화를 가져오게 된다.

CMOS는 4단자로 구성되어 있다. Gate, Source, Drain, Bulk로 구성되어 있으며 각 단자별로 연결이 되어 전기적인 특성을 가진 트랜지스터로서의 동작을 수행하게 된다.

그림 1를 보면 좌측이 NMOS 우측이 PMOS이다.

P-type substrate는 NMOS의 Bulk이며, N-WELL 은 PMOS의 Bulk이다.

다이오드의 특성을 보면 P/N 구조로 되어 있으며 P 쪽에 높은 전압이 걸리게 되면 다이오드는 도통하게 되며 P/N 사이의 공핍층은 얇아지게 된다. 반대로 N 쪽에 더 높은 전압을 걸게 되면 P/N 사이의 공핍층은 두꺼워지게 된다. 이같이 다이오드의 특성을 확인했을 때 P/N 구조로 되어있는 CMOS 또한 같은 영향성을 받게 된다.

그림 9을 보면 Source(N type) 와 Bulk(P type) 간의 전위차로 인한 공핍층의 증가와 감소를 확인할 수 있다. 이를 감안한 회로 설계는 긍정적인 공정 영향성을 볼 수 있지만, 이를 간과한 회로설계는 의도치 않은 공정 영향성으로 인한 특성 변화를 겪게 될 것이다. 기판 바이어스 효과는 RBB와 FBB로 공정 특성 변화가 일어나게 된다.

FBB: Forward Body Bias

-Body 전압이 Source 전압보다 높아지면서 공핍층의 두께를 감소시켜 문턱전압을 낮춰 전류량을 증가시킨다.

RBB: Reverse Body Bias

-Body 전압이 Source 전압보다 낮아지면서 공핍층의 두께를 증가시켜 문턱전압을 높여 전류 량을 감소시킨다.

그림 9. (a), (b) 기판 바이어스 효과에 따른 문턱전압의 변화[9]

(a) MOSFET 구조 (b) Bulk-Source 간의 전압차에 따른 문턱전압 변화

3. 향후 반도체 산업의 전망

4차 산업혁명에 도래한 반도체 산업은 앞으로 더 큰 호황을 맞을 것이다. 삼성전자와 SK하이닉스 그리고 대만의 TSMC 등의 기업에서 반도체 장비 투자에 수십 조 원을 투자하겠다는 계획을 보면 알 수 있듯이, 앞으로의 삶에서 반도체의 필요성은 더 커질 것이다.

다만 지금껏 메모리 반도체 위주의 성장되었다면, 이후로는 시스템 반도체가 더욱 각광받을 것이다. 단순 기억장치가 아닌 이제는 생각을 하고 판단하고, 현재 눈으로 보는 현실을 가상현실로 구현하는 세상이 도래할 것이기 때문에 시스템 반도체의 중요성을 더 커질 것이다.

그림 10. 앞으로의 반도체 성장전망[10]

곧 다가올 미래에서는 영화 “Back to the future”와 같이 하늘을 나는 자동차. 인간의 개입 없이 운전하는 자율주행 자동차. 별도의 장비 없이 언제 어느 곳에서나 가상의 디스플레이를 구현하여 영상통화, 회의, 정보검색을 할 수 있을 것이다.

이 모든 것이 실현되기 위해서는 시스템 반도체의 발전은 필수 불가결이라 저자는 생각한다.

4. 결론

이번 기술 보고서의 결론을 도출해 보면, 반도체는 작고 미세하지만 점점 더 우리 삶의 영역에 자리잡을 것이며 우리 삶의 질을 훨씬 더 높여 줄 수 있는 것이라고 생각한다.

반도체 회사에 근무하는 저자는 이번 기술 보고서 제작을 통해 간과하고 있었던 반도체 공정의 특성들과 변화되어 가는 공정들에 대해 다시금 정리할 수 있는 좋은 기회였던 것 같다.

메모리 반도체, 시스템 반도체 모두 미래 4차 산업혁명을 이끌어갈 주역이 될 것이므로 저자와 같이 전기 전자공학을 전공하는 사람들에 대해 이 기술 보고서를 참고하여 반도체 산업에 대한 미래에 대한 확신과 반도체 공정에 대한 관심, 그리고 더 나아가 본인의 향후 진로에 대한 계획을 세우는 데 도움이 되었으면 하는 바람이 있다.

5. 참고 문헌

[1] Razavi, Behzad. Microelectronics. John Wiley & Sons, Inc., 2015.

[2] He, Frank, et al. "FinFET: From compact modeling to circuit performance." 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC). IEEE, 2010.

[3] Yakimets, Dmitry, et al. "Vertical GAAFETs for the ultimate CMOS scaling." IEEE Transactions on Electron Devices 62.5 (2015): 1433-1439.

[4] Pelloux-Prayer, Bertrand, et al. "Planar fully depleted SOI technology: The convergence of high performance and low power towards multimedia mobile applications." 2012 IEEE Faible Tension Faible Consommation. IEEE, 2012.

[5] Gallon, C., et al. "Electrical analysis of mechanical stress induced by shallow trench isolation [MOSFETs]." ESSDERC'03. 33rd Conference on European Solid-State Device Research, 2003.. IEEE, 2003.

[6] Gallon, C., et al. "Electrical analysis of mechanical stress induced by shallow trench isolation [MOSFETs]." ESSDERC'03. 33rd Conference on European Solid-State Device Research, 2003.. IEEE, 2003.

[7] Drennan, Patrick G., M. L. Kniffin, and D. R. Locascio. "Implications of proximity effects for analog design." IEEE Custom Integrated Circuits Conference 2006. IEEE, 2006.

[8] Drennan, Patrick G., M. L. Kniffin, and D. R. Locascio. "Implications of proximity effects for analog design." IEEE Custom Integrated Circuits Conference 2006. IEEE, 2006.

[9] Maeda, Shigenobu, et al. "Substrate-bias Effect and Source-drain Breakdown Characteristics in Body-tied Short-channel SOI MOSFET's." IEEE Transactions on Electron Devices 46.1 (1999): 151-158.

[10] 전자부품 전문 미디어 디일렉(http://www.thelec.kr) 김규식, 전경운 기자 기사(2024.01.30)

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)

.png)

.png)

.png)

.png)

.png)

.JPG)

.png)

.png)

(0).png)

(0).png)