글|브래드 브래넌(Brad Brannon), 아나로그디바이스

제로 IF(ZIF) 아키텍처는 무선 기술이 발명된 이래 꾸준히 사용되어 왔다. 오늘날 ZIF 아키텍처는 텔레비전, 휴대전화, 블루투스® 기술 등 거의 모든 소비자용 무선제품에 사용된다. ZIF가 이렇게 널리 사용되는 주된 이유는 이 아키텍처가 무선기술 중에서 최저 비용, 최저 전력 소비, 최소 풋프린트의 솔루션을 제공하기 때문이다.

ZIF 아키텍처는 지금까지 고성능을 요구하는 애플리케이션에는 사용되지 않았다. 하지만 무선 기술의 수요 및 스펙트럼 사용이 급격히 증가함에 따라, 이런 필요성을 충족하는 인프라에서 경제적으로 무선 성능을 구현하기 위한 변화가 필요하게 됐다. 현대의 ZIF 아키텍처는 해당 아키텍처에 일반적으로 수반되는 여러 결함들을 공정, 설계, 파티셔닝, 알고리즘의 조합을 통해 해결해 왔기 때문에 이러한 필요성을 충족할 수 있다.

ZIF 기술의 진보는 현존하는 고성능 무선 아키텍처에 도전장을 내밀고 있으며, 과거 ZIF 기술로는 불가능했던 새로운 애플리케이션을 구현하는 혁신적인 성능의 신제품들을 출시하고 있다. 이 글에서는 ZIF 아키텍처의 다양한 혜택과 이를 통해 무선 설계방식에서 구현할 수 있는 뛰어난 성능을 소개한다.

무선 엔지니어의 도전 과제[1]

오늘날의 트랜시버 설계자는 무선 장치와 애플리케이션에 대한 필요성이 증가함에 따라 더욱 많은 요구에 직면하고 있으며, 이는 곧 더 넓은 대역폭에 대한 수요와 직결된다. 설계자들이 사용하는 무선 방식은 지난 수년간에 걸쳐 단일반송파에서 다중반송파로 변화해왔다.

하나의 대역 내에 있는 스펙트럼이 모두 사용되면 새로운 대역이 할당됨에 따라 지금은 40개 이상의 무선대역이 사용되고 있다. 대역 운영자들은 여러 대역에 걸쳐 스펙트럼을 보유하고 있고 이러한 자원은 조직화돼야 하기에, 현재의 무선 추세는 반송파 묶음(carrier aggregation)을 향하고 있다. 이는 더 나아가 다대역 무선 방식으로 이어진다. 이러한 추세는 보다 높은 성능을 가진 무선 부품을 요구하고 있으며, 이는 보다 뛰어난 대역 외 신호제거, 향상된 송출 및 전력 소비 성능에 대한 필요성과 직결된다.

무선에 대한 수요가 빠르게 증가하는 반면, 전력과 공간의 범위는 제한적이다. 전력과 공간 사용을 모두 최적화하고자 하는 수요가 끊임없이 증가하면서, 카본 풋프린트 및 물리적 풋프린트를 줄이는 일이 중요해지고 있다. 이러한 목표를 달성하기 위해서는 무선 아키텍처와 파티셔닝을 바라보는 새로운 관점이 필요하다.

통합

특정 설계에서 무선 부품의 수를 늘리기 위해서는 각 무선 부품의 풋프린트를 소형화해야 한다. 이를 해결하기 위해 사용되던 방법은 해당 설계를 하나의 실리콘 판에 계속해서 통합시키는 것이다. 디지털적인 관점에서는 수긍할수 있는 방법이나, 부품의 통합을 위해 아날로그 기능을 통합하는 것이 언제나 타당한 것은 아니다. 그 이유 중 하나는 무선 부품이 가진 다수의 아날로그 기능들이 효과적으로 통합될 수 없기 때문이다.

예를 들어, 〈그림 1〉은 기존의 IF 샘플링 수신기를 나타낸 것이다. IF 샘플링 아키텍처는 저잡음 이득 및 RF 선택도(selectivity), 주파수 변환, IF 이득 및 선택도, 감지 등 네 가지의 기본 단계로 구성되어 있다. 선택도에는 일반적으로 SAW 필터가 사용된다. 이러한 장치들은 통합될 수 없기에, 칩 상에 위치할 수도 없다. RF 선택도는 압전방식 또는 기구적 장치로 제공되지만, 종종 IF 필터로는 LC 필터가 사용되기도 한다.

LC 필터는 간혹 일체식 구조에 통합될 수 있기는 하지만, 두 필터 성능(Q 및 삽입 손실)을 절충해야하고 디지타이저(검출기)의 샘플링률을 높여야 하기에 결국 전체적인 전력 소비는 증가한다.

디지타이저(ADC)는 비용과 전력 소비를 적정 수준으로 유지하기 위해 저비용 CMOS 공정에서 구현되어야 한다. 디지타이저를 바이폴라 단계에서 구현할 수도 있지만, 이 경우 장치의 크기 및 전력 소비가 증가하기에 크기를 최적화하는 데에는 적절하지 않다. 따라서 크기의 최적화를 위해서는 표준 CMOS 공정이 가장 적절하다.

이는 고성능 증폭기의 통합에, 그 중 특히 IF 단계를 통합하는데 문제가 된다. 증폭기를 CMOS 공정에 통합할 수는 있지만, 저전력, 저전압에 최적화되어 있는 공정이 요구하는 만큼의 성능을 구현하는 것은 어려운 일이다. 더욱이 믹서와 IF 증폭기를 칩에 통합시키려면 단간(interstage) 신호가 디지털화되기 전에 신호의 경로가 칩을 벗어나 IF 및 안티앨리어싱 필터에 접근하도록 설정해야 하는데, 이 경우 통합으로 인해 생기는 이점을 상당수 포기해야 한다.

다시 말해 핀 개수와 패키지 크기가 증가하기 때문에 통합에 역효과가 발생한다. 뿐만 아니라 주요 아날로그 신호가 패키지 핀을 통과할 때마다 성능 저하가 발생한다.

최적의 통합 방법은 시스템을 재파티셔닝해 통합 불가한 항목들을 제거하는 것이다. SAW 필터 및 LC 필터는 효과적인 통합이 어렵기 때문에, 가장 좋은 방법은 아키텍처를 다시 설계해서 이들을 제거할 방법을 찾는 것이다.

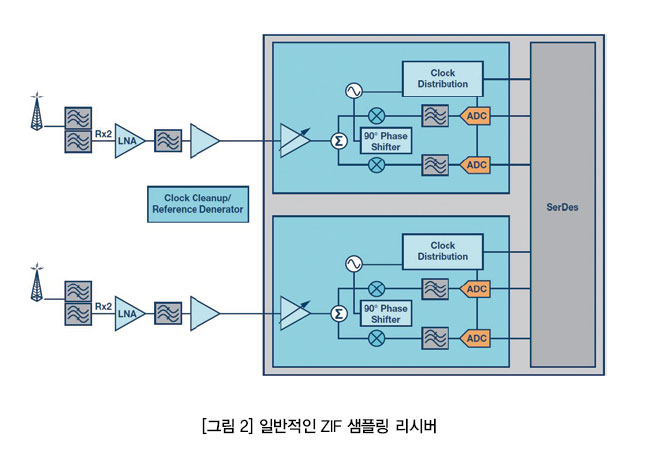

〈그림2〉는 RF 신호를 직접적으로 복합 기저대역으로 변환해 IF 필터 및 IF 증폭기의 필요를 완전히 제거함으로써 이러한 목표를 달성하는 일반적인 ZIF 신호 체인을 나타낸 것이다. 선택도는 오프 칩(off- chip)의 손실 고정 IF 장치 대신한 쌍의 저역 필터를 능동 저역 필터로 통합될 수 있는 I/Q 기저대역 신호 체인에 포함시킴으로써 구현된다.

기존의 IF SAW 필터 혹은 LC 필터가 그 특성상 고정되는 반면, 이러한 능동 필터는 수백 kHz에서 수백 MHz에 이르는 범위 사이에서 전기적으로 조정할 수 있다. 기저대역의 대역폭을 바꾸면 동일한 장치로 부품 사양을 바꾸거나 다른 고정 IF 필터 간의 변환 없이 넓은 대역폭을 지원하도록 할 수 있다.

그림을 통해 직관적으로 알 수는 없지만, ZIF 수신기 또한 국부발진기를 교체하는 것만으로도 방대한 RF 주파수범위를 지원할 수 있다. ZIF 트랜시버는 수백 MHz에서 최대 약 6 GHz에 이르는 일반적인 연속 범위에 해당하는 광대역 요건을 제공한다. 고정 필터가 없을 때 비로소 진정한 의미에서 유연한 무선 설계가 가능하고, 대역 변환에 필요한 노력을 크게 줄이거나 완전히 없앨 수도 있다.

ZIF 설계는 다양한 용도로 사용할 수 있는 디지타이저와 프로그램 가능한 기저대역 필터를 기반으로, 높은 성능뿐 아니라 넓은 주파수 범위와 대역폭에 적용할 수 있으면서도 각각의 구성에 대해 아날로그 회로(필터 등)을 최적화할 필요 없이 일관된 성능을 유지하는 유연성을 제공한다.

진정한 소프트웨어 정의 무선(Software Defined Radio, SDR) 기술인 것이다. 또한 여러 대역을 지원해야 하는 애플리케이션에서 필터를 다수 제거할 수 있어 풋프린트를 줄이는 데 크게 기여한다. 경우에 따라서는 RF 필터를 아예 제거하여 대역을 바꿀 필요가 없는 완전한 광대역 무선 부품을 구현할 수도 있다.

일부 장치를 제거하고 다른 장치들을 통합함으로써 ZIF 설계에 필요한 PCB풋프린트를 크게 줄일 수 있고, 이는 곧 대역 변환(re-banding) 과정을 단순화할 뿐만 아니라 필요 시 폼팩터를 바꿔야 하는 불필요한 노력도 줄일 수 있게 한다.

최소 풋프린트

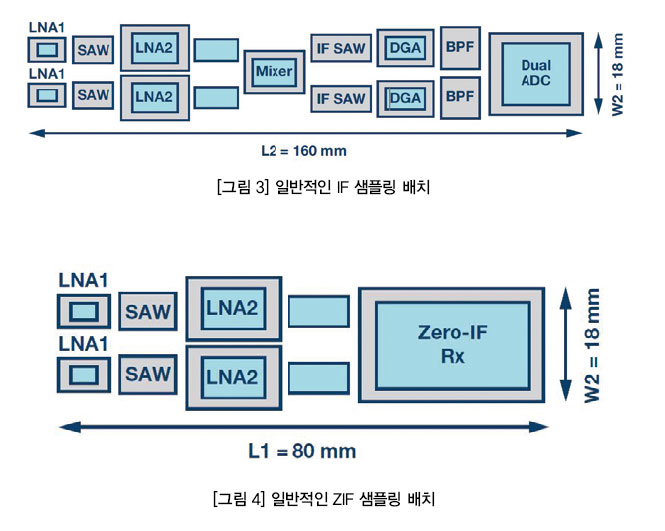

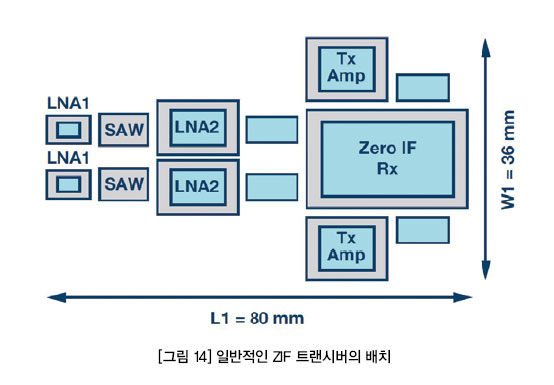

이들 아키텍처 각각에 대한 PCB 영역을 직접 비교해 보면(그림 3 및 그림 4), 이중 수신 경로를 합리적으로 구현하기 위한 PCB 영역은 IF 샘플링에 2,880 mm2(18 mm×160 mm), ZIF 샘플링에 1,434 mm2(18 mm×80 mm)가 필요하다는 것을 알 수 있다. RF 필터 및 기타 단순화를 위한 부품의 제거를 고려하지 않는다면[2], ZIF 아키텍처는 현재의 IF 샘플링 기술과 비교했을 때 무선 풋프린트를 최대 50%까지 줄일 수 있다. 차세대 설계에서는 추가적인 통합으로 풋프린트를 두 배 더 줄일 수 있을 것이다.

최소 비용

사용되는 부품의 관점에서 볼 때, IF 샘플링 시스템에서 ZIF 아키텍처로 전환할 시 비용을 33% 절감할 수 있다. 비용 분석은 언제나 까다롭지만 〈그림1〉과 〈그림 2〉를 자세히 보면 IF 및 안티 엘리어싱 필터를 비롯해 개별 부품이 상당수 제거됐으며, 믹서와 기저대역 증폭기가 통합됐음을 알 수 있다. 한가지 분명하지 않은 것은, ZIF 수신기가 선천적으로 기존의 IF 샘플링 아키텍처에는 없는 대역 외 제거 기능을 제공하기에 전체적인 외부 필터링 요건이 크게 줄었다는 점이다.

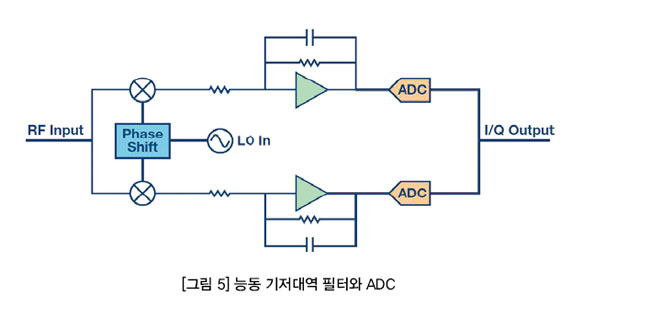

ZIF 아키텍처에서 이를 가능하게 하는 두 가지 요소가 있다. 첫 번째는 능동 기저대역 필터로 대역 내 이득 및 대역 외 제거 기능을 모두 제공한다. 두번째는 높은 샘플링률을 가진 저역 Σ- Δ 컨버터로 I/Q 신호를 디지털화하는데 사용된다. 능동 필터는 대역 외 부품 수를 줄이는 데 도움이 되며, ADC의 높은 샘플링률은 외부 안티 앨리어싱을 위한 필터링이 필요하지 않을 정도의 높은 주파수로 앨리어싱 포인트를 이동시킨다(이는 능동 필터가 그러한 신호를 충분히 제거해주기에 가능하다).

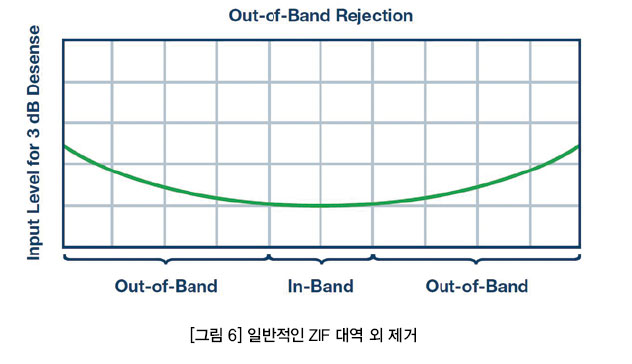

기저대역 신호를 〈그림 5〉와 같이 능동 필터에 적용시켜주면 높은 주파수의 신호는 롤 오프(roll- off)된다. 이후 ADC는 저역 필터의 출력을 디지털화하고 궁극적으로 필터링한다. 캐스케이드식 시스템의 결과는 〈그림 6〉에서 확인할 수 있다. 그림은 일반적인 수신기 성능이 능동 필터와 Σ- Δ ADC의 복합적인 영향으로 어떻게 나타날 수 있는지를 보여준다. 여기서는 내역 내 및 대역외 출력 모두에서 일반적인 3 dB 디센스(desense)를 확인할 수 있다. 외부 필터링 없이 대역 외 성능이 향상된 점에 주목해야 한다.

성능 수준이 비슷할 경우 IF 샘플링 수신기는 선택도 및 대역 외 신호로부터의 보호를 위해, 또 광대역 신호의 앨리어싱을 막고 잡음이 대역에서 다시 앨리어싱되는 일을 막기 위해 SAW 기술 등 개별 IF 필터링을 사용한다. IF 샘플링 아키텍처는 반 IF(half- IF term) 및 기타 원치 않는 믹서(mixer term)로부터 보호를 받아야 하며, 이 경우 RF 및 IF 필터링 요건이 추가되고 샘플링율과 IF 플래닝이 제한된다. 반면 ZIF 아키텍처에는 RF 플래닝에 제한이 없다.

이렇게 내재된 대역 외 제거 기능은 설계 및 애플리케이션에 따라 외부 RF필터링의 필요성을 감소시키거나 완전히 없애 주기도 한다. 외부 RF 필터는 유형에 따라 상대적으로 비쌀 수 있기에, 이 경우 비용을 직접적으로 절감할 수 있게 된다. 또한 이러한 손실 장치를 제거하면 RF 이득 단계를 없앨 수 있어 비용을 줄일 수 있을 뿐만 아니라 전력소모를 줄이고 선형성을 향상시킬 수 있다. 재파티셔닝 및 통합으로 얻게 되는 비용 절감 효과와 함께 제공되는 이점들이다.

앞서 언급한 바와 같이 비용은 생산량 및 판매자와의 계약 내용에 따라 크게 달라지기에 산정하기가 어렵다. 하지만 상세히 분석한 결과, ZIF 아키텍처는 통합, 제거, 요건 감소를 통해 일반적으로 전체 시스템 비용을 최대 1/3까지 줄여준다는 것을 알 수 있었다. 여기서 절감되는 비용이 시스템 비용이지 장치비용이 아니라는 점에 유의해야 한다.

보다 적은 수의 장치에 많은 기능을 탑재하는 추세이기에 전체 시스템 비용이 감소하더라도 일부 장치의 비용은 증가할 수 있다.

부품 구성 비용 외에도 통합 ZIF 수신기는 다른 몇 가지 문제점들도 해결할 수 있다. 통합 시스템이 시스템에 사용되는 장치의 개수를 줄여주기에 조립비용이 낮아지고 공장 생산량이 증가한다. 또한 개별 장치의 수가 줄어들기에 장치를 배치하는 데 소요되는 시간도 짧아진다. 이러한 모든 요소들이 어우러져 제조 원가를 절감할 수 있게 된다.

ZIF 수신기는 광대역을 다루므로 대역을 재설정하는데 소요되는 엔지니어링 비용을 줄일 수 있다. IF 샘플링 시스템에서는 IF 주파수를 신중히 선택해야 하는 반면, ZIF 시스템에서는 이런 신중함을 필요로 하지 않는다. 국부발진기를 변경하는 것으로 새로운 대역을 대거 추가할 수 있게 된다.

또한 ZIF를 사용할 시 대부분의 애플리케이션이 외부 RF 필터를 필요로 하지 않기에 공정을 더욱 간소화할 수 있다. 결국 위에서 설명한 제조 및 엔지니어링 비용과 더불어 직접 비용을 중요하게 고려한다면 ZIF 솔루션을 사용해 절감하는 비용은 상당한 수준이라고 볼 수 있다.

최저 전력

단순히 〈그림 1〉에 나타난 것과 같은 아키텍처를 온칩 시스템에 바로 적용 및 통합한다고 해서 전력이나 비용을 줄일 수 있는 것은 아니다. 목표로 하는 공정에 최적화할 수 있는 효율적인 아키텍처를 사용해야 전력 사용량을 절감할 수 있다. 〈그림 1〉과 같은 아키텍처를 지닌 IF 샘플링 수신기는 저비용 공정에선 조정하기 어려운 고주파나 중저파를 사용하므로, 필요한 주파수를 지원하기 위해 상당한 전력이 소모된다. 그러나 〈그림 2〉에서 보는 것과 같은 ZIF 아키텍처는 즉시 해당 주파수를 DC(기저대역)로 낮추어 최저주파 회로의 구현을 가능케 한다.

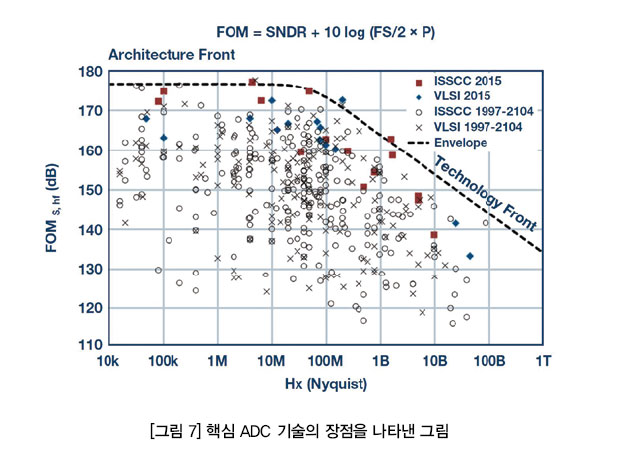

마찬가지로 단순히 대역폭 만으로 문제를 해결하려는 시도 역시 비효율적이다. 직접 RF 샘플링 같은 아키텍처는 상당히 유연하면서도 넓은 대역폭을 제공한다. 그러나 월든(Walden)[3]과 멀맨(Murmann)[4]이 말한 것처럼 시스템에 대역폭을 추가하면 전력 사용량도 반드시 늘어나게 된다.

있는 그대로의 대역폭이 필요한 상황이 아니라면 대부분의 수신기 애플리케이션에서 대역폭만으로 이러한 문제를 처리하려는 접근은 그다지 경제적인 해결 방안이 되지 않는다. 장기적인 연구로부터 도출된 데이터는 컨버터 개발의 두 가지 영역을 보여준다. 기술영역은 동적 범위와 대역폭의 형태로 핵심 AC 성능을 상당히 향상시킨 기술을 기록한다. 반면 아키텍처 영역은 핵심 아키텍처의 전반적인 효율성 향상을 기록한다.

일반적으로 효율성 곡선은 처음에는 오른쪽으로 움직였다가, 설계가 최적화되면서 점점 위로 올라가기 시작한다.

통신 애플리케이션에서 컨버터는 〈그림7〉에서 보듯이 효율이 10× 대역폭당 10dB 감소하는 경사 영역에서 사용된다.

이 경사에서 대역폭을 두 배로 늘리면 전력 소비는 약 세 배가량 증가한다. 그러나 이러한 핵심 기능이 기능 장치에 통합될 때에는 효율이 향상되어서 일반적으로 효율이 아키텍처 영역으로 가까이 이동할 때 전력 손실이 2에 가까워진다.

결론적으로 전력 소비와 관련된 어플리케이션에서 최저 전력을 위한 솔루션은 대역폭과 샘플링율을 해당 어플리케이션에 대해 최적화하는 것이다. Σ- Δ 컨버터를 사용한 ZIF 샘플링은 이런 애플리케이션에 대해 최적화되어 있다.

특정 구현 방식에 따라 ZIF 수신기를 구현하면 전력 소비를 IF 샘플링 아키텍처 대비 50 % 이상, 직접 RF 샘플링대비 최대 120%까지 절감할 수 있다.

전력 소비는 비용과도 직결된다. 전력소비가 높아지면 패키징 비용 및 공급량 생산이 증가할 뿐 아니라, 회로가 소비하는 전력이 kW/hr당 12센트일 때 작동 비용이 연간 와트당 1달러가 넘게된다. 전자 장비 대부분의 비용이 낮은 점을 감안할 때, 이들을 단 1년 간 작동시키는 데 소비하는 전력만으로도 직접비용을 초과할 수 있는 것이다.

이렇듯 통합 무선 솔루션에 선택지가 생기면서, 비용 및 전력 소모에 민감한 애플리케이션을 선택할 때에는 그 득실을 신중히 고려해야 한다. 불필요하게 전력소비를 높이는 아키텍처를 선택할 시, 전력 소비가 늘어나는 것은 물론이며 해당 솔루션의 장기적인 작동 비용에도 영향을 미칠 수 있다.

성능 향상

무선 설계에 중요시되는 여러 가지 주요 측정 기준이 있다. 이러한 측정 기준에는 잡음 지수(NF), 선형성(IP3, IM3), 감도 열화(desensitization), 선택도 등을 들 수 있다. 일반적인 무선 사양 외에도 중요하지만 대부분의 사용자는 모르고 지나가는 사양들이 있다. 여기에는 시간, 공급량, 온도, 공정의 기능으로 사양 분배 및 드리프트가 포함된다. ZIF아키텍처는 이러한 사양과 무선 설계를 위한 기타 주요 요건을 만족시킨다.

온도, 공급량 및 공정 추적하기 완전 통합된 트랜시버 아키텍처의 장점 중 하나는 제대로 설계된 무선 부품의 경우 장치 일치 성능이 훨씬 뛰어날 수 있다는 것이다. 이는 장치가 제대로 설계된 경우 시간, 온도, 공급량, 주파수에 따라 효과적으로 장치 추적이 가능하기 때문이다. 일치되지 않은 부분이 남아 있다면 즉시 통합 솔루션에 일반적으로 내장된 신호 처리 기법을 통해 제거될 수 있다.

이러한 과정은 IC설계에서 아주 일반적이지만, 무선 장치 통합에서 갖는 차이점이 있다면 ZIF설계에서는 주파수에 영향을 받는 모든 부품이 칩 상에 위치하기에 이들도 모두 추적 가능하다는 것이다. 〈그림 1〉에서 보는 것과 같은 일반적인 무선 부품에는 칩 외부에 IF 필터가 존재한다.

이러한 IF 필터의 특성은 시간, 온도, 장치 간의 기능에 따라 달라지며, 그 결과 칩 상의 무엇과도 상관 관계가 없어 추적이 불가능하다. 하지만 필터를 통합했을 때의 가장 큰 장점은, 온칩 디바이스로 구성되기에 장치를 조정하거나 비율계량(ratiometric) 방식으로 각각을 추적할 수 있어 성능을 안정적으로 유지할 수 있다는 것이다. 설계만으로는 안정화할 수 없는 장치들을 손쉽게 보정할 수 있게 되는 것이다. 그 결과, 장치 변경을 고려할 시 장치 간 상관관계가 없는 개별 설계에 비해 훨씬 적은 비용을 필요로 한다.

예를 들어 종종 믹서, IF 필터, IF 증폭기 및 ADC에 각각 1 dB의 NF 변화를 할당하는 경우가 있다. 성능을 고려할 때 이러한 변화는 단계적으로 이뤄져야 한다. 그러나 모든 주요 사양이 서로 추적 혹은 보정하는 통합 설계는 하나의 장치만 1 dB만큼 변화시키면 되기에 신호 체인 변화를 크게 간소화할 수 있다.

이는 부품 간 상관관계가 없어 잡음이 증가할 가능성을 상쇄하기 위해 추가적인 시스템 이득이 필요한 설계와 비교해 큰 차이가 있으며, 최종 제품의 비용, 전력 소비, 선형성에 상당한 영향을 미친다. 〈그림 2〉에서 보는 것과 같은 통합설계에서 전체 성능의 변화는 상관 관계가 없는 설계에 비해 상당히 미미하며, 그 결과 필요한 시스템 이득도 작다.

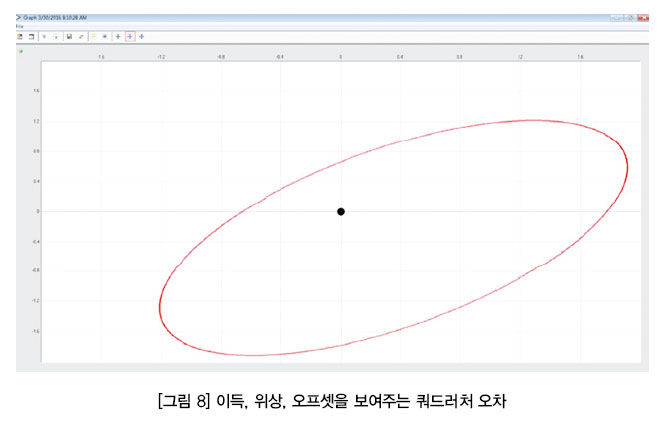

향상된 보정 기법

ZIF 수신기는 일반적으로 과거에 우려를 야기했던 두 가지 영역이 있다. 복잡한 데이터는 실제 및 가상의 부품을 나타내는 실제 캐스케이드 네트워크의 쌍으로 생성 및 표시되기에 〈그림 8〉에 나타난 것처럼 개별 신호 체인의 이득, 위상, 오프셋을 나타내는 오차가 발생한다.

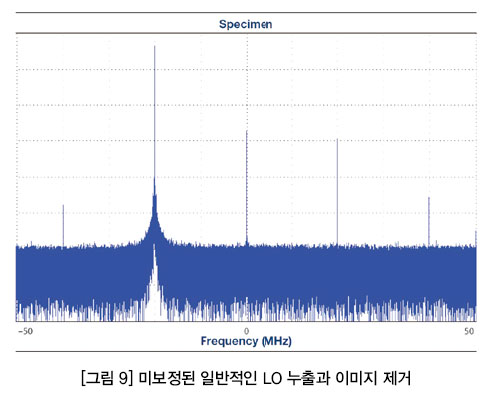

이러한 오차는 위 스펙트럼 상의 이미지처럼 나타나며, 일반적으로 해당 아키텍처들이 더욱 널리 적용되지 않았던 이유가 되기도 했다. 그러나 통합 솔루션을 활용하면, 아날로그 최적화 및 디지털 보정을 통해 이러한 오차를 쉽게 제어할 수 있게 된다. 〈그림 9〉는 보정되지 않은 복잡한 데이터가 일반적으로 나타나는 모습이다. 여기서는 LO 누출(과 DC 오프셋) 및 이미지 제거(쿼드러처 오류)를 모두 확인할 수 있다.

LO 누출 제어

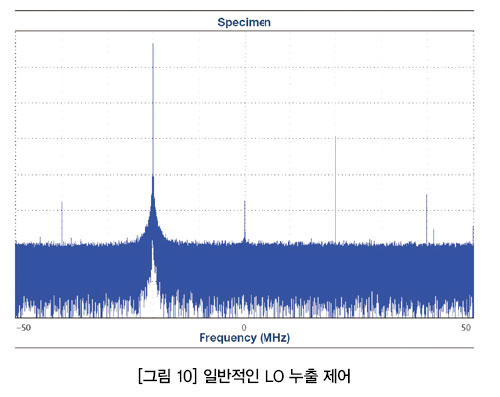

LO 누출은 I 혹은 Q 신호 경로에서 DC오프셋의 증가로 나타난다. 이러한 LO누출은 LO가 RF 신호 경로와 직접 결합되어 출력으로 일관되게 다운 컨버티드(down converted)될 때 발생한다. 이렇게 발생한 믹서는 DC 오프셋으로 표기되어 신호 체인의 잔여 DC 오프셋에 더해진다. 뛰어난 ZIF 아키텍처는 이런 오차를 초기는 물론, 시간, 온도, 공급 및 공정이 변화함에 따라 자동으로 추적하고 보정하여 〈그림 10〉과 같이 - 90 dBFS 이상의 성능을 구현해 낼 수 있다.

QEC

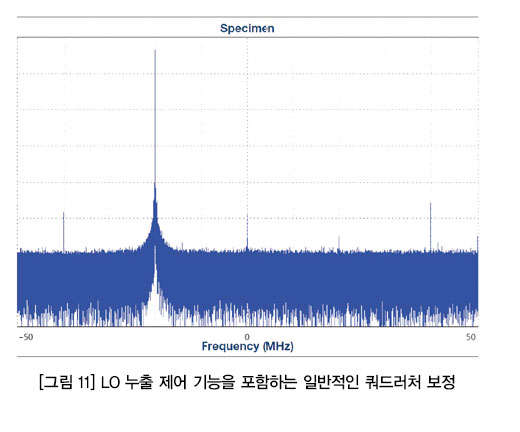

이미지가 성능을 저하시키는 일을 방지하기 위해 일반적으로 쿼드러처 오차 보정(quadrature error correction, QEC) 기능이 사용된다. 〈그림 11〉은 그러한 기능이 미칠 수 있는 영향을 보여준다. 본 예시의 이미지는 - 105 dBc 이상으로 향상되는데, 이는 대부분의 무선 애플리케이션에 충분하고도 남는 성능이다. LO 누출과 QEC 모두 시간에 따라 성능이 변하더라도, 항상 최적의 성능을 유지하도록 보정이 이루어지는 지 확인하기 위해 추적이 적용된다.

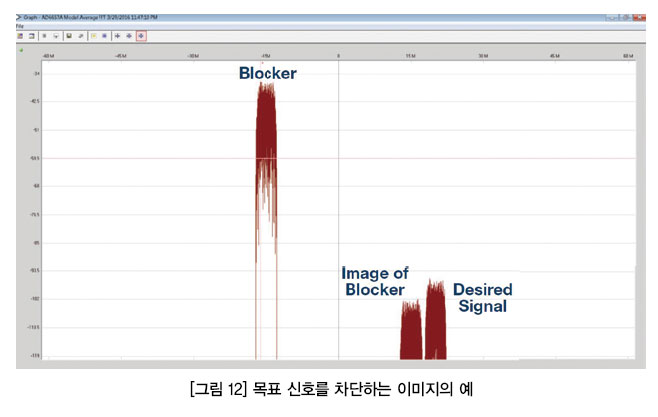

무선 시스템에 있어 쿼드러처 오차와 LO 피드스루는 중요하다. 오차가 충분히 크다면, 큰 블로커(blocker)의 이미지가 그보다 작은 목표 신호를 가릴 수도 있다. 〈그림 12〉는 큰 블로커의 이미지가 15 MHz일 때 목표 신호가 20 MHz를 중심으로 위치한 모습을 보여준다. 해당 이미지가 부분 또는 전체적으로 목표 신호 위로 겹쳐지면 목표 신호의 SNR을 떨어뜨려, 복조 시 오차가 발생할 수 있다. 보통 LTE 및 W- CDMA 같은 시스템이라면 이러한 이미지에 대한 허용 오차가 상당히 크기는 하지만, 그렇다고 해서 이에 대해 전혀 영향을 받지 않는 것은 아니다.

일반적으로 이러한 시스템은 75 dBc 이상의 이미지 제거 성능이 요구되며, 이는 〈그림 11〉에서 보듯이 ZIF 아키텍처를 사용하면 쉽게 만족 및 유지할 수 있다.

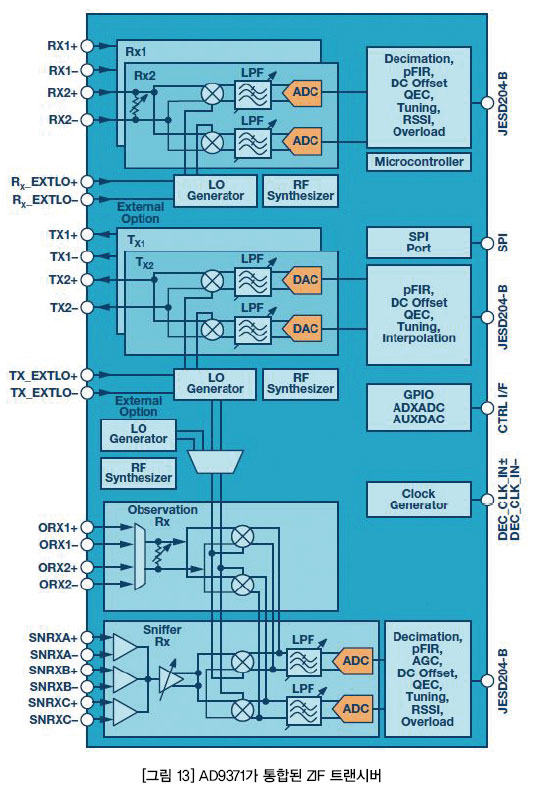

AD9371

ZIF 송신 및 수신의 대표적인 예는 AD9371이다. 〈그림 13〉에서 볼 수 있듯이, AD9371는 통합 AGC, DC 오프셋 보정(LO 누출 제어), QEC 뿐만 아니라 관찰 및 스니퍼 수신기까지 포함하는 추가 기능과 함께 듀얼 송신, 듀얼 수신 등 아주 높은 수준의 통합된 기능성을 제공한다. AD9371은 300 MHz에서 6 GHz에 이르는 넓은 RF 범위를 지원한다.

각 송신기는 20 MHz~100MHz의 합성 대역을 지원할 수 있으며, 각 수신기는 5 MHz~100 MHz의 범위를 지원할 수 있다. AD9371은 3G와 4G 애플리케이션을 대상으로 하지만, 최대 6 GHz의 대역이 사용되는 여러다른 범용 무선 및 소프트웨어 정의 어플리케이션에 사용하기에도 적합한 솔루션이다.

AD9371은 앞서 말한 모든 주파수 기반 장치와 더불어 모든 보정 및 할당 기능을 12 mm×12 mm BGA 패키지에 통합해 넣은 완전한 시스템을 제공한다. 〈그림 4〉의 수신 기능 외에도 〈그림 14〉에는 풋프린트에 필요한 송신 기능도 추가해서 아주 콤팩트한 듀얼 송수신 설계를 완성했다. 전력 소비는 대역폭, 기능 등 정확한 구성에 따라 달라지지만, AD9371의 경우 일반적으로 LO누출 및 이미지 제거를 유지하는 디지털 기능을 포함하더라도 4.86W에 불과하다.

AD9371의 주요 성능

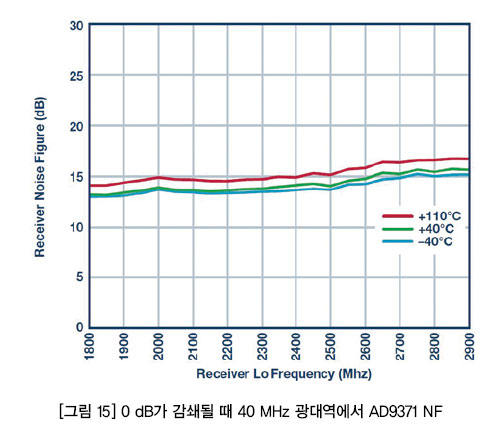

잡음 수치

〈그림 15〉 및 〈그림 16〉은 AD9371의 일반적인 NF 특성을 보여준다. RF 주파수의 넓은 스위프(sweep)를 나타내는 〈그림 15〉를 보면 NF가 이 스펙트럼상에서 상대적으로 평평한 모습을 보임을 알 수 있다. 이 장치의 입력 구조는 NF가 dB 단위로 증가하도록 감쇄기의 형태를 하고 있다. 감쇄 없이 NF가 16 dB인 최악의 경우, 외부 이득 변화가 약 4 dB 감쇄되도록 가정하면, 전체 NF는 20 dB라고 생각할 수 있다.

최소 24 dB의 이득을 제공하는 외부 LNA(0.8 dB)라면 2 dB의 시스템 NF를 제공하게 된다.

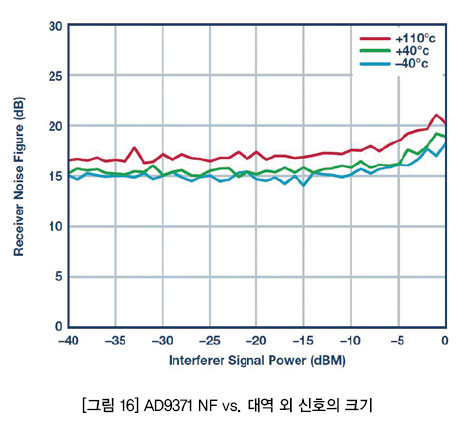

〈그림 16〉은 AD9371의 입력에 대해 대역 외 블로커의 기능을 하는 NF를 보여준다. 외부 이득을 24 dB라고 가정하면, 이 장치의 입력 단에 대해서 0dBm의 값은 안테나 연결 장치에 대해 - 24dBm 일 때 생겨날 수 있다 .

AD9371의 영향만을 고려한다면, 전체적으로 NF가 1 dB 감소한 것은 통합 수신기에서 3 dB만큼 감소한 것과 동일할 것이다.

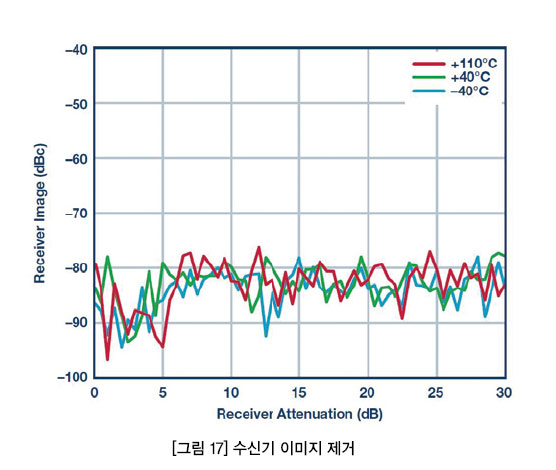

이미지 제거

LO 누출과 마찬가지로, 수신 이미지제거는 〈그림 17〉의 정보를 통해 추정할 수 있다. - 40 dBm 안테나의 일반적인 입력 수준에서 이미지는 안테나 포트에 비례해 80 dB 낮은 - 120 dBm로 추정할 수 있다.

결론

그동안 ZIF 아키텍처는 저성능 애플리케이션에 한정적으로 사용되어 왔지만, AD9371 같은 새로운 제품은 업계의 판도를 바꿀만한 성능을 제공한다.

이러한 장치는 IF 샘플링 수신기에 준하는 성능을 제공할 뿐만 아니라, 무선부품을 다시 파티셔닝함으로써 제조 비용은 물론, 설치 후 작동 비용까지도 절감할 수 있는 견고한 아키텍처를 구현한다. 더 이상 솔루션 비용이 낮은 설계를 채택하기 위해 무선 성능을 희생할 필요가 없기 때문에, 사용자들은 이제 자원과 시간을 무선 부품의 구현이 아닌 애플리케이션 개발에 투자할 수 있게 될 것이다.

● 참고자료 [1] 이번 논의가 주로 수신기(Rx)에 집중되어 있기는 하나, 송신기(Tx)에도 동일하게 적용될 수 있다. |

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>