글 | 토마스 뉴(Thomas Neu), 고속 데이터 컨버터 시스템 엔지니어 Texas Instruments

.jpg)

JESD204B 인터페이스는 기존의 병렬식 상호연결 방식에 비해 명쾌하고 훨씬 유연성 있는 디지털 인터페이스다. 이 새로운 인터페이스로 옮겨갈 때 시스템 설계자는 클로킹이나 동기화 등 여러 요소를 고려해 봐야 한다.

최근 JESD204B라는 새로운 인터페이스에 대해 말이 많았다. 이 새로운 인터페이스 표준은 고속 데이터 컨버터와 디지털 프로세서 혹은 FPGA 간의 디지털 상호연결 문제를 다룬다. 이 인터페이스는 기존의 저속 CMOS나 LVDS 인터페이스와 대조적으로 디지털 데이터를 전송하기 위해 고속 직렬 인터페이스를 사용한다. 이 새로운 인터페이스가 전반적인 설계의 복잡성이나 보드 공간과 비용을 절감하는 이점이 있긴 하지만, 시스템 설계자라면 JESD204B 인터페이스로 전환할 때 설계상 많은 부분을 주의 깊게 살펴 볼 필요가 있다.

이 글에서는 JESD204B 인터페이스의 시스템 부분을 살펴보고자 한다(그림 1). 샘플링 비율과 AC 성능 규격 외에 아날로그-디지털(ADC) 변환이나 디지털-아날로그(DAC) 변환 소자 선택에 영향을 주는 새로운 매개변수가 몇 가지 있다.

.jpg)

.jpg)

가장 중요한 매개변수로는 여러 JESD204B 하위 클래스(다중 채널 애플리케이션에서 중요) 지원이나 내부 클록 디바이더를 이용하는 고조파 클로킹이 들어간다. 대기시간에 민감한 산업용 및 군용 애플리케이션의 경우는 총 데이터 링크 대기시간이 가장 결정적인 요소가 될 수 있다.

그 밖에 새로운 주요 규격으로는 FPGA 클래스와 비용을 결정하는 직렬 인터페이스 최대 지원 속도 및 지원 JESD204B 링크 구성이 있다. JESD204B 표준은 링크 구성 자체는 매우 자유롭지만 전송 디바이스와 수신 디바이스 간 호환성은 시스템 설계자가 해결해야 할 몫이다.

컨버터 클로킹

JESD204B-기반 시스템에서는 데이터 컨버터 클록이 2가지 기능을 한다(그림 2). 샘플링 클록이 저-지터 클록이므로 ADC 직렬 컨버터와 DAC 직/병렬 컨버터에서 고속 클록을 생성할 때 사용한다.

.jpg)

JESD204B는 20% 여유 처리시간이 있는 8비트 데이터를 10비트 워드(혹은 16비트 데이터를 2개의 10비트 워드)로 인코딩 하는 8b/10b 인코딩 방식을 이용한다. 이 인코딩 방식을 사용하면 0이나 1로 된 고정된 패턴을 전송해도 전송한 데이터를 충분히 변환하여 직병렬 컨버터의 위상 동기 루프(Phase-locked loop, PLL)가 내장 클록을 복구할 수 있다. 따라서 8b/10b 인코딩은 16비트 해상도의 ADC가 각각의 포착한 샘플을 20비트로 전송한다. 이제 출력 데이터가 하나의 차동 방식을 이용해 20배의 샘플링률로 전송되거나 2개의 레인을 이용해 10배의 샘플링률로 전송된다.

ADC16DX370

두 번째, 입력 클록을 사용해 동기화 입력 신호를 포착해 내부 기준 클록이나 로컬 다중 프레임 클록(LMFC)을 리셋한다. MIMO 구성 시 필요한 다중 채널은 다중 데이터 컨버터의 디바이스 클록의 위상을 동기화하고, 이 동기화 신호를 동시에 유지하는 방식으로 동기화 한다(그림 3). 클록 타이밍과 동기화를 정확히 관리하는 것이 무척 중요한 역할이며 여기에 대해서는 나중에 자세히 다룰 것이다. 흔한 예로 LMK04828 JESD204B 클록 지터 클리너 같은 단일 디바이스로 컨버터 샘플링 클록과 동기화 신호를 분배하여 디바이스 간 편향(skew)을 최소화 한다.

또한 JESD204B 표준은 고조파 클로킹 개념도 도입하여 시스템에 있는 각 디바이스에 정확한 샘플링 클록 주파수를 제공할 필요가 없어졌다. 기본 샘플링률의 몇 배에 해당하는 하나의 다중 주파수(2, 4, 8배 등)를 분배해 시스템 클록 트리를 단순화 할 수 있다. 그런 후 개별 데이터 컨버터는 내부 클록 디바이더를 이용해 필요한 클록 주파수를 생성할 수 있다.

하위 클래스 0, 1, 2 ?

JESD204B 표준에는 다중칩 동기화에 주로 영향을 주며 결정적 지연 기능을 지원하는 3가지 하위 클래스(0, 1, 2)가 있다. 데이터 컨버터가 하나나 둘, 혹은 전 세 개 하위 클래스를 모두 지원할 수도 있다(ADS42JB69 듀얼, 16비트, 250-MSPS ADC 등). 애플리케이션에 따라 어떤 하위 클래스를 지원하느냐가 컨버터 선택에 중요한 요소로 작용하게 될 것이다.

.jpg)

하위 클래스 0은 최고 12.5Gbps의 높은 라인율 등 JESD204 개정본 B에 추가된 기능을 지원하는 동시에 JESD204A의 하위 호환성도 유지한다. 하위 클래스 0으로도 많은 애플리케이션에 사용할 수 있긴 하지만 하위 클래스 1과 2만 결정적 지연 기능을 지원한다. 결정적 지연 기능은 JESD204B 트랜스미터와 리시버 간에 고정된 디지털 링크를 구축해 준다.

데이터 전송 시작은 로컬 다중 프레임 클록(LMFC)이라는 내부 기준 시계를 기준으로 한다. 동기화 신호를 이용하는 여러 디바이스 간에 LMFC 클록을 동기화함으로써 다중칩 동기화를 크게 간소화할 수 있다. 하위 클래스 1에서는 외부 SYSREF 신호를 동기화 신호로 사용하여 결정적 지연 기능을 구현하고, 하위 클래스 2는 SYNCb 신호를 이용한다(표 1).

하나의 클로킹 디바이스로 샘플링 클록과 SYSREF 신호를 분배할 수 있어서 매우 정확하게 위상을 동기화 하고 디바이스 간 편향을 최소화 할 수 있어 시스템 설계자 중에는 하위 클래스 1을 사용하는 사람이 많다.

결정적 지연(Deterministic Latency)이란 ?

JESD204B에서 도입한 가장 좋은 기능 중 하나가 바로 로직 디바이스와 데이터 컨버터 링크 간 결정적 지연이다. 전송 및 수신 경계 간 스패닝을 포함하여 다중칩 동기화 과정이 상당히 간소화된다. 데이터 컨버터에는 서로 다른 클록 도메인에서 운용할 수 있는 다양한 블록뿐만 아니라 프로세스, 온도, 공급 전압 변동에 민감한 전파 지연 기능도 있다. 따라서 여러 개의 트랜스미터와 리시버 간 링크 지연 폭이 넓어진다.

.jpg)

JESD204B에서는 공통 디바이스 클록을 모든 컨버터에 배분한 후 각 디바이스 내부 클록을 생성한다. 내부 클록 디바이더로 원하는 샘플링률을 만들면 위상의 모호성이 증가한다. 예를 들어 두 블록으로 나뉜 구조에서 시작 조건에 따라 0°이나 180° 위상으로 된 1/2 클록을 생성하여 불확실성이 커질 수 있다.

앞서 말한 것처럼 JESD204B 표준에는 송수신 디바이스 간 링크에 결정적 지연을 만드는 하위 클래스가 2개 있다. 하위 클래스 1은 외부 SYSREF을, 하위 클래스 2는 SYNCb 신호를 동기화 신호로 이용한다.

JESD204B 표준에 정의된 것처럼 결정적 지연은 JESD204B 송수신기 간에 이루어지는 반복 지연을 우리가 알고 있는 수치로 유지하여, 전원이나 링크 재동기화 주기 간에는 편차가 없다.

동기화 신호(SYSREF나 SYNCb)는 모든 내부 블록(입력 클록 디바이더 등)을 알려진 상태로 리셋할 때 사용한다. 내부 기준 클록이나 로컬 다중 프레임 클록(LMFC)의 위상을 동기화 신호 샘플을 취한 디바이스 클록 가장자리에 맞춘다. 그러나 모든 외부 동기화 신호뿐 아니라 다양한 디바이스 클록 간에 서로 길이를 맞춘다는 가정을 전제로 한다.

시스템 엔지니어는 외부 동기화 신호가 디바이스 클록의 설정 시간이나 유지시간과 일치하도록 해야 한다. 단 ADS42JB69와 같은 데이터 컨버터에는 SYSREF 입력부에 프로그램 가능한 지연 완충 공간이 있다. 이런 공간이 있기 때문에 고주파수 디바이스 클록에서는 정확한 시간 정규화에 큰 도움이 된다.

결정적 지연 구현

결정적 지연 절차에 대해서는 하위 클래스 1을 사용하여 아래에 예로 들었으며, 그림 4에 도식화 했다. 하위 클래스 2도 LMFC 동기화에 SYSREF 신호 대신 SYNCb 신호를 사용한다는 점을 제외하면 매우 유사하다.

1. SYSREF 신호를 배분하고 모든 디바이스에 대해 LMFC를 동기화 한다. 단사(one-shot), 간헐, 주기 신호 중 하나로 SYSREF를 사용할 수 있다. 주기나 간헐 신호로 구성한 경우에는 SYSREF 신호 주기가 LMFC의 정수 배수여야 다중 프레임 중 SYSREF 펄스를 피할 수 있다. 주기적 SYSREF 신호는 컨버터 샘플링 클록의 저조파 클록이므로 컨버터 성능에 의사 효과를 유발할 수 있다. 따라서 동기화 후 정상 운영 시에는 꺼놓는 경우가 종종 있다.

2. 링크를 구축한 후에는 수신 디바이스가 SYNCb 신호를 낮게 구동하여 코드 그룹 동기화(CGS) 요청을 한다.

3. 리시버가 K28.5 문자를 제대로 디코딩 한 후에는 SYNCb 신호를 높게 하여 그 다음 LMFC 경계에 있는 모든 JESD204B 링크에 대해 동시에 초기 레인 동기화(ILA) 시퀀스를 시작한다.

4. 수신 디바이스에 있는 탄성 FIFO가 모든 레인에서 들어오는 유입 데이터의 버퍼 역할을 하여 각종 물리적 링크 간 편향을 처리한다. 탄성 버퍼의 크기는 리시버(RX) 버퍼 입력부에 가장 먼저 데이터가 도착한 순간부터 그 다음 방출될 때까지 그 사이에 들어오는 모든 데이터를 저장할 정도여야 한다.

리시버 지연 허용(RBD)이라고도 하는 일정한 수의 프레임 사이클이 끝나고 LMFC 경계에 닿으면 방출이 일어난다. 모든 레인에서 나온 데이터가 그 다음 방출 기회가 오기 전 탄성 버퍼에 도착하도록 RBD 값을 선택해야 한다. RBD 값은 1~K 사이의 값으로 선택해야 한다. 그러나 K로 설정하는 경우도 있는데 이렇게 하면 결정적 지연이 다중 프레임 주기와 일치하게 된다.

지연 시간을 최소화 하려면 RBD를 훨씬 낮은 값으로 설정할 수도 있으나 디바이스 간 시간 편향처럼 실행 면에 한계가 있다(SYSREF를 내부에 등록하여 배분). 8b/10b 인코딩 같은 블록의 지연을 처리해야 한다(그림 5).

직렬 인터페이스

ADC16DX370 같은 최신 고속 컨버터는 대개 전압 모드(VML)나 전류 모드 로직(CML) 직렬 컨버터/직병렬 컨버터(SerDes) 트랜스미터를 사용한다(그림 6). CML에서는 2개의 스위칭 트랜지스터를 사용해 종단 레지스터를 통해 전류를 일정하게 유지하여 리시버에 차동 전압 강하를 일으킨다.

.jpg)

차세대 고속 데이터 컨버터는 한 차원 높은 CMOS 프로세스로 이동하고 있으므로 자체적으로도 훨씬 빠른 트랜지스터 스위칭 속도가 가능해 데이터율도 높아진다. 한편 저차원 CMOS 프로세스도 SerDes 블록의 디지털 전력 소모량이 크게 감소해 전반적인 디지털 인터페이스 설계 효율이 매우 높아지게 된다.

예를 들어 ADC16DX370는 7.4Gbps인 하나의 직렬 링크를 통해 샘플링한 데이터를 전송하여 보드 공간과 트랜스미터 전력소비량을 줄일 수 있다. 아니면 3.7Gbps인 2개의 직렬 레인으로 보드 공간 대신 FPGA 비용을 크게 낮추는 방법도 있다.

아이 다이어그램(Eye Diagram)

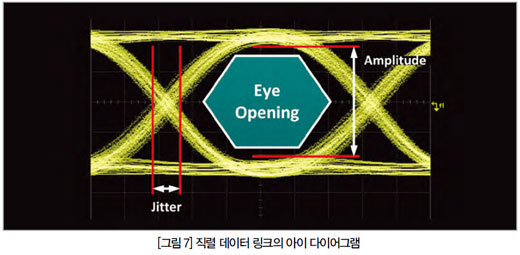

시스템 설계자는 보통 수신 디바이스의 아이 다이어그램으로 직렬 링크의 품질을 조사한다. 이 다이어그램은 고속 오실로스코프로 트랜스미터에서 나오는 개별 비트를 중첩하여 얻을 수 있다.

.jpg)

아이 다이어그램(그림 7)으로 리시버가 유입 데이트 스트림에서 얼마나 정확한 정보를 추출할 수 있는지 알아본다.

눈에 해당하는 진폭은 전송 채널의 유실량을 나타낸다. 수직 폭이 클수록 리시버의 정확한 로직 수준을 가늠하기 편하다.

지터는 신호가 0V(영 교차점)을 지날 때의 이상적인 전환점과의 편차를 지정한다. 입력 신호가 논리적으로 높거나 낮은 지 리시버에서 결정할 때 지터가 작을수록 타이밍 마진이 큰 것으로 해석한다.

지터가 링크 품질에 큰 영향을 주므로 JESD204B 표준에서는 트랜스미터(TX)와 리시버(RX)의 지터 요건을 규정하고 있다. 트랜스미터 지터는 출력에서 바로 측정한다. 여기에서 트랜스미터 자체가 전송 채널로 들어가기 전 아이 다이어그램을 어느 정도 저해하는지 알 수 있다. 수신 지터는 지터의 내성 요건을 측정한 것이다. 이 수치는 유입 데이터 스트림에서 정확한 정보를 추출하기 위해 리시버가 가져야 할 지터 내성 정도를 가리킨다. TX와 RX 지터 요건은 ~최고 3.125, ~최고 6.25, ~최고 12.5Gbps로 3가지 최고 데이터 범위 중 하나로 지정한다(그림 8).

능동 이퀄라이제이션 기술

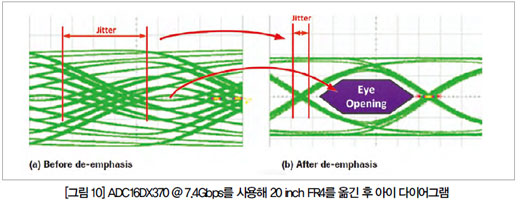

직렬 링크 품질은 주로 리시버가 유입 데이터를 어느 정도로 잘 복구하는 지에 달려있다. 전송 거리가 길수록 신호 감쇠가 일어나기 쉬워 아이 오프닝이 수축한다. 손실성 PCB 소재는 저역 필터처럼 작용한다. 삽입 손실을 계산하는 가장 효과적인 방법 중 하나가 프리앰퍼시스나 디앰퍼시스 전송 형태 고역 통과 필터를 추가하거나 SerDes 리시버에서 등화(equalization)하는 것이다. 프리앰퍼시스는 여분의 출력 전류를 추가해 신호 상승 및 하강 배수를 높여 고차 고조파의 진폭을 키운다. 한편 디앰퍼시스는 비트 전환이 전혀 일어나지 않을 때 신호 진폭을 줄여준다(저주파수 대역을 특히 감쇠). 따라서 채널의 삽입 손실을 보상할 때 프리앰퍼시스와 디앰퍼시스는 동일한 효과를 낸다(그림 9).

예를 들어 ADC16DX370는 다른 양의 디앰퍼시스와 출력 진폭 수준을 여러 가지 제공하므로, 채널의 손실 프로파일에 가깝게 조정할 수 있다. DAC38J84 쿼드 16비트 2.5GSPS DAC의 SerDes 리시버는 완전 적응 등화로 채널 삽입 손실을 자동으로 보상해 준다. 수신한 데이터를 기준으로 이동 함수의 영점을 맞추면 되는데, 그렇게 하면 심벌 간 간섭도 최소화 할 수 있다. 또한 그 리시버에는 내장형 아이 스캔과 등화 분석 기능이 있어 전송 대응자가 필요 이상으로 등화를 하지 않았는지 확인해 볼 수 있다. 디앰퍼시스가 있고 없는 상태에서 리시버의 아이 다이어그램을 보면 프리앰퍼시스와 디앰퍼시스의 장점을 확연히 알 수 있다(그림 10).

링크 구성

수신 디바이스가 전송된 데이터를 정확히 재구성하려면 송수신기의 링크를 동일하게 구성해야 한다. JESD204B 표준에는 여러 개의 매개변수가 있으나 송수신 디바이스 구성은 시스템 설계자가 해야 한다.

L = 컨버터 디바이스 당 레인 수

M = 디바이스 당 컨버터 수

F = 프레임 당 옥텟(octets) 수

S = 컨버터 하나를 기준으로 프레임 주기 당 전송된 프레임 당 샘플

예를 들어 FPGA 링크에 연결된 컨버터는 서로 호환되지 않는 서로 다른 구성으로 두 레인을 구성할 수 있다. 왼쪽에 있는 링크(LMFS = 2111)는 각 컨버터 샘플이 도착하면 양쪽 레인을 채우도록 구성했다. 오른쪽 링크(LMFS = 2221)는 한 번에 샘플 2개를 처리하며 하나의 샘플을 두 옥텟(Octet)에 할당한다(표 2).

JESD204B 표준에는 여러 옥텟과 레인 간 샘플을 나누는 옵션도 있다(표 3). 예를 들어 12비트 샘플 2개를 3개의 옥텟을 이용해 전송할 수 있다. 저해상도 데이터 컨버터를 사용할 때에는 이 기능이 매우 유용하나 ADC12J4000처럼 샘플링률이 높은 경우는 그렇지 않다.

ADC12J4000는 4Gsps에서 12비트를 출력한다. 여덟 개의 직렬 레인으로 한 프레임에 샘플 40개를 전송한 후 마지막 옥텟을 4개의 종단 비트로 채운다. LMFS 구성은 LMFS = 8885이다.

FPGA 펌웨어에서 사용자는 대개 L, F, K 매개변수를 지정한다. 수많은 컨버터가 있으므로 설계자는 JESD 블록 데이터 출력을 지정한 로직도 맵핑한다. 초기 레인 동기화 중에 JESD 링크 구성에 관한 핵심 매개변수(L, F, K, M, 하위 클래스 등)를 전송한 후 수신 디바이스 내부에 지정되어 있는 것으로 확인을 한다.

일반적으로 데이터 컨버터에는 여러 가지 패턴이 옵션으로 구현되어 있어(클록, 램프, 사용자 패턴), 초기 단계의 디버그 속도를 높여준다.

TI는 고속 ADC와 DAC로 알테라와 자일링스 FPGA를 모두 지원한다. 요청하면 예제 코드를 받아볼 수 있다. 단 코드를 컴파일 하기 위해서는 IP 라이선스를 받아야 한다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>