글 | *알베르토 비앙코(Alberto Bianco),**클라우디오 아드라그나(Claudio Adragna), ***쥬세빼 스카빠투라(Giuseppe Scappatura), ST

이 글은 트랜지션 모드 부스트 PFC의 COT(constant on time) 제어를 혁신적으로 향상시키는 데 초점을 맞추고 있다. 표준 COT, 개선된 COT(eCOT), 램프개선 COT(reCOT)를 비교하여 실제 구현을 통한 물리적 측정값을 보여준다. 이러한 측정을 통해 분석 내용과 함께 양호한 성능을 얻었음을 확인할 수 있을 것이다.

글 | *알베르토 비앙코(Alberto Bianco), IPC(Industrial Power Convergence), 시니어 스태프 엔지니어

**클라우디오 아드라그나(Claudio Adragna) 애플리케이션&시스템 아키텍처 디렉터 - 펠로우(Application & System Architecture Director - Fellow)

***쥬세빼 스카빠투라(Giuseppe Scappatura), HW 시니어 설계 엔지니어, ST마이크로일렉트로닉스

규정을 만족시키고 역률 및 왜곡을 개선하기 위해 여러 가지 역률 교정 기법이 연구돼 왔고[1], 이 중에 부스트 토폴로지가 가장 일반적으로 사용되고 있다. 과거 다양한 종류의 제어장치가 개발돼 왔는데[2], 전류 모드 제어장치와 전압 모드 제어장치로 분류할 수 있다. COT[3]는 파워 트랜지스터의 턴온 기간이 컨버터의 출력 전압만을 기반으로 제어되는 일반적인 제어 기법으로, 각 라인 사이클이 일어나는 동안에 천천히 변화하거나 일정하게 유지된다.

디지털 구현에서 온타임은 대개 루프 자체의 대역폭에 견줄만한 속도, 예컨대 입력 전압의 사이클 반(半)마다 갱신된다. 전형적인 COT 제어는 임계 동작 모드(critical conduction mode)[4]라고도 하는 트랜지션 모드(Transition Mode, TM)로 동작하는데, 이것은 연속(CCM) 및 비연속(DCM) 전도 모드 간의 경계에서 동작한다. TM은 고유 제로 전압 스위칭(Zero Voltage Switching) 기법에서의 높은 효율성을 특징으로 하는데, 한편으로는 리플 전류가 크기 때문에 커다란 EMI 필터를 필요로 한다.

이처럼 보다 높은 리플 전류 때문에 이들은 중간 정도 출력(300 W 미만)의 애플리케이션에서 선호되는 반면, CCM 제어는 보다 높은 전력(임계값 이상)의 애플리케이션에서 선호된다. 이 글에서는 세 부분에 걸쳐 표준 COT와 표준 COT의 단점을 극복하기 위한 방법, 그리고 입력 필터 콘덴서 전류를 보상하기 위한 방법에 대해 설명한다. 이 세 가지 구성의 성능은 75 W 및 230 V 그리고 THD 및 PF 면에서 최악의 조건인 입력 전압으로 동작하는 디지털 제어 200 W AC/DC를 이용하여 비교될 것이다.

표준 COT

표준 COT 알고리즘은 트랜지션 모드 PFC에 가장 많이 사용되는 제어 기법 중 하나다. COT 제어장치는 트랜지션 모드에서는 인덕터의 전류가 영에 가깝다는 사실을 이용한다.

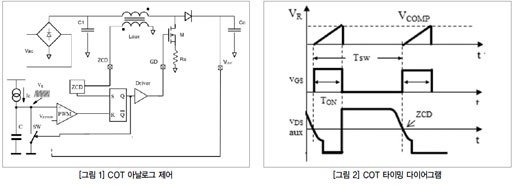

그림 1과 2는 표준 COT를 구현하는 블록 및 타이밍 다이어그램을 나타낸다. 파워 MOSFET게이트는 인덕터의 전류가 영(zero)이 될 때 열린다. 이는 인덕터와 MOS 및 다이오드의 기생 커패시턴스(parasitic capacitances) 간에 공진을 야기하므로, 이러한 상황은 대개 인덕터 보조 권선의 전압을 감지하여 인식한다. MOS는 톱니파 신호가 VCOMP 신호에 도달할 때 닫힌다. 그리고 나서 제어장치는 다음 번 ZCD를 기다리게 된다. 그림 1의 회로를 고려할 때 인덕터 전류의 피크 부분을 (1)로 나타낼 수 있다.

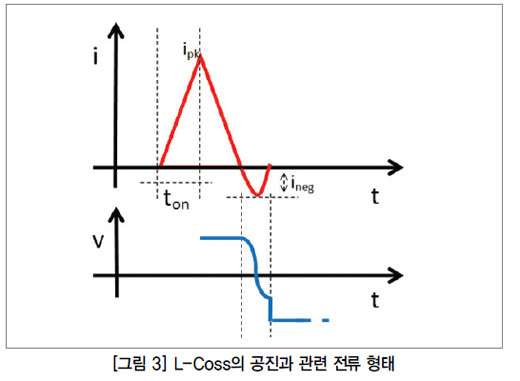

입력 전류 값은 삼각 인덕터 전류(triangle inductor current)의 대략 절반 정도로 볼 수 있다[5]. 등식 (2)에서 알 수 있듯이, 회로가 소모하는 AC 전압과 전류 사이에는 완벽한 선형 관계(linear relation)가 나타나는데, 이상적으로 완벽한 단위 역률을 제공하며 아무런 왜곡도 보이지 않는다. 유감스럽게도, 기생 성분(parasitic element)은 그림 3에서 볼 수 있듯이 인덕터 전류 형태에 네거티브 오프셋을 야기한다.

.jpg)

특히 ZCD에 도달할 경우 MOSFET의 아웃 커패시턴스가 Vout에서 충전되므로 턴온 시에 방전되어야만 한다. 이는 COSS와 인덕터 사이에 공진이 있으며(그림 3 참조) THD가 나빠짐을 의미한다[3, 4]. ineg 항은 Vin, L 및 COSS의 함수이다. 사실상 공진 시에는 손실이 없다고 가정하고, 그 에너지를 다음과 같이 살펴볼 수 있다:

.jpg)

단순화하기 위해 음의 전류를 대략 삼각형으로 보고, 입력 전류(즉, 인덕터 전류의 절반)를 다음과 같이 계산할 수 있다:

.jpg)

Vin을 (6)으로 간주할 경우, (5)의 첫 번째 항은 사인파 형태인 반면, ineg 항은 상수이다. 이는 사인파형이 완벽하지 못함을 의미하는 것으로, 고조파 왜곡 면에서 성능이 저하된다.

eCOT

음의 전류 보상을 위한 첫 번째 방법은 eCOT이다. 이 방법은 ineg 항을 없애기 위해 루프에 정전류를 추가할 것을 제시한다. 이 솔루션에서 온 펄스의 타이머는 인덕터의 전류가 사전 설정된 값인 iset에 도달한 뒤에만 시작된다.

.jpg)

![]()

그에 따른 피크 전류는 (7)과 같이 되며, 평균 전류는 이제 (8)과 같이 된다. iset 항은 기생 효과로 인한 비이상적 상태를 보상하기 위해 사용될 수 있다. 특히 iset이 ineg과 동일하도록 선택될 경우, 그에 따른 전류는 (9)와 같이 된다. 아날로그 구현 예제(그림 4 참조)는 COT에 대한 유사한 접근 방법을 보여주고 있다. 다만 전류 비교기(여기서는 ZCC로 명명된)에는 고정된 값이 추가돼 있다. 그림 5는 관련 타이밍 차트이다.

reCOT

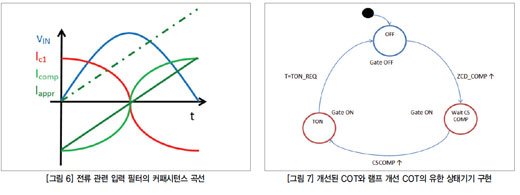

EMI를 제한하기 위해 PFC의 입력은 대개 다이오드 브리지와 필터(보다 정교한 π 필터나 간단한 콘덴서)로 구성된다. 두 경우 모두 커패시터가 레귤레이터의 입력 전류에 기여한다. 입력 라인 전압을 (9)로 간주하면, 커패시터 전류(그림 6의 적색 선 참조)는 (10)과 같다.

.jpg)

전압과 위상이 달라진 커패시터의 전류는 역률을 악화시킨다. 입력 커패시턴스 필터의 기여를 보상하기 위해 반대 전류(그림 6의 연두색 선)를 추가해야 한다. 그러나 추가된 유효 전류는 녹색 점선인데, 이는 PFC가 1사분면(I-V)에서 동작하며, 입력 커패시터에 전류를 공급할 수 없고, eCOT와 reCOT가 0 전류로부터 시작하여 합쳐지기 때문이다.

연두색 점선은 라인 사이클 시에 iset 값을 바꿔줌으로써 얻을 수 있다. 디지털 솔루션에서는 이를 라인 사이클을 따라 몇 단계씩, 예컨대 16단계씩 증분시킴으로써 달성할 수 있다. 따라서 램프의 생성에는 iset 값들을 계산하기 위해 라인 사이클을 따라 16회를 더 계산해줘야 한다. 하지만 계산 자체가 워낙 간단하기 때문에 그 연산 부하는 무시할 수 있을 정도다.

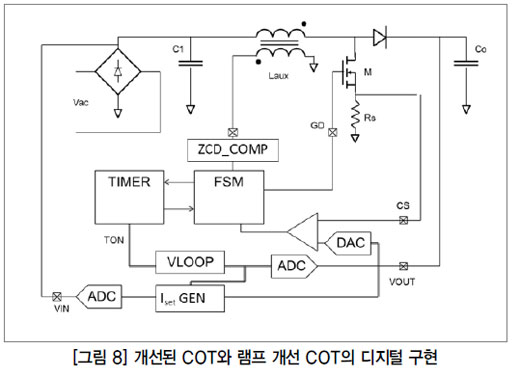

그림 7은 혁신적인 사건 중심 상태기기(SMED)에 의한 디지털 구현 방법을 보여준다[6]. OFF 상태에서 시작해서 ZCD가 발생할 경우(보조 날개의 전압이 0), 게이트가 열리며 전류 비교기가 임계값에 도달하기를 기다리게 된다. 이 마지막 선택은 eCOT(고정 임계값)나 혹은 임계값이 반주기 전압 라인에서 수정되는 reCOT를 결정하게 된다. 결국 유한 상태 기기(finite state machine, FSM)는 타이머가 필요한 온타임에 도달한 뒤에 OFF 상태로 발전하게 된다. 그림 8은 두 가지 향상된 방법의 디지털 구현 방법 전체를 보여준다.

Vin과 Vout은 디지털 방식의 값으로 샘플링 및 변환된다. Vout은 VLOOP과 Iset GEN 블록들에 대한 입력이다. 첫 번째 것은 제어장치의 핵심으로서 TON(타이머의 입력)을 생성하며, 두 번째 것은 CSCOMP를 위한 임계값을 생성한다. FSM의 경우, 임계값을 수정하거나(eCOT) 혹은 주기 중에 수정할 수 있다(reCOT). FSM 블록은 그림 7에서 설명한 FSM을 구현하는데, 이것은 CSCOMP, ZCD_COMP 및 TIMER 출력을 관찰하여 게이트의 구동을 관리한다. reCOT의 타이밍 다이어그램은 그림 5에서 본 다이어그램과 유사하다. 차이점은 iset 값으로서, 이것은 반주기 동안에 변화한다.

결과

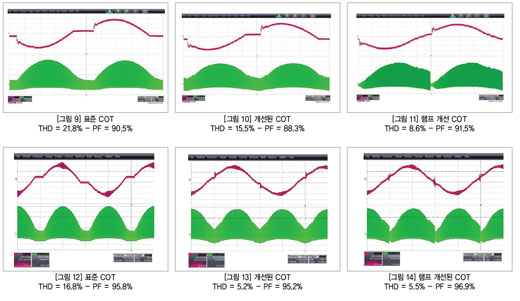

그림 9, 10 및 11은 230 V 입력 및 75 W에서의 PFC의 동작을 비교하는데, π 입력 필터가 각각 1 μF의 커패시터 두 개에 사용된다. 보라색 선은 입력 PFC 전류이며, 녹색선은 PFC 인덕터 전류이다.

그림 12, 13 및 14는 동일한 보드 상에서 다이오드 풀 브리지 이후의 입력 필터를 470 nF의 단일 커패시턴스로 변경했을 때의 동작을 비교한 것이다.

결론 및 향후 작업

eCOT는 인덕터 전류에 정전류를 추가함으로써 부스트 컨버터의 기생요소들을 보상해 주며, reCOT는 PFC의 입력 커패시턴스 필터를 보상해 주기 위해 인덕터 전류에 램프를 추가해 준다. π 입력 필터를 갖춘 보드는 표준 COT(21.8%)로부터 reCOT(8.6%)로 THD가 개선됨을 보여준다. 또한 표준 COT로부터 마지막 방법을 통해 PF 개선이 달성된다(90.5%로부터 91.5%로). 후자의 경우, eCOT는 PF 측면에서 악화된 결과를 얻는다.

커패시턴스만을 입력 필터로서 갖는 보드는 표준 COT(16.8%)로부터 eCOT (5.2%)로 THD가 개선됨을 보여주는 반면, reCOT는 5.5%의 THD를 보여준다.

또한 표준 COT로부터 마지막 방법으로의 PF 개선이 달성된다(95.8%로부터 96.9%로). 후자의 경우, eCOT는 PF의 면에서 악화된 결과를 얻는다. 이러한 결과들은 두 방법이 좋은 THD 및 PF 성능을 얻게 됨을 보여준다. 이 알고리즘의 연산 부하는 매우 낮아서 EMI 필터 설계를 간소화하고 π 필터에 보다 작은 인덕터를 사용할 수 있도록 해준다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>