글/ 알테라

첨단 FPGA는 최신 실리콘 제조 기술을 적용해 출시시간을 크게 단축했다. 하지만 이런 특성은 장점만 있는 것이 아니다. 이유는 FPGA 업체가 최종 고객이 첨단 디바이스를 설계·탑재하는 데 정확한 타이밍 모델을 제공하기 어렵기 때문이다. 이 글에서는 양산 FPGA를 이용하기에 앞서 최종 사용자가 FPGA 설계에 이용할 수 있도록 타이밍 모델을 제공하는 것에 대해 설명한다.

서론

첨단 FPGA를 사용하는 설계자는 실리콘이 생산되기 훨씬 전에 상세한 타이밍 특성이 필요하다. 하지만 FPGA는 첨단 프로세스 노드를 사용하고 고도의 구성 가능성을 특징으로 특성분석 작업이 매우 까다롭다. 따라서 FPGA 사용자의 요구를 충족하려면 양산 실리콘이 나오기 전, 여러 단계의 타이밍 모델을 제공해야 한다. FPGA 디바이스 개발 작업은 진행될수록 더 정확해진 타이밍 모델을 이용해 샘플 실리콘의 특성분석과 상관화를 할 수 있다. 또한 타이밍 모델을 이용하여 새로운 FPGA 디바이스 개발과 함께 디자인을 개발할 수 있다.

FPGA 고유의 타이밍 모델 과제

첨단 프로세스 노드는 프로세스 노드마다 실리콘으로 구현할 수 있는 물리적 한계를 끌어올리기 위해 많은 해결 과제가 발생한다. 또한 최첨단 프로세스 기술은 복잡성과 비용, 위험성이 지극히 높아 이 기술을 다루려는 IC 디자이너도 많지 않다.

투자비 회수 측면에서 보아도 대대적인 엔지니어링 시간을 투입하는 것은 비효율적이다. 하지만 FPGA 업체들은 비용이 조금 들더라도 디바이스 모델링 문제의 해결책을 찾는 것이 규모의 경제면에서 타당하다고 생각한다. 이런 해결 과제는 나노미터 스케일의 디바이스 물리적 특성과 FPGA 고유의 구성 가능성으로부터 비롯된 것이다.

첨단 실리콘 프로세스 노드로 인한 타이밍 모델 과제

첨단 극미세 제조 기술을 이용하면 회로 동작을 예측 및 모델링하기가 어렵다. 이전까지는 기존 세대 프로세스 노드의 실리콘 동작을 토대로 다음 프로세스 노드의 동작을 예측했었다. 하지만 새로운 프로세스 노드가 거듭될수록 물리적 효과들을 추론하기는 현실적으로 더 어려워지고 있다.

따라서 새로운 시뮬레이션 기법을 고안하고 실제 실리콘 샘플의 측정을 하며 시뮬레이션 결과에 따라 교정(calibration)이 필요하다. 알테라의 ‘FPGA 타이밍 모델을 이용한 실리콘 성능 보장(Guaran-teeing Silicon Performance with FPGA Timing Models)’에서는 오늘날 첨단 실리콘에 본질적으로 제기되는 해결 과제에 대해 논의하고 있다. 이러한 과제들로는 다음을 들 수 있다:

■ 온-다이 프로세스 변동성

■ 비대칭적인 N-채널 및 P-채널 트랜지스터 속도

■ Clock 불확실성 및 지터

■ 금속적 변동성

■ 수명 저하

■ 전역 변동성

■ 온칩 로컬 변동성

■ 신호 누화

■ 분산적 기생 RC wire 효과

■ 전력 분산 효과

실리콘 측정 vs. 회로 시뮬레이션의 특성분석 및 상관화

실리콘 디바이스가 제작되고 초기 실리콘을 이용해 측정하면 특성분석(characterization)을 계획해 샘플 제품을 측정할 수 있다. 이들 테스트를 통해 제작된 디바이스의 실제 속도를 계산하고 결과를 회로 시뮬레이션으로부터의 동작과 상관화한다. 시뮬레이션과 실제 측정 사이에 차이가 있으면 타이밍 모델을 교정함으로써 최종 사용자 타이밍 모델을 실제 실리콘 측정에 따라 조정한다.

특성분석 작업은 매우 복잡한 작업이다. 최근의 칩은 수십억 개의 트랜지스터를 포함해 모두를 낱낱이 테스트하기란 불가능하다. 따라서 특성분석 테스트는 프로세스와 전압, 온도(process, voltage, and temperature: PVT)의 변동 범위에 걸쳐 디바이스 상의 주요 요소들의 실제적인 동작 특성을 판단할 수 있도록 신중하게 설계해야 한다.

FPGA는 사용자에게 거의 ‘무한정한 프로그램의 가능성’이란 특성으로 각인되어 이미 복잡한 특성분석 작업을 더 복잡하게 할 수 있다.

FPGA는 타이밍, 로딩, 전원 요구가 각기 다른 다양한 요소를 포함한다:

■ 내부 메모리

■ 트랜시버

■ 표준 셀 블록

■ 시스템-온-칩 기능(임베디드 프로

세서 등)

■ 범용 로직 엘리먼트(LE)

■ 로컬 및 전역 routing 요소

이러한 모든 요소가 다양한 구성으로 사용자 디자인에 포함되고 상호작용해 낱낱이 열거하고 테스트하기란 어렵다. 따라서 현장에서 디바이스를 구성할 수 있는 모든 구성 방식을 분석에 반영하도록 특성분석 계획을 신중하게 작성하고 시행해야 한다. 지정된 속도 등급으로 디바이스 타이밍을 충족하도록 하기 위해서는 전체적인 프로세스, 동작 전압, 동작 온도 변동 범위에 걸쳐 디바이스의 특성을 측정해야 한다.

이런 차이를 타이밍 모델로 반영하고 교정할 때까지 디바이스 특성분석은 계속된다. 최종적으로 TimeQuest Timing Analyzer에 이용되는 타이밍 엔진과 Quartus짋 II 소프트웨어의 fitter의 place-and-route 툴로 인코딩한다.

모든 동작 조건으로 타이밍 분석

FPGA는 일련의 범위 온도, 전원 전압, 제조 프로세스 변동에 걸쳐 동작해야 한다. 그뿐만 아니라 특정한 속도 등급이라 하더라도 디바이스마다 변동적일 수 있어 모든 변수가 각기 다른 방식으로 디바이스 타이밍에 영향을 미친다. 28 nm 및 이후의 첨단 프로세스 노드에서는 온도 역전(temperature inversion) 같은 나노미터 스케일 효과로 타이밍 지연이 온도나 전압과 직접적인 상관관계로 변동적이지 않을 수 있다. 따라서 최악과 최선의 타이밍 상황을 모두 포괄적으로 반영하기 위해 다중의 동작 조건에 걸쳐서 타이밍을 분석해야 한다.

알테라는 4개의 극단 동작 조건으로 타이밍 모델을 제공한다. 모든 동작 조건으로 타이밍 분석을 함으로써 온도와 전압, 제조 프로세스 변동에 걸쳐 적절히 동작할 것을 보장한다.

FPGA 타이밍 분석 정확성을 위해서는 회로 시뮬레이션 필요

만약 RTL 디자이너가 프로그램할 때까지 디바이스의 로직 토폴로지를 알 수 없다면 어떻게 정확한 타이밍 정보를 디바이스에 제공할 수 있을까?

알테라의 TimeQuest Timing Analyzer는 두 가지 다른 기법을 이용해 사용자 디자인의 분석을 한다. 정적 타이밍 지연 데이터베이스와 커스텀 회로 시뮬레이터가 그것이다.

지연 데이터베이스는 로직이나 하드 IP(intellectual property) 블록과 같이 구성 가능성이 제한적이며 잘 정의된 요소들에 사용된다. 회로 시뮬레이터는 사용자 디자인의 특정한 구성을 반영해 상세한 시뮬레이션을 할 수 있다. 회로 시뮬레이션은 고도로 구성 가능성이 높은 routing 패브릭으로 정적 지연 수치를 이용해서 정확하게 모델링할 수 없는 routing 인터커넥트 지연을 다룰 수 있다.

또한 용량성 부하(capacitive loading) 효과와 선택한 금속 routing 트랙의 지연, 회로에 적용된 입력 파형, 기타 효과를 반영할 수 있다. 하지만 상세한 SPICE 회로 시뮬레이션은 전체적인 최종 사용자 디자인에 이용하기는 실용적이지 않다. Quartus II 소프트웨어 회로 시뮬레이터는 FPGA 아키텍처에 최적화되어 범용 SPICE 시뮬레이션보다는 수십 배 더 빠르게 실행된다.

FPGA 개발 프로세스에 따른 타이밍 모델 제공

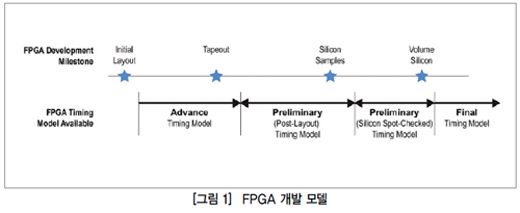

사용자 타이밍 모델의 이용 가능한 시점을 이해하기 위해서는 FPGA 개발 프로세스와 이용할 수 있는 모델을 연관해서 살펴보는 것이 유용할 것이다(그림 1).

초기 레이아웃(Initial Layout)

초기 레이아웃 단계에서는 새로운 디바이스의 아키텍처가 최종적으로 마무리된다. 내부 구성요소(routing, 범용 로직, 메모리, 트랜시버 등이 차지하는 다이 비중)들을 어떻게 혼합할 것인가를 정하고 플로어플랜을 작성한다. 이때 상세한 레이아웃은 작성되지 않는다. 하지만 EDA 툴로부터 블록과 블록 사이의 지연을 상당한 정도까지 예측하고 추출할 수 있다. 이 단계에서는 상세한 타이밍 시뮬레이션은 이뤄지지 않으며 완료되면 디자인에 대해 상세한 레이아웃과 시뮬레이션을 할 수 있다. 또한 선행적(Advance) 타이밍 모델을 이용할 수 있다.

테잎아웃(Tapeout)

상세한 레이아웃이 이뤄지고 회로 시뮬레이션이 완료된다. 파운드리와 협력해서 물리적 디바이스 효과에 대한 최신 정보를 포함하는 레이아웃 작성 후, 시뮬레이션으로부터 회로 지연을 도출할 수 있다. 이 설계 단계가 완료되면 EDA 툴로부터 최종적인 파라미터 추출이 가능하며 레이아웃과 시뮬레이션이 파운드리로 테잎아웃을 제공할 수 있을 정도로 상세한 수준이 된다. 이 단계가 완료되면 예비적(Preliminary) 레이아웃 후 타이밍 모델을 이용할 수 있다.

스팟 체크 실리콘(Spot-Checked Silicon)

파운드리에서 샘플 디바이스를 제작하면 이들 샘플 디바이스를 상관화 계획에 따라 스팟 체크를 하고 이 결과를 원래의 시뮬레이션 결과와 상관화한다. 그리고 어떤 차이가 있으면 그 원인을 추적한다. 이 단계에서는 실리콘을 계속해서 스팟 체크를 해 가는 것에 따라 타이밍 모델을 업데이트한다. 이 단계가 완료되면 예비적(Preliminary) 실리콘 스팟 체크 타이밍 모델을 이용할 수 있다.

양산 실리콘(Volume Silicon)

마침내 파운드리에서 디바이스 양산을 착수하고 대량의 샘플 실리콘으로 타이밍 모델과 상관화를 할 수 있다. 특성분석 시에 의도하는 여러 가지 목표는 프로세스 변동 코너에 대해 동작을 분석할 수 있도록 통계적으로 의미 있는 샘플 크기가 필요하다. 이를 위해 양산 측정은 중대 전환점이라고 할 수 있다. 이 단계에서는 특성분석 측정에 대해 높은 신뢰도를 달성할 수 있으며 상관화 작업이 완료된다. 이 단계가 완료되면 최종적인 타이밍 모델을 이용할 수 있다.

다양한 타이밍 모델을 이용할 때의 우수 관행

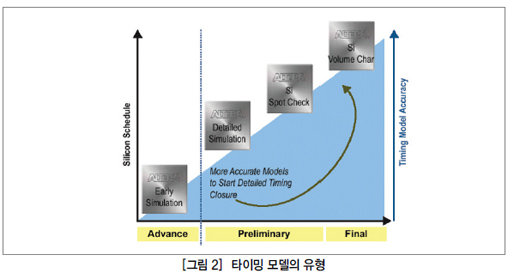

알테라는 최종 사용자가 아직 나오지 않은 FPGA로 시스템을 설계할 수 있도록 FPGA 개발 작업의 각각 단계에 따라 점진적으로 더 정확해지는 타이밍 모델을 제공한다(그림 2).

선행적(Advance) 타이밍 모델

이 단계의 타이밍 모델은 레이아웃 전, 정보를 바탕으로 초기의 지연 예측과 엔지니어링 예측을 포함한다. 이러한 예측들은 레이아웃과 시뮬레이션이 완료된 후에 변경될 수 있다. 따라서 선행적 타이밍 모델은 절대적 지연 수치가 변경될 수 있어 시스템 아키텍처 검토 용도로만 사용하고 상세한 타이밍 종결 작업에는 사용하지 않아야 한다. 선행적 타이밍 모델은 다음 예측들과 함께 사용해야 한다:

■ 시스템 지연시간 평가

■ 기초적 타이밍 평가(파이프라인 예산)

■ I/O 전송 전략(데이터패스 폭,

버스트 폭, I/O 표준 절충)

☞ 선행적(Advance) 타이밍 모델은 타이밍 종결 작업에는 사용하지 않아야 한다. 따라서 이 단계의 타이밍 모델은 FPGA 프로그래밍 파일(.pof) 출력이 지원되지 않는다.

예비적(Preliminary) 모델

예비적(Preliminary) 모델은 특성분석과 상관화 작업을 아직 더 해야 하므로 변경될 수 있는 타이밍 데이터를 포함한다. 이들 모델은 상세한 시뮬레이션 결과를 토대로 초기의 스팟 체크 생산 샘플링에서부터 양산 샘플링에 이르기까지 특성분석 작업을 계속해 나감으로써 얻어지는 실리콘 측정으로 교정하므로 선행적 모델보다 좀 더 정확하다.

예비적(Preliminary) 레이아웃 후 타이밍 모델

‘예비적(Preliminary)’이라고 표시된 앞의 모델은 최종적인 디바이스 레이아웃의 회로 시뮬레이션으로부터 추출한 지연을 포함한다. 이들 지연은 구현 FPGA의 테잎아웃 표현으로부터 추출된 것이다. 하지만 초기의 예비적 모델들은 물리적 실리콘으로부터 측정한 결과를 포함하지 않아 시스템 디자인 사인오프에는 이용하지 않아야 한다. 다만 초기 타이밍 종결 작업을 시작할 수 있다.

예비적(Preliminary) 실리콘 스팟 체크 타이밍 모델

후반의 예비적 모델들은 실제의 초기 샘플 실리콘 측정에 대해 상관화하는 타이밍 정보를 포함한다. 이 단계에서는 양산 특성분석 작업은 아직 완료되지 않았다. 알테라는 특성분석 작업을 계속해서 진행하고 이에 따른 예비적 모델들을 업데이트하며 실리콘 결과를 타이밍 모델과 상관화하여 Quartus II 소프트웨어 툴에 적용한다. 예비적 타이밍 모델들은 다음 예측들과 함께 이용해야 한다:

■ 점차 향상되는 예비적(Preliminary) 모델들을 이용할 수 있게 됨에 따라 좀 더 정확한 결과를 이용해서 타이밍 종결 작업을 시작하고 계속할 수 있다.

■ 랩에서 시스템 bring up에 이용하도록 초기 평가 고객들에게 제공되는 프로그래밍 파일(.pof) 지원

☞ 디자이너들은 제품을 내놓기에 앞서 또다시 새로운 소프트웨어 빌드를 이용할 수 있다는 점을 예상하고 있어야 한다.

최종적(Final) 모델

이 단계에서는 실리콘을 충분한 규모로 특성분석을 하고 타이밍 동작을 포괄적으로 분석한다. 이들 모델은 양산 시스템에 사용할 수 있다.

■ 최종적인 타이밍 종결

■ 고객 양산 시스템에 이용하기에 적합

결론

FPGA를 이용해서 설계하는 시스템 디자이너들은 시장의 치열한 경쟁에 직면해서 디바이스를 물리적으로 이용할 수 있게 되었을 때 곧바로 시스템을 내놓을 수 있어야 한다. 따라서 설계는 FPGA를 물리적으로 이용할 수 있기 훨씬 전부터 시작해야 한다.

견고한 시스템 디자인을 달성하기 위해서는 FPGA의 정확한 타이밍 모델을 이용해야 한다. 하지만 첨단 FPGA는 물리적으로 모델링하기가 매우 까다로우며 이 때문에 양산 실리콘 특성분석을 마치기 전까지는 최종적인 타이밍 모델을 이용할 수가 없다. 그뿐만 아니라 오늘날 하이엔드 FPGA는 고도의 구성 가능성으로 복잡한 특성분석 작업을 더욱더 복잡하게 한다.

알테라는 실리콘을 이용할 수 있기 훨씬 앞서서 고객이 자사 시스템으로 FPGA를 설계할 수 있도록 지원하고 있다. 최종적으로는 포괄적으로 상관화된 타이밍 모델에 이르기까지 각기 단계마다 앞서 개발 단계에서 얻어진 좀 더 정확한 타이밍 정보를 반영해 FPGA 개발 프로세스에 따라서 여러 단계에 걸쳐서 타이밍 모델을 제공함으로써 가능한 것이다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>