ISSCC 2020 채택된 198편의 최신 논문, 한국은 35편 채택

제67회 국제고체회로학회(International Solid-State Circuits Conference, 이하 ISSCC)가 2월 16일~2월 20일까지 5일간 미국 샌프란시스코(메리어트 호텔)에서 열린다.

ISSCC는 IEEE 반도체 집적회로 시스템 및 시스템집적 분야 학회 중 가장 권위있는 학회로 1954년에 설립되어 고체회로 및 SoC 설계 분야의 올림픽으로 불린다.

.jpg)

IEDM(국제전자소자회의)와 함께 반도체 및 고체회로분야의 양대 산맥으로 IEEE SSCS(Solid-State Circuit Society)의 지원을 받는다. 25개국 3,000여 명의 학자들과 연구원들이 참여하는 ISSCC는 연구성과 및 정보를 교환하고 미래의 반도체산업과 기술을 논의하는 컨퍼런스로 참석자의 60% 이상이 산업 분야 소속일 만큼 실용성이 강한 연구 발표 행사이다.

이번 ISSCC 2020(

http://www.isscc.org)은 “AI 시대를 여는 집적회로(Integrated Circuits Powering the AI ERA)”라는 주제로 큐비트, 3D integrated silicon photonics 등의 새로운 디바이스 기술, 인공지능 및 기계학습과 같은 새로운 시스템 구현방법, IoT, 센서, 자율주행, 5G통신, THz 등 새로운 첨단반도체 회로 기술을 소개한다.

ISSCC의 관계자는 “반도체회로 및 시스템의 끊임없는 발전은 우리의 일상생활에 큰 영향을 미치고 있으며 우리가 일하는 방식, 소통하는 방식, 사회생활의 방식도 변화시킨다”며, “지난 수십 년간 무어의 법칙(Moore’s Law) 예측대로 반도체 회로 기술은 엄청난 속도로 발전해왔으나, 최근 들어 새로운 기술적 및 경제적 난관을 대면하고 있다. 인류의 역사가 도전과 응전의 기록이듯이, 반도체회로를 연구하는 각계 각국의 연구자들은 이러한 난관을 극복하려는 새로운 기술들을 부단히 연구하고 있다”고 밝혔다.

다음은 주요 기술 분과별로 채택된 주요 논문 내용이다.

메모리 분과

메모리 기술 분과는 총3개 세션에서 16편의 논문이 발표된다. 아시아 14편(한국논문 7편 포함), 북미 2편(Industry 10편, Academy 6편) 등이다.

세션13: Non-Volatile Memories(2/18, 화) 5편 모두 아시아 논문(한국 2편)이며 세션15: SRAM & Compute-in-Memory(2/18, 화)는 아시아 논문 4편, 북미 1편이다. 세션 22(DRAM)는 아시아 논문 5편(한국 5편), 북미 1편이다.

튜토리얼(2/16, 일)은 인텔(Fatih Hamzaoglu)에서 “Basics of Nonvolatile Memories: MRAM, RRAM, and PRAM”을 주제로 발표한다.

하이라이트 논문

Non-Volatile Memories의 Performance 향상

[13.1] 1Tb 4-bit/cell (QLC) 5th generation VNAND of 1.2Gb/s interface [삼성전자]

[13.2] 1Tb 4-bit/cell (QLC) 3D-Flash of 30MB/s program throughput [SK하이닉스]

[13.5] A 128Gb 1bit/cell 96-Word-Line-Layer 3D Flash Memory to Improve Random Read Latency with tPROG=75us and tR=4us [Kioxia, Western Digital]

[13.3] A 22nm 32Mb Embedded STT-MRAM with 10ns Read Speed, 1 Million Cycle Write Endurance, 10 Yrs

Retention@150°C [TSMC]

SRAM & Compute-in-Memory : 5nm 공정 기술의 SRAM 및 CIM

[15.1] A 5nm 135Mb SRAM in EUV and High Mobility Channel FinFET Technology with Metal Coupling and Charge Sharing Write-Assist Circuitry Schemes for High Density and Low VMIN Applications[TSMC]

[15.2] 6T SRAM based 8b-input x8b weight CIM for both forward and backward propagation [National Tsing Hua Univ.]

HBM2E 메모리 대역폭 향상

[22.1]A 1.1V 16GB 640GB/s HBM2E DRAM with a Data Bus Window Extension Technique and a Synergetic On-Die ECC Scheme [삼성전자]

[22.3] A 128Gb 8-High 512GB/s HBM2E DRAM with a Pseudo Quarter Bank Structure, Power Dispersion and an Instruction-based at-Speed PMBIST [SK하이닉스]

LPDDR5 대역폭 향상

[22.2] An 8.5Gb/s/pin 12Gb LPDDR5 SDRAM with Hybrid Bank Architecture, Skew-Tolerant Scheme, Low-Power Scheme, and Speed-Boosting Techniques in 2nd generation of 10nm DRAM Process [삼성전자]

High-Speed Interfaces

[22.4] A 32Gb/s Digital-Intensive Single-Ended PAM-4Transceiver for High-Speed Memory Interfaces Featuring a 2-Tap Time-Based Decision Feedback Equalizer and an In-Situ Channel Loss Monitor [Univ. of Minnesota]

Technology Directions 분과

TD(Technology Directions) 분과는 총 4개 세션에서 16편의 논문이 발표(50편 제출, 채택률32%)한다.

지역별로는 아시아(7편), 북미(6편), 유럽(3편) 순이며 산학 부분별로는 대학교(14편), 연구소(1편), 기업(1편) 순이다.

주요 하이라이트 논문은 다음과 같다.

SESSION 19(CRYO-CMOS for Quantum Technologies) 의 논문은 양자 컴퓨팅을 위한 극저온 CMOS 반도체집적회로 및 시스템 기술을 다루며 유럽지역이 강세(3/3편)를 나타냈다.

[19.1] A Scalable Cryo-CMOS 2-to-20GHz Digitally-Intensive Controller for 4x32 Frequency Multiplexed Spin Qubits/Transmons in 22nm FinFET Technology for Quantum Computers 델프트 대학교는 인텔과 협업하여 22nm FinFET 공정을 사용하여 세계최초로 4×32 스핀큐비트 및 초전도 큐비트를 2~20GHz로 제어할 수 있는 극저온 반도체 칩을 발표한다.

SESSION 17: Low-Power Circuits for IoT & Health

IoT와 Health 응용은 지속적인 동작이 필수이며 반도체 센서나 송수신기의 전력소모가 매우 중요하다. 4편 중 아시아 지역 논문 2편 발표된다(삼성전자 1편, 북경대학교 1편).

[20.3] A 4.0×3.7×1.0mm3MEMS-CMOS Integrated E-Nose with embedded 4 Gas Sensors, a Temperature Sensor, and a Relative Humidity Sensor

삼성전자는 공기질 관리용 초소형 가스센서를 발표한다. mm 스케일의 반도체칩에 캐미컬 센싱이 가능한 MEMS 공진기 6대를 탑재하여 ppm 농도의 가스 4종 및 온/습도 변화를 동시에 감지할 수 있는 복합 센서를 구현하였다.

SESSION 33: Non-Volatile Devices for Future Architectures

저전력 및 고속데이터 병렬처리는 AI응용에 매우 중요하다. ReRAM 등 비휘발성 메모리 기반의 Computation-in-Memory 구조는 면적 및 에너지 효율성이 뛰어나다.

3편 중 아시아 지역논문은 2편이 발표된다(오사카대학교 1편, 칭화대학교 1편).

[33.3]Via-Switch FPGA: 65nm CMOS Implementation and Architecture Extension for AI Applications

오사카 대학교에서 발표하는 65nm공정의 via-switch FPGA는 기존의 atom-switch FPGA 대비 61.4%, SRAM FPGA 대비 91.7% 면적효율이 우수하다.

SESSION 33: Biomedical Sensing, Stimulation & Harvesting

웨어러블 및 삽입형 장치를 위한 다양한 바이오메디컬시스템(암치료를 위한 초소형 선량계, 1225채널 인공 시각장치) 및 인체 통신을 활용한 전력전송 혹은 뇌파 측정시스템 소개한다.

6편 중 아시아 논문은 3편(싱가포르 국립대학교)이다.

.jpg)

DAS 분과

DAS(Digital Architecture & Systems)분과는 총3개 세션에서 14편 논문을 발표(총 제출 논문수: 40편)한다.

극동이 5편(한국 2, 대만 3)이며 북미는 7편, 유럽은 2편이다. 이 밖에 기업체(10편), 연구기관(2편), 대학(2편) 순이다.

SESSION 2: Processors

A 7nm High-Performance and Energy-Efficient Mobile Application Processor with Tri-Cluster CPUs and a Sparsity-Aware NPU (삼성전자)

스마트폰을 위한 7nm 공정의 고성능 AP-SOC를 소개한다. 3-cluster의 CPU와 고효율 NPU를 구현하였고, HW auto-clock-gating 기술을 활용하여 높은 에너지 효율을 달성했다.

Domain-Specific Processors

A Fully Integrate Genetic Variant Discovery SoC for Next-Generation Sequencing (National Taiwan University)

유전자 변이 발견을 위한 전용 SOC칩을 소개한다. 기존 GPU를 활용한 SW구현에 비해 월등한 에너지 효율 향상을 달성한다.

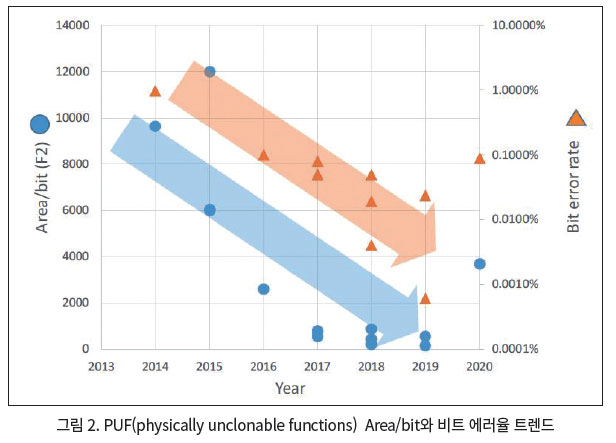

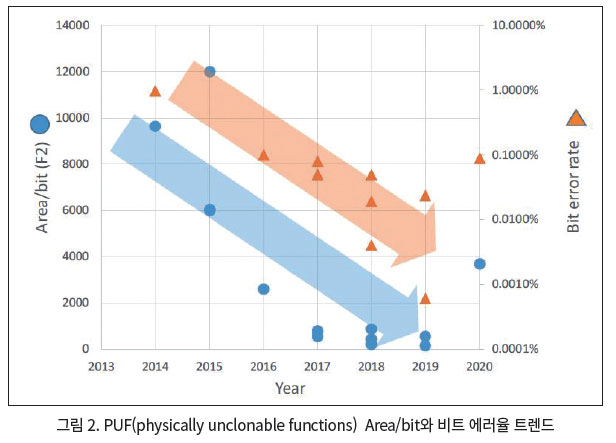

IoT and Security

Physically Unclonable Function in 28nm FDSOI technology achieving high reliability for AEC-Q100 Grade 1 and ISO26262 ASIL-B (삼성전자)

28nm FDSOI 공정으로 구현된 고신뢰성의 PUF (물리적 복제불가능 함수)회로를 소개한다. AEC-Q100 1 등급과 전장용 ISO26262 ASIL-B 안전 규격을 만족하며, 우수한 정확도를 달성한다.

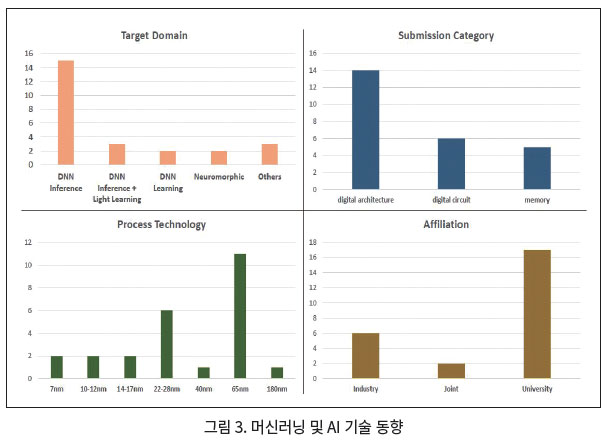

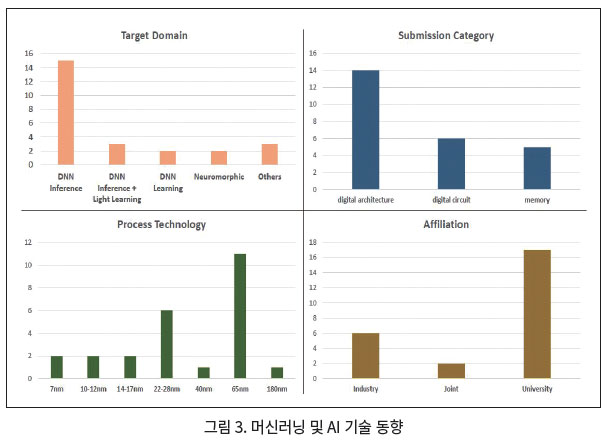

Machine Learning & AI 분과

머신러닝 & AI (Machine Learning & AI) 기술 분과는 High Performance Machine Learning(4)과 Low Power Machine Learning(3) 등 총2개 세션으로 구성된다. 제출 논문 수는 각각 25편과 7편이다.

한국 논문은 KAIST의 “GANPU: a32.4mm2energy-efficient (135TFLOPS/W) DNN training processor in 65nm technology”이다.

Digital Circuits 분과

디지털 회로(Digital Circuits)은 총2개 세션에서 12편의 논문이 발표된다.

극동에서 5편(한국1, 중국2, 싱가포르1, 대만1), 북미에서 7편이 나왔으며 분야별로는 산업계에서 3편, 대학에서 9편이 채택됐다. 이처럼 디지털 회로 기술분과는 학계가 강세를 보였다.

내용을 보면 디지털 LDO, MDLL, 디지털 PLL, Flip-Flop, 다양한 애플리케이션(Neuromorphic chip, Annealing processor 등)을 위한 다양한 디지털 회로에 관련된 논문들이 제출되었다.

크게 클럭과 파워에 관련된 논문들을 발표하는 세션과 시스템 관련 회로들을 발표하는 세션으로으로 분리하여 구성하였다.

[

Session 25] Digital Power Delivery & Clocking Circuits

_ Digital LDO, Fractional-N MDLL, PLL, Flip-Flop, NTV(Near Threshold Voltage) NOC with error detection and correction 등의 다양한 디지털 회로들이 제안됐다.

_ Synthesizable Digital LDO 논문이 다수를 차지했다.

_ Full-customized 설계 기법에 머무르지 않고, 좀더 빠르게 설계 가능한 Fully Synthesizable이 가능한 디지털 회로를 제안하는 논문이 계속 늘어나고 있다. 기존 기술대비 전력과 가격 면에서의 효율을 지속적으로 보여주고 있다.

_ 산업분야 논문들은 특이하게도 모두 인텔(Intel)사의 논문으로 모두 10nm 공정을 사용하고 있으며, 산업계에서도 디지털 회로의 비중을 계속 올려가는 추세임을 증명하였다.

[Session 31] Digital Circuit Techniques for Emerging Application

_ Edge Robotics에 응용 가능한 Spiking Neural Network에 기반한 Neuromorphic 칩에 적용 가능한 NeuroSLAM이라는 SLAM(Simultaneous localization and mapping) 알고리즘을 가속하는 회로를 제안한다. SLAM은 로봇공학에서 주로 사용하는 개념으로 이동하면서 동시에 현재의 위치를 추정하고 주변을 탐색하는 문제를 다룬다.

_ Compute In Memory(CIM) Spin 기술을 이용하는 Scalable한 디지털 CMOS annealing 프로세서 관련 논문.

_ 2D PE array based chip에 사용 가능한 효율적인 Clock Chain Techniques 관련 논문.

_ 디지털 회로기술이 power delivery, 클럭 관련 회로에 국한하지 않고 더 다양한 애플리케이션에 적용 가능한 시스템 형태로 확대된 논문들이 다수 제출됐다.

_ 3건 모두 학교에서 제출한 논문으로, 빅 시스템(big system)을 주제로 시스템 관점에서 유용한 회로를 제안하고 검증하였다는 것이 주목할 만하다.

IMMD 분과

IMMD(Imagers, MEMS, Medical and Displays) 기술 분과는 총3개 세션에서 23편의 논문이 발표된다(총 제출 논문수: 70편).

이 분과는 특히 극동 지역이 강세를 나타내어 극동 14편(한국 6편), 북민 7편, 유럽 2편이 채택되었다. FE 논문 중 43%은 한국 논문으로 꾸준한 편수를 유지하고 있다. (편수 유지: 6편→6편/비율 감소: 60%→43%). 이미지 센서 분야의 총 10편 논문에서 3편을 점유할 정도로 한국이 강세를 나타내고 있다.

Session 5 주요 논문

[5.1] A 240x192-Pix 10-FPS 70klux 225m-Range Automotive LiDAR SoC using a -40ch 0.0036mm2 Voltage/Time- Dual-Data-Converter-based AFE (Toshiba)

매우 민감한 SiPM을 사용하여 빛이 반사되어 돌아오는 시간과 파형을 감지하여 정밀하게 디지털 값으로 변환함으로써 최대 225미터의 거리를 높은 각도 분해능으로 추출하는 스캐닝 LiDAR이다.

[5.6] A 1/2.65-inch 44Mpixel CMOS Image Sensor with 0.7um-pixels fabricated by advanced full-depth deep-trench isolation technology(Samsung)

전체 깊이 트랜치 분리, 도핑 폴리실리콘 증착 등의 최신공정기술을 최대한 활용하여 세계 최초로 0.7um 픽셀을 구현하였다

[5.6] A 132dB Single-Exposure Dynamic Range, CMOS image sensor with high-temperature tolerance (Sony)

서로 다른 크기의 두 가지 포토다이오드와 커패시터를 픽셀 내에 집적하고 리셋 노이즈를 저감시켜 높은 온도에서도 화질 열화를 방지하는 HDR 센서이다.

Session 26 주요 논문

[26.1] A 4.5mm2 Multi-Modal biosensing SoC for PPG, ECG, BIOZ and GSR Acquisition in Consumer Wearable Devices (Mediatek)

PPG 측정시 빛의 입력 범위를 넓히고 두 개의 전극에서 ECG 측정이 가능하며 GSR, BIOZ까지 동시에 측정할 수 있는 웨어러블 SoC이다.

[26.2] A Neuromorphic Multiplierless Bit-Serial Weight-Memory-Optimized 1024-tree Brain State Classifier and Neuromodulation SoC with an 8-Channel Noise-Shaping SAR ADC Array (University of Toronto)

지수함수적으로 신호가 감소하는 메모리 1024개를 트리구조로 구성하여 뇌신경신호를 효율적으로 분류해내는 뉴로모픽 SoC이다.

[26.6] A 6.5μW 10kHz-BW 80.4dB-SNDR Continuous-Time ΔΣ Modulator with Gm-input and 300mVpp Linear Input Range for Closed-loop Neural Recording (Yonsei University)

기존에 비해 높은 주파수인 10kHz의 뇌신경 신호를 300mVpp까지 왜곡없이 측정할 수 있는 연속시간 델타 시그마 모듈레이터이다.

[28.3] A 5.2Mpixel 88.4dB-DR 12-inch CMOS X-ray Detector with 16b Column-Parallel Continuous-Time ΔΣ ADCs (Yonsei University)

169개의 sub-chip들을 스티칭 기술로 웨이퍼상에서 연결하여 12인치 크기(20.7cm× 20.7cm)의 엑스레이 센서를 구현한다.

면적이 작고 에너지 효율이 높은 3차연속 시간 델타 시그마 모듈레이터를 매 칼럼마다 집적하여 16b 디지털 엑스레이 사진을 30fps로 연속 촬영이 가능하다.

IMMD: 한국 논문 소개

Session5: Imagers and ToFSensors

[5.4] A Dynamic Pseudo4-tap CMOS Time-of-Flight Image Sensor with Motion Artifact Suppression and Background Light Cancelling over 120 klx (성균관대,UNIST, 지안)

[5.5] A 2.1e-Temporal Noise and -105dB Parasitic Light Sensitivity Backside-illuminated 2.3um-Pixel Voltage-Domain Global Shutter CMOS Image Sensor using High Capacity Concave-type Capacitor Technology(삼성전자)

[5.6] A 1/2.65-inch 44Mpixel CMOS Image Sensor with 0.7umpixels fabricated by advanced deeptrench isolation technology (삼성전자)

Session26: Biomedical Innovations

[26.6] A 6.5μW 10kHz-BW 80.4dB-SNDR Continuous-Time ΔΣ Modulator with Gm-input and 300mVppLinear Input Range for Closed-loop Neural Recording(연세대, UST, 카톨릭대)

Session28: User Interaction & Diagnostic technologies

[28.2] A 51dB-SNR 120Hz scan-rate 32x18 Segmented-VCOM LCD In-cell Touch-Display Driver IC with 96-channel Compact Shunt-sensing Self-capacitance Analog Front-end (센트론)

[28.3] A 5.2Mpixel 88.4dB-DR 12-inch CMOS X-ray Detector with 16b Column-Parallel Continuous-Time ΔΣ ADCs( 연세대,Rayence)

.jpg)

아날로그 분과

아날로그 기술 분과는 총2개 세션에서 16편의 논문이 발표된다. 총57편의 논문이 제출되어 이중 16편이 채택되었다(채택율 28.1%). 극동 지역이 5편(한국1, 중국1, 싱가포르1, 대만2), 북미가 5편, 유럽이 6편이다. 산업 분야(4편)와 학교 분야(12편)에서 아카데미가 강세를 나타냈다.

[

Session 3] Analog Techniques -I

_ BAW Oscillator가 production level의 결과를 최초로 보고.

_ 온도 보상 기능이 내장된 RC oscillator 다수의 논문으로 소개됨.

_ 내장형 온도센서의 power efficiency가 지속적으로 개선.

[Session 23] Analog Techniques -II

_ Lidar, ultrasound probe, coulomb counter, audio, bio amplifier 등 다양한 애플리케이션에 적용이 가능한 회로기법이 소개된다.

_ 기존의 성능을 한단계 업그레이드하기 위한 다양한 기법이 제시됨.

[3.1] An Integrated BAW Oscillator with <±30ppm Frequency Stability over Temperature, Package Stress, and Aging Suitable for High-volume Production (Texas Instrument)

_ Texas Instrument에서 BAW를 이용한 최초의 mass production 가능한 MEMS Oscillator 소개.

_ Crystal-less operation을 위해서 power와 cost를 모두 만족시키는 결과.

_ 온도와 stress 등 다양한 환경변화에도 30ppm의 frequency stability를 보장하는 MEMS 기반의 오실레이터 구현.

[23.1] “A 4GS/s 80dB DR Current-Domain Analog Frontend for Phase-Coded Pulse-Compression Direct Time-of-Flight Automotive Lidar”(Robert Bosch)

_ 로버트 보쉬에서 차량용 Lidar를 위해 Peak power를 줄이는 Pulse-coded 기법을 소개.

_ 수십 mW의 laser power만으로 60m 이상의 거리 측정이 가능함을 보임.

[23.8] “A 41μW 16MS/s 99.2dBSFDR Capacitively Degenerated Dynamic Amplifier with Nonlinear Slope Factor Compensation” (Yonsei University)

_ 연세대에서 선형성이 매우 높은 dynamic amplifier를 소개.

_ 새로운 linearization 기법을 제안하여,16MS/s의 속도에서 41μW 전력 소모로 매우 높은99.2dB의 SFDR을 달성한다.

파워 관리 분과

파워 관리(Power Management) 기술 분과는 3개의 세션에서 총21편의 논문이 발표된다.

이 3개의 세션은 △Session 11:DC-DC Converters(4 FE / 3 NA/ 1 EU), △Session 18: GaN & Isolated Power Conversion (5 FE / 2 NA / 1 EU), △Session 32:Power Management Techniques(2 FE / 1 NA / 2 EU) 등이다.

총 71편이 제출되어 21편의 논문이 선정되었다(채택율: 29.6%). 지역별로는 극동(11편), 북미(6편), 유럽(4편) 순이다.

제출된 71편의 논문 중 50%는 DCDC Converter 기술에 관한 것이다.

_ Inductive switching과 capacitive switching을 조합한 hybrid switching converter가 많이 연구됐으며 Passive 소자들을 fully integration한 on-chip resonant switchedcapacitor converter의 효율 및 용량향상 기법이 소개되었다.

_ Conversion ratio가 높은 출력에서 DC-DC converter 효율을 향상시키고자 하는 기법이 많이 제안되었다.

_ GaN converter 및 Isolated Power Converter 논문 증가. 전통적인 high power 기술들이 IC level에 적용되고 있다.

_ Energy Harvester 및 WPT 논문채택율이 감소하고 있다. Energy harvesting 및 WPT 논문 제출수는 21편이었지만, 3편만 채택되어 새로운 아이디어 고갈이 우려된다.

주요 논문들

[11.2] A Fully Integrated Resonant Switched-Capacitor Converter with 85.5% Efficiency at 0.47W UsingOn-Chip Dual-Phase Merged-LC Resonator.

_ Dartmouth College, Hanover, NH, US.

_ 최근 전원 관리 분과의 가장 관심받는 기술은 큰 면적을 차지하는 외장 수동 부품을 제거할 수 있는 fully integrated DC-DC 변환 기법이다.

_ Planar spiral inductor와 flying capacitor를 병합 설계하여, off-chip passive component가 전혀 사용 되지 않은 fully integratedon-chip DC-DC converter를 개발하였다.

[18.5] ZVS Flyback Converter ICs Optimizing USB Power Delivery for Fast Charging Mobile Devices to Achieve 93.5% Efficiency

_ Richtek, Hsinchu, Taiwan

_ USB Type-C 전력 전송을 최적화할 수 있는 zero voltage switching Flyback converter를 새롭게 제안하고 설계하였다.

_ MCU, ADC, flyback converter, 보상기 및 제어기를 포함한 full system level 설계를 통해 기술의 완성도를 높였다.

데이터 컨버터 분과

데이터 컨버터(Data Converters) 기술 분과는 총2개 세션에서 15편의 논문이 발표된다(총 제출 논문수: 45편).

이 분과의 논문은 극동지역(9편)이 강세를 보였으며 다음으로 북미(5편), 유럽(1편) 순이었으며 학계(10편), 산업계(5편) 순으로 나타내었다.

[Session 9] Noise-Shaping ADCs

_ 최근 Noise-shaping ADC가 강한 트렌드를 나타내고 있다.

_ 11~17bits, 2kHz~40Mhz BW의 noise-shaping and deltasigma ADC.

_ Cascaded noise-shaping, closed-loop dynamic amp, 세련된 mismatch error shaping 기법, 고해상도를 위한 on-chip digital calibration 소개됨.

[Session 16] Nyquist and VCOBased ADCs

_ 속도와 해상도를 증가시키는 것은 여전히 Nyquist ADC의 주요 트렌드임.

_ Time-interleaving, on-chip calibration로 강화된 Pipeline ADC 소개

_ Noise-cancellation SAR에 적용, non-uniform sampling이 소개됨.

Session 9 주요 논문들

[9.1] “A current-sensing frontend realized by a continuoustime incremental ADC with 12b SAR quantizer and reset-then-open resistive DAC achieving 140dB DR and 8ppm INL at 4kS/s” (MediaTek)

_ MediaTek에서 기존 고해상도 ADC보다 광대역을 55nm 공정으로 구현한 current-sensing front-end를 소개한다.

_ 12bit SAR 비교기와 새로운 DAC switching 기법을 이용하여 continuous-time incremental ADC로 4KS/s와 1mW 전력소모로 140dB 동작범위 구현.

[9.5] “A 13.5b-ENOB secondorder noise-shaping SAR with PVTrobust closed-loop dynamic amplifier”(University of Texas, Austin)

_ UT Austin에서 PVT에 강한 closed-loop dynamic amp를 활용하여 noise-shaping SAR ADC를 40nm 공정으로 구현.

_ 2차 noise-shaping ADC로 -10℃ to 80℃ 온도범위와 ±12% 전원 변화에 대해 0.2bit 저하만 갖는 13.6bit 성능을 측정.

Session 16 Highlights

[16.1] “A 12b 18GS/s RF Sampling ADC with an integrated wideband track-and-hold amplifier and background calibration” (Analog Devices)

_ Analog Devices에서 on-chip digital 보상을 적용한 9GHz 대역폭과 50dB 이상 선형성을 갖는 ADC 소개.

_ 제안한 ADC는 8 GHz 신호를 18GS/s의 속도와 1.3W 전력소모로 48dB SNDR과 54dB SFDR 성능 측정됨.

[16.5] “A 13b 0.005mm2 40MS/s SAR ADC with kT / C noise cancellation” (Tsinghua University)

_ 청화대에서 13bit 40MS/s SAR ADC를 40nm 공정으로 구현.

_ 새로운 Sampling 기법으로 노이즈를 줄여 240fF의 입력 커패시턴스만을 갖고, 40 MS / s 와 0.59mW 전력 소모로 69dB SNDR 성능 달성.

무선 분과

무선 기술 분과에서는 3개의 세션에서 총 24편의 논문이 발표되었다.

극동 지역에서는 8편이 발표되었고(한국 2), 그 다음으로 북미(12편), 유럽(4편) 순으로 논문이 나왔다.

무선 분과 세션은 △Session4: mmwave Wireless for Communi cation & Radar(FE: 2 / NA: 6 / EU: 0) △Session 10: High Performance Transceivers (FE: 3/ NA: 4 / EU: 1) △Session30: Efficient Wireless Connectivity(FE: 3/ NA: 2 / EU: 3) 등이다.

주요 논문들

mm-wave Wireless for Communication & Radar

최근 레이더, 빔포밍 시스템, mm-wave IC 등은 자율주행, 5G 등 자주 화두가 되고 있는 토픽이다. Session 4는 광대역 통신을 위한 새로운 기반 기술에 관한 논문들이 발표될 예정이다.

[4.1] A39 GHz Band CMOS 16-Channel Phased-Array Transceiver IC with a Companion Dual-Stream IF transceiver IC for

_ 5G NR Base-Station Applications [Samsung Electronics, Korea]

5G NR 기지국용 세계 최초의 상용화 39GHz 대역 CMOS RF phase-array transceiver IC

_ 28nm Bulk CMOS 공정을 이용한 16채널 RF phased-array 기반 트랜시버와 65nm Bulk CMOS 공정을 이용한 IF 트랜시버로 구성

High Performance Transceivers

5G-NR 및 802.11ax 표준은 MIMO/Spatial diversity를 위해 큰신호 대역폭, 다중 반송파 생성 등의 어려운 문제 해결을 요구한다. 이 세션에서는 기록적인 데이터 속도와 최고 수준의 트랜시버 통합에 관한 논문을 발표한다.

[10.3] A 12 nm CMOS RF Transceiver supporting 4G/5G UL MIMO [MediaTek, Taiwan]

_ 2/3/4/5G를 모두 커버하는 12nm FinFET CMOS로 설계된 트랜시버를 발표한다.

이 Multi-mode, multi-band 셀룰러 트랜시버는 6-carrier aggregation downlink와 2-carrier aggregation uplink로 구성된다. 4x4 MIMO256-QAM 통신을위하여 새로운 LO phase-synchronization를 처음으로 시연한다.

Efficient Wireless Connectivity

Wireless connectivity는 다양한 사물 인터넷(IoT) 응용 프로그램의 핵심 요소이다. 이 세션에서는 27.6nW 초저전력 Wake-up 수신기에, 장거리 IoT 연결을 위한 고집적 NB-IOT(Narrowband-IOT) 트랜시버 SoC 등을 발표한다.

[30.2] NB-IoT and GNSS All-in-One System-on-Chip integrating RF Transceiver, 23dBm CMOS Power Amplifier, Power Management Unit, and Clock Management System for Low Cost Solution [Samsung Electronics, Korea]

_ 이 논문은 NB-IoT과 GNSS(위성통신) 시스템을 하나의 칩에 동시에 집적한 RF 트랜시버를 발표한다.

[30.5] A 0.5V BLE Transceiver with a 1.9mW RX Achievin -96.4dBm Sensitivity and 4.1dB Adjacent Channel Rejection at 1MHz offset in 22nm FD-SOI [Sony Semiconductor Solutions, Japan]

_ 이 논문은 0.5V의 저전압에서 동작하며 1.9mW만의 전력을 소모하는 Digital PLL, SAR-ADC로 구성된 BLE 트랜시버를 발표한다.

RF 분과

RF 기술 분과는 고주파, 고속 동작 반도체 시스템의 핵심회로 기술 등이 소개된다.

이번 컨퍼런스에서는 3개의 세션 총24편의 논문이 발표된다. 극동 지역에서 8편의 논문이 나왔고(한국 4편) 이어서 북미(8편), 유럽(8편) 순으로 논문을 냈다.

주요 키워드는 5G, THz이며 지난해 최다 인원이 참석할 정도로 관심도가 높다.

주요 세션은 △세션17: Frequency Synthesizers & VCOs (FE5 / NA0 / EU4) △ 세션24: RF & mm-WavePowerAmplifiers (FE 2/ NA5/EU1) △세션29: Emerging RF & THz Techniques(FE1/ NA4/ EU3) 등이다.

Session 17 요약

Frequency Synthesizers & VCOs

_ 5G 통신 및 초광대역 통신 시스템에 사용되는 초저잡음의 반송주파수 및 클락 주파수 신호를 생성하는 주파수 합성기 구조들이 소개된다.

_ 반도체 시스템의 집적도를 높이기 위하여 Passive 소자의 사용을 배제한 Ring-VCO 기반All-Digital PLL들이 주목.

[17.3] A-58dBc-Worst Fractional Spur and-234dB-FOMJIT, 5.5GHz-Ring-DCO-Based Fractional-NDPLL Using a Time-Invariant-Probability Modulator, Generating a Nonlinearity-Robust DTC-Control Word(KAIST, Daejeon, Korea)

고성능 반도체 시스템에 클락 신호를 제공하기 위해서 집적도가 떨어지는 인덕터를 사용하여고주파 신호를 생성하는 방식이 사용되어 왔는데, 필연적으로 실리콘 면적의 증가를 가져왔다. 이 논문은 신호 처리기법을 이용하는 새로운 설계 방법을 도입해서 인덕터의 사용없이 저잡음, 고분해능의 고주파 신호를 생성하는 연구를 소개한다.

Session 24

Power Amplifiers

_ 안테나에 높은 출력을 공급하면서도 높은 수준의 전력 효율성을 유지하는 밀리미터 대역 Power Amplifier는 5G 기술 고도화를 위한 핵심 기술이다.

_ 상기 목표를 위하여, 밀리미터 대역 Doherty PA가 대세 구조로 발표된다. 또한, PA와 안테나를 하나의 모듈로 개발하는 것이 새로운 추세가 되고 있다.

[24.5] A 15-bit Quadrature Digital Power Amplifier with Transformer-Based Complex-Domain Power Efficiency

Enhancement

_ Fudan University, Shanghai, China

_ 15Bit의 분해능을 가질 수 있는 디지털 PA구현. 23.6dBM의 평균 출력 전력에서 24.4% 효율을 달성.

Emerging RF & THz Techniques_비교적 저주파수 부근의 주파수의 사용이 포화되면서 더높은 주파수 대역의 활용이 주목받고 있다. 300GHz 이상의 Sub-THz 주파수를 이용하여 imager, sensor, 초광대역 통신 시스템 등을 만드는 기술이 소개된다.

[26.1] A 490GHz,-101.3dBm,

32 mW Fully Integrated CMOS Imager Adopting Dual-Locking Receiver-Based FLL(KAIST, Daejeon, Korea)

_ 490GHz 대역의 RF 트랜시버를 실리콘에 완전히 집적한 imager를 발표한다.

_ 고주파동작에서 전력 소모가 큰 frequency divider, VCO 등의 사용을 배제하고 injection-lockingbased 주파수 교정기를 사용하여 전력소모를 최소화하였다.

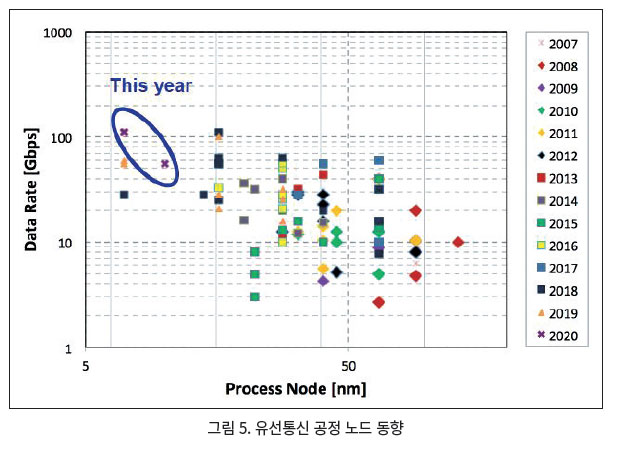

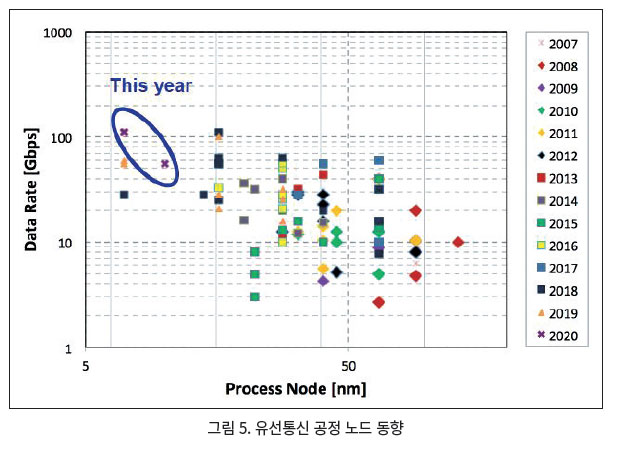

Wireline 분과

유선 통신(Wireline Communications)는 2세션에서 최신 기술을 발표한다.

이 분과에서는 △Session 6:Ultra High-Speed Wireline (4 FE /4 NA / 0 EU) △Session 12:Advanced Optical Communication Circuits(1 FE / 1 NA / 2 EU) 등이다.

12개의 논문이 채택(채택률 36%)되었고 북미가 5편, 극동아시아가 5편, 유럽이 2편이다. 8개의 긴 논문과 4개의 짧은 논문으로 구성되었다. 극동에서는 한국 논문 3편(서울대 2편, 삼성전자1편), 대만 논문1편, 일본 논문1편이 채택되었다.

기술동향

긴구리선용 DAC/ADC 기반초고속 PAM-4 송수신기와 3D Integrated silicon photonics PAM-4 송수신기, 광통신용 부품 등이 주목받았다.

Session 6:초고속 유선

[6.1] A 112Gb/s PAM-4 Long-Reach Wireline Transceiver Using a 36-Way Time-Interleaved SAR-ADC and Inverter-Based RX Analog Front-End in 7nm FinFET, (Xilinx, CA) 36-way time-interleaved 56Gb/s 7b ADC를 이용한 PAM-4 송수신기가 long-reach copper interconnects에서 112Gb/s를 달성.

[6.2] A 460mW 112Gbps DSPBased Transceiver with 38dB Loss Compensation for Next Generation Data Centers in 7 nm FinFET technology (MediaTech, CA)

4-lane 112 Gb/s DAC/ADC 기반 송수신기가 112Gb/s에서 동작하고 DSP를 제외했을 때 단지 5pJ/b 이하의 전력소모를 기록함.

[6.5] A 6.4-to-32Gb/s 0.96pJ/b Referenceless CDR Employing ML-Inspired Stochastic Phase-Frequency Detection Technique in 40nm CMOS (Seoul National University, Korea)

제안된 CDR은 harmonic locking을 피하면서 unlimited frequency detection capability와 함께 11μs의 매우 빠른 lock time을 달성하였으며, 32Gb/s에서 0.96pJ/b의 매우 낮은 에너지를 소모함.

Session 12:AdvancedOptical Communication Circuits

[12.1] A 3D-Integrated Microring based 112 Gb/s PAM4 Silicon Photonic Transmitter with Integrated Nonlinear Equalization and Thermal Control (Intel, OR)

제안된 광송신기는 sub-GHz의 detuning resolution을 가지는 thermal control 회로를 이용하여 55℃까지 0.5dB 이하의 power penalty를 보이며 동작하였으며, laser 전력을 포함하여 7.5pJ/bit의 에너지 효율을 달성.

[12.2] A 4-Channel 200Gb/s PAM4 BiCMOS Transceiver with Silicon Photonics Front-Ends for Gigabit Ethernet Applications (Catania, Italy)

제안된 송수신기는 채널당 850mW를 소모하면서 BER 2E-4 에서 -9.5dBm의 optical input sensitivity와 송신기 출력단에서 6dB의 extinction ratio를 달성.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)

.jpg)

.jpg)