[전자과학 전동엽 기자] 5nm 이하 반도체 초미세 공정을 위한 첨단 기술이 제조공정에 투입되면서 첨단 공법 및 재료에 대한 관심이 높아지고 있다.

반도체 미세 공정에 따른 첨단 기술은 크게 트랜지스터 구조, 재료, EUV에 관한 것이 핵심이다. FinFET 구조의 한계가 다가옴에 따라, 5nm 이하 공정에 적용할 수 있는 새로운 트랜지스터 구조나 메탈레이어의 두께 감소를 위한 새로운 재료, 패턴 형성을 위한 EUV(Extream Ultraviolet, 극자외선) 패터닝 기술의 도전과제 해결이 그 대상이다.

3대 쟁점 "트랜지스터 구조, 반도체 재료, EUV 효율"

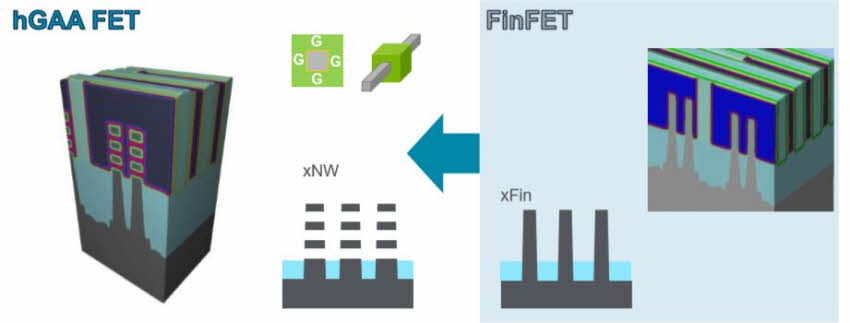

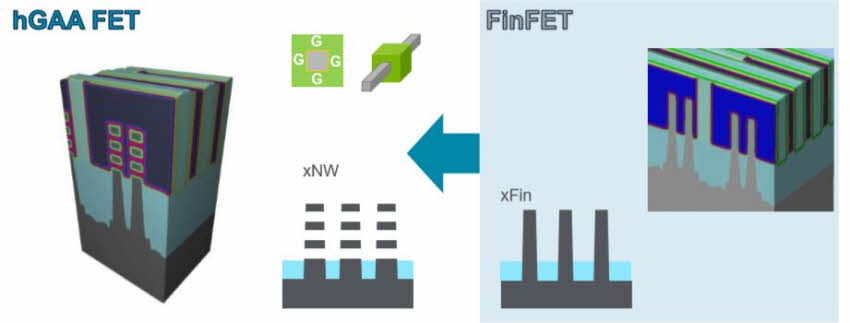

현재 널리 쓰이고 있는 FinFET 구조는 트랜지스터 구조를 평면에서 3차원으로 바꿔 평면에서 3면으로 사용면적을 넓힌 것이다. 트랜지스터는 게이트에 전압을 넣으면 게이트와 채널이 닿는 면적이 넓어질수록 성능이 좋아지기 때문이다.

삼성전자가 지난해 3나노 공정에 도입하겠다고 공개한 GAA(Gate-All-Around)는 트랜지스터 게이트가 채널 4개면 모두에 배치되는 기술이다. 삼성은 3나노 GAA 공정에서 1세대를 Early, 이후 성능과 전력이 개선된 2세대를 Plus(3 GAP)라고 부르고 있다. 삼성전자는 3나노 공정에서 독자적인 MBCFET(Multi Bridge Channel FET) 기술을 적용한다.

MBCFET은 기존의 가늘고 긴 와이어 형태의 GAA 구조를 한층 더 발전시켜 종이처럼 얇고 긴 모양의 나노시트를 적층하는 방식이다. 성능과 전력효율을 높이는 것은 물론 핀펫 공정과도 호환성이 높아 기존 설비와 제조 기술을 활용할 수 있다는 장점을 가지고 있다고 회사 측은 설명했다.

최근, 국제반도체장비재료협회(SEMI)가 개최한 반도체 전자재료 컨퍼런스 ‘SMC 코리아 2019’에 발표자로 나선 어플라이드 머티어리얼즈(Applied Meterials)의 나오미 요시다 디렉터(Distinguished MTS)도 5nm와 그 이하의 공정을 만족시킬 수 있는 새로운 구조와 재료의 중요성을 역설했다.

나오미 디렉터는 5nm 노드 이상으로 CMOS 스케일링을 가능하게 하는 새로운 트랜지스터 구조로 hGAA(Horizontal-Gate All Around) FET을 제시했고, Thickness Scaling을 위한 물질로 코발트(Co)를 소개했다. 이어 hGAA(Horizontal-Gate All Around) FET을 진화적 변화(Evolutional Change)라고 표현하며 5nm 이하의 공정을 실현하기 위해서는 hGAA FET이 핵심이라고 강조했다.

hGAA FET(좌)과 FinFET(우) 구조 비교

“hGAA FET은 FinFET과 유사한 구조와 흐름을 가지고 있다. 그러나 hGAA는 FinFET과 달리 고품질의 실리콘 나노와이어 적층 공정을 통해 원형의 게이트를 쌓아올려 게이트의 모든 면을 채널과 만나게 한다. 게이트와 채널이 닿는 면적이 더 넓어 고집적, 고성능 반도체 설계가 가능하게 될 것이다.”

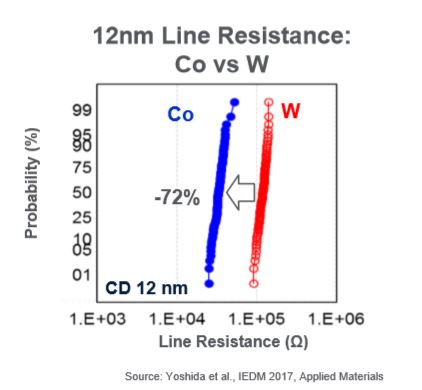

메탈 레이어의 두께 감소를 위한 새로운 재료가 필요하다는 점도 제기됐다. 기존 반도체 재료는 주로 텅스텐(W), 구리(Cu), 알루미늄(Al) 등이 많이 사용됐지만, 코발트(Co)는 텅스텐에 비해 전도성이 높고 장벽 두께를 줄일 수 있다는 것.

코발트(Co)와 텅스텐(W) 12nm 라인 저항값 비교

나오미 디렉터는 “5nm 이하 공정을 구현하는데 있어 메탈 레이어의 두께감소가 굉장히 중요하다. 층 두께의 감소는 새로운 재료의 고려없이는 조정이 불가능하다. 코발트를 하나의 예로 들었지만 새로운 재료의 등장이 필수적이다. 공급사와 재료사가 협력하면서 시스템의 변화를 이끌어야한다”라고 말하며 새로운 재료의 필요성을 강조했다.

같은 행사에 참가한 IMEC의 프레드릭 라자리노 R&D 매니저는 EUV(Extream Ultraviolet, 극자외선) 패터닝 기술이 가진 도전과제에 대한 해결방안을 제시했다.

SIS 기법으로 EUV공정의 효율을 높여야

집적률을 높이기 위해서는 패턴의 선 폭이 좁아져야 하는데 기존에 광원의 파장 길이가 가장 작았던 불화아르곤(ArF)으로는 10nm 공정까지가 한계로 지적되면서, 부각된 기술이 EUV 노광공정이다. 프레드릭 매니저는 “현재 게이트 피치의 스케일링 속도는 점점 느려지고 있는 반면, 메탈 피치 스케일링은 여전히 공격적으로 진행되고 있다. EUV에 있어서 기회가 있을 수 있다.”고 전했다. 그는 거칠기(roughness)와 파선, 병합, 접촉누락과 같은 확률적 인쇄실패 문제를 가진 EUV공정을 위해서는 SIS(Sequential infiltration synthesis) 기법으로 완화할 필요가 있다고 말했다.

SIS는 EUV 감광제에 무기원소를 침투시켜 강도를 강화하고 패터닝 효율을 향상시키는 원자층 증착기술이다. SIS를 TiN(질화티타늄)층에 적용시켜 LCDU(Local Critical Dimention Uniformity, 패턴 임계치수 균일도)가 향상됐고, 기존 공정대비 거칠기가 20% 향상됐다.

지난해 10월 삼성전자는 EUV 기반 7nm 공정 생산을 개시했고, 올해 4월에 성공적으로 5nm EUV 개발을 완료해 면적확장 및 초저전력 이점을 얻었다. TSMC는 올 3월부터 ArF기반으로 해오던 7nm 공정을 EUV로 전환해 양산체제를 구축했다. 그리고 5nm노드는 리스크 생산을 이미 시작했으며 2020년 초 대량 생산할 계획이다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)