글 | 아론 버만(Aaron Behman), 아담 테일러(Adam Taylor), 자일링스

임베디드 비전(EV: Embedded Vision) 시스템은 의료 이미징 및 증강현실은 물론, ADAS에서 머신 비전에 이르기까지 여러 다양한 애플리케이션에 사용되고 있다.

EV 시스템을 탑재함으로써 최종 애플리케이션에 상당한 이점을 제공할 수 있지만, 이와 더불어 개발자는 이러한 시스템 탑재로 인해 생명의 위협을 초래하거나 부상 또는 자산 손상이 발생하지 않도록 보장할 수 있어야 한다. 이를 달성하기 위해서는 엔지니어링 라이프 사이클 및 합의된 표준에 따른 설계의 안전성뿐만 아니라, 악의적으로 또는 다른 어떠한 방식으로도 EV 시스템을 수정하지 못하도록 방지할 수 있는 보안 이슈를 고려해야 한다.

EV 시스템의 최종 애플리케이션은 안전 및 보안 요건이 강화될 것이다. 예를 들어, 컨수머 애플리케이션은 ADAS(Advanced Driver Assistance Systems)나 머신 비전 시스템보다 훨씬 적은 요건이 적용될 것이다.

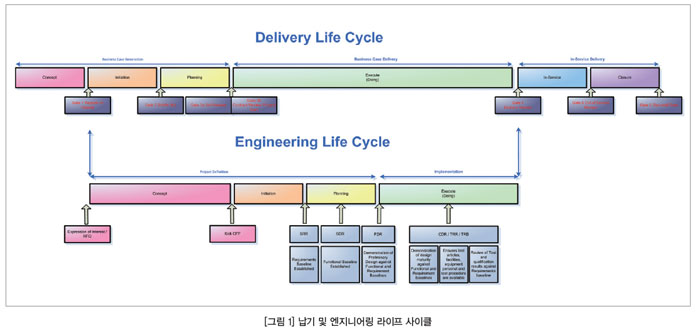

이러한 설계 고려사항과 안전 및 보안 요건을 지원하기 위해 기능 안전을 요구하는 많은 전자 시스템의 우산 역할을 하는 IEC61508과 같은 여러 잘 알려진 국제 표준들이 있다. 또한 자동차 애플리케이션을 위한 ISO26262를 비롯해 기계 분야의 IEC62061, 비행 애플리케이션용 DO178/DO254 등 애플리케이션 별로 특화된 다양한 표준들이 존재한다. 이와 더불어 상업용 애플리케이션은 최종 마켓에 따라 CE, UL, CSA와 같은 마크도 획득해야 한다. 이러한 각 표준은 구현 조직의 엔지니어링은 물론, 납기 라이프 사이클에 걸쳐 준수될 수 있도록 개발 및 검증 요건을 제시하고 있다.

EV 시스템의 핵심은 프로세싱 코어이지만, 시스템은 일반적으로 지금까지 제기된 여러 측면들을 해결할 수 있는 FPGA나 프로그래머블 SoC를 포함하게 될 것이다.

이러한 표준이 실제로 의미하는 것은 무엇인가?

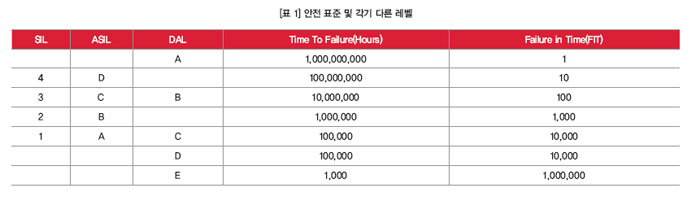

이러한 안전 표준의 대부분은 IEC61508의 SIL(Safety Integrity Level)이나 DO254의 DAL(Design Assurance Level), ISO26262의 ASIL(Automotive SIL)과 같이 다양한 이름의 안전 레벨을 정의하고 있다. 또한 SIL, DAL, ASIL에는 애플리케이션의 중요도에 따라 애플리케이션에 적용할 수 있도록 여러 각기 다른 레벨을 포함하고 있다. 일반적으로 이러한 레벨은 실패 시간 수로 정의되거나 또는 실패하기까지의 시간으로 정확하게 지정된다. 일반적으로 서로 다른 표준들로 조정이 되기는 하지만, 〈표 1〉에 나타낸 것처럼 약간의 차이가 있다.

설계 분석을 수행하면, 인증에 필요한 레벨이 어떻게 달성되는지 확인할 수 있는데, 엔지니어들은 실패시간(Time to Failure)의 역수인 FIT(Failure in Time) 레이트로 작업하는 경향이 있다. SIL 4 및 DAL A 레벨로 작업하는 경우, 이러한 요건을 달성하기 위해서는 올바르게 구조화된 시스템이 필요하다.

체계적인 고려사항

안전 시스템을 개발하려면 각 개발 단계에서 명확하게 정의된, 추적 가능한 요건을 갖춘 탁월한 시스템 엔지니어링 실무능력이 필요하다.

앞서 살펴본 것처럼 엔지니어링 라이프 사이클은 최종 애플리케이션 및 이와 관련된 인증 요구사항에 따라 결정된다. 이 라이프 사이클은 EV 시스템의 콘셉트에서 생산, 그리고 폐기에 이르기까지의 전반적인 엔지니어링 접근방식을 정의하게 된다.

이 라이프 사이클 내에서 프로젝트의 진행을 제어하는 엔지니어링 리뷰 게이트를 정의할 수 있다. 이러한 검토 과정에서 독립적인 기술 전문가들은 디자인 완성도가 다음 단계로 나아갈 수 있는지 또는 적절한 표준 입증을 달성하기 위해 추가 작업을 수행해야 하는지 확인하기 위해 요건 및 설계, 기술 보고서, 테스트 결과 등을 검사한다.

또한 엔지니어링 플랜에서는 적용 가능한 표준 준수여부에 대한 일련의 증거자료를 얻기 위해 수행되는 모든 레벨에서의 검증 및 유효성 검사 프로세스에 대한 개요를 제시해야 한다. 이를 위해서는 환경적인 동작 범위와 역동적인 진동 및 충격에 대한 EV 시스템의 테스트가 필요할 수도 있다. 또한 시스템의 동작 수명이 달성됐는지 확인하기 위해 EV 시스템의 가속 수명 테스트를 수행해야 할 수도 있다.

보안 문제의 경우, 엔지니어들이 설계의 안전성과 관련하여 직면하고 있는 하이-레벨 이슈들을 비롯한 여러 측면들을 고려해야 한다. 여기에는 다음과 같은 것들이 포함된다.

ㆍ 설계에 대한 경쟁사의 리버스 엔지니어링

ㆍ 설계의 무단 변경

ㆍ 설계 내 데이터에 대한 무단 액세스

ㆍ 최종 애플리케이션 무단 제어 및 조작

이러한 문제들 가운데 일부는 해결할 수 있는 여러 가지 방법이 있다. 암호화된 비트 스트림을 사용해 설계 및 제조 파일에 대한 액세스를 제어할 수 있으며, 또는 최종 제품의 JTAG 포트에 대한 액세스를 제한하거나 선택된 디바이스의 아키텍처에 따라 소프트웨어 보안조치를 구현함으로써 물리적 디자인을 보호할 수 있다.

품질을 고려한 설계

당연한 말이지만, 최종 애플리케이션에 따라 애플리케이션 품질 요건을 준수할 수 있는 컴포넌트 및 제조 표준을 선택해야 한다. 프로세싱 코어의 경우, 표준 상업용 품질 표준에서 산업 및 자동차, 우주항공, 방위산업과 같은 보다 까다로운 표준에 이르기까지 자일링스(Xilinx)의 FPGA나 SoC 디바이스를 사용할 수 있다. 이를 통해 엔지니어링 팀은 올바른 컴포넌트 등급을 선택함으로써 처음부터 품질을 향상시킬 수 있다.

또한 이러한 표준들의 엄격한 요건을 달성하는데 사용할 수 있는 다양한 설계 기법들도 있다. 신뢰성 요건(성공 확률이라고도 함)을 충족시킬 수 있도록 신뢰성 엔지니어링 기법을 이용해 필요 시 시스템 내의 기능에 대한 신뢰성 블록 다이어그램을 만들거나 위험한 장애 모드나 단일 실패지점을 제거할 수 있다. 또한 설계 자체 내에서 FMECA(Failure Mode Effect Criticality Analysis)를 수행할 수 있는데, 수행되는 레벨은 기능 블록에서 컴포넌트 레벨까지 애플리케이션에 따라 다양하다.

FMECA는 잠재적인 실패 모드를 비롯해 시스템에 대한 다음 효과 및 최종 효과를 고려하게 되며, 결함이 자체-테스트나 시스템 모니터링으로 인해 감지될 수 있는지도 고려한다. 컴포넌트 레벨의 FMECA를 개발하려는 경우, 디자인 내의 각 컴포넌트에 대한 PSA(Part Stress Analysis)를 고려해 정확한 부하경감 상태로 동작하는지 확인할 수 있다. 적용된 부하경감 레벨은 일반적으로 사용되는 선택된 표준에 따라 다르다.

표준은 국방부((Mil-STD 1547)와 유럽 우주기구(ESCC-Q-30-11A)가 포함되어 있다. PSA를 수행하지 않는다면, 스트레스를 받는 디바이스를 사용하게 될 수 있으며, 이로 인해 이러한 디바이스는 장비의 수명 제한 요인이 될 수 있다. FMECA 예측에 따라 시스템의 손실 또는 성능 저하를 일으키는 결함이 발생할 수도, 그렇지 않을 수도 있다.

신뢰성 문제와 더불어, 이용사례에 따른 시스템에 대한 위협 및 식별된 위협에 대한 잠재적인 완화 전략을 결정하는 시스템 위협 분석을 실행할 수도 있다.

아키텍처 케이스 스터디

하드웨어 레벨에서는 시스템의 기능과 기능적 안전 및 보안을 구현할 수 있는 방법을 고려해야 한다. 이는 처음부터 모두 구현할 수도 있지만, 이미 이러한 기능을 지원하는 즉, 자일링스의 징크(Zynq?) 올 프로그래머블(All Programmable) SoC와 같은 컴포넌트를 선택하는 것이 훨씬 유리하다.

모든 EV 시스템의 핵심은 이미지 프로세싱 파이프라인이다. 이를 위해 감시 및 제어 능력을 겸비한 고대역폭 프로세싱 기능이 필요하다. 징크 AP SoC를 이용하면, 기존의 프로세서 및 FPGA 조합과는 달리 긴밀하게 통합된 아키텍처를 구현할 수 있다.

프로세서와 로직 패브릭 간의 긴밀한 통합으로 더욱 뛰어난 SAWP-C 솔루션을 구현할 수 있을 뿐만 아니라 두 제품 간의 상호 작용에 대해 외부의 악의적이거나 혹은 다른 액세스 시도가 불가능하기 때문에 보다 안전한 시스템을 제공할 수 있다.

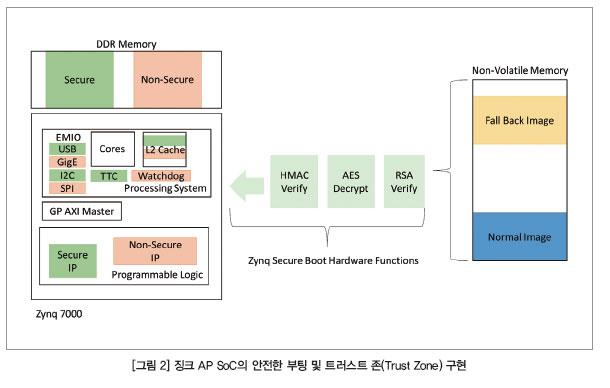

전자 아키텍처 내에 징크 AP SoC의 임베디드 보안 아키텍처를 사용해 보안 설정을 제공할 수 있다. PS(Processing System)와 PL(Programmable Logic) 모두 시스템 파티셔닝이 안전한지 확인하는데 사용할 수 있는 3단계 프로세스가 있다. 이는 HMAC(Hashed Message Authentication Code)와 AES(Advanced Encryption Standard) 암호화 해독, 그리고 RSA 인증이다. AES와 HMAC은 모두 256 bit 개인키를 사용하는 반면, RSA는 2,048 bit 키를 사용하며, 징크 AP SoC의 보안 아키텍처는 JTAG 액세스가 활성화 또는 비활성화될 수 있도록 한다.

이러한 보안 기능은 부팅 파일과 비휘발성 부팅 매체를 위한 구성 파티셔닝을 생성할 때 사용할 수 있다. 또한 초기 첫 단계 부트 로더가 해당 애플리케이션을 로드하는데 실패하면, 다른 메모리 위치에 저장된 또 다른 애플리케이션 사본으로 폴 백(Fall Back)하도록 폴 백 파티셔닝을 정의할 수도 있다.

디바이스가 성공적으로 작동되면, ARM 트러스트 존(Trust Zone) 아키텍처를 사용해 PL 주변장치를 포함한 징크 AP SoC 내의 하드웨어 기능에 대한 액세스를 제한하는 직교 영역을 구현할 수 있다. 또한 메모리와 L2 캐시를 세그먼트화해 제한된 상호작용을 제한하는 보안 또는 비보안 영역을 유지할 수 있다.

Zynq AP SoC PL 패브릭 내에서 이미지 프로세싱 파이프라인을 구현하는 경우, 트러스트 존을 사용해 프로그래머블 로직 패브릭 내의 IP 코어에 대한 보안 또는 비보안 액세스를 제공할 수도 있다. 이를 통해 이미지 프로세싱 체인의 중요한 부분에 보안 액세스를 사용하여 구성에 대한 비승인된 변경을 방지할 수 있다.

이미지 프로세싱 파이프라인은 사용자가 개발한 모듈이나 IP 라이브러리의 모듈을 이용해 구현이 가능하다.

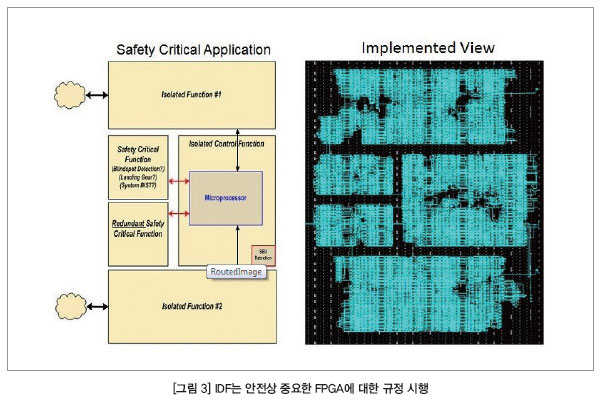

일부 안전 및 보안 구현(예: IEC61508)은 디자인 요소들을 서로 절연시킬 것을 요구하기도 하는데, 이는 모듈 중복성이나 다른 안전 영역, 테스트 기능 때문이기도 하다. IDF(Isolation Design Flow)를 이용해 식별된 영역들을 물리적으로 분리시킬 수도 있다.

IDF는 프로세싱 체인 또는 다른 제어 로직 내에 다수결 투표(Majority Voting)를 구현하고자 하는 경우 매우 유용할 수 있다. 이를 사용하면 중복 모듈 간의 유일한 상호 연결을 신뢰할 수 있는 경로를 통해 이뤄지도록 할 수 있다.

설계를 구현하는 경우, 사용할 수 있는 다양한 디바이스나 툴 별로 특화된 구현 고려사항들이 있다. 물론 최종 애플리케이션과 전반적인 엔지니어링 관리 계획에는 이러한 기법의 구현 필요성이 설명된다.

ㆍ 메모리에 EDAC(Error Detecting and Correcting) 코드를 사용한다. 필요할 경우, 애플리케이션이 메모리에 액세스하는지 여부와 상관없이 주기적으로 메모리의 데이터를 읽고 수정하는 스크러빙(Scrubbing) 기능과 결합할 수 있다.

ㆍ 제어 단어를 정의할 때 해밍(Hamming) 차이를 활용하고 명령어 간의 해밍 거리를 늘리면, 구현 시 더 많은 비트가 요구되므로 디자인 안정성에 도움이 될 수 있다.

ㆍ 중요한 명령의 경우, 중요한 기능을 수행하는 두 개의 별도 명령이 요구되는 ARM 및 FIRE 방식을 사용한다.

ㆍ 외부 통신 인터페이스에서 EDAC 코드를 사용한다.

ㆍ 시스템의 상태 또는 이를 보고할 수 있는 포괄적인 BIT(Built in Test) 기능. 징크 XADC는 먹스를 통해 외부 신호의 도입과 디바이스의 전압 및 온도를 모니터링할 수 있는 BIT 시스템의 매우 유용한 요소다.

결론

기능 안전을 위한 올바른 산업 표준을 달성함으로써 임베디드 비전 시스템을 성공적으로 구현할 수 있다. 또한 여기에는 시스템 개발자들이 사용할 수 있는 다양한 컴포넌트와 툴, 개발 방법론들이 있다.

EV 시스템에 대한 인증을 획득하기 위해서는 인증 달성에 필요한 증거를 수집하는데 사용되는 엔지니어링 라이프 사이클을 정의한 엔지니어링 관리 플랜을 생성하고, 올바른 적용 표준을 식별함으로써 처음부터 준비해 나가야 한다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>